一种多路中频与基带高速交换路由的装置及其通信方法与流程

1.本发明涉及一种多路中频与基带高速交换路由的装置及其通信方法,特别是涉及通信技术领域。

背景技术:

2.随着计算机网络技术的发展,在5g网络技术的推进下,为了实现网络的高速接入,天线端将采用大规模天线技术的方式阵列。

3.现有技术中,在网络的高速接入时,单路通用公共无线电接口不能满足射频拉远单元与基带处理单元之间的大数据量的高速的数据传输的需求,且同时具有传输时延,可靠性低,以及可扩展性不高导致实用性不强的缺陷。

技术实现要素:

4.发明目的:一个目的是提出一种多路中频与基带高速交换路由的装置,以解决现有技术存在的上述问题。进一步目的是提出基于装置的通信方法。

5.技术方案:一种多路中频与基带高速交换路由的装置,具体包括:中频板模块、公共无线电接口板卡模块、基带板模块、通信连接模块;所述中频板模块通过通信连接模块与公共无线电接口板卡模块构建数据通信链路;所述公共无线电接口板卡模块通过通信连接模块与中频板模块以及基带板模块构建数据通信链路;所述基带板模块与中频板模块通过公共无线电接口板卡模块与通信连接模块,进行数据的交换传输。

6.在进一步的实施例中,所述通信连接模块进一步包括srio协议链路模块、光纤链路模块;所述srio协议链路模块通过srio链路将中频板模块传输出的数据,发送至公共无线电接口板卡模块中的公共无线电接口板卡;所述光纤链路模块通过光纤的光口将公共无线电接口板卡模块中数据传输至基带板模块。

7.在进一步的实施例中,所述公共无线电接口板卡模块中进行数据通信时,通信数据包中进一步包括cpri业务帧、srio业务帧,其中cpri业务帧业务帧组成cpri组帧模块进一步包含iq映射模块、iq指示信号映射模块和控制模块,所述控制模块中添加了相应的控制信息,降低了数据传输的延时,提高系统的吞吐量。

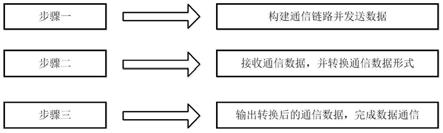

8.一种多路中频与基带高速交换路由的方法,基于所述装置,具体包括以下步骤:步骤一、构建通信链路并发送通信数据;步骤二、接收通信数据,并转换通信息数据形式;步骤三、输出转换后的通信数据,完成数据通信。

9.在进一步的实施例中,所述步骤一进一步为构建用于传输通信数据的通信链路,具体包括中频板与cpri板卡之间的srio链路、cpri板卡与基带板之间的光纤链路。

10.在进一步的实施例中,所述srio链路在中频板到基带板的通信中,用于接收中频板中的通信数据并发送至cpri板卡;在基带板到中频板的通信中,用于将cpri板卡中打包成srio协议帧格式的业务数据,根据业务数据中指定字段确定目的标识符,将srio包发送

到对应的中频板中。

11.在进一步的实施例中,所述光纤链路在中频板与基带板之间的数据通信过程中,通过cpri板卡中的cpri光口与基带板,利用光纤传输通信数据。

12.在进一步的实施例中,所述步骤二进一步为在数据通信过程中,利用cpri板卡中对应协议之间的成帧和解帧,实现中频板与基带板之间通信数据的格式转换;所述格式转换包括srio数据包到cpri光口的映射、cpri数据包到中频板的srio数据包的映射。

13.在进一步的实施例中,所述srio数据包到cpri光口的映射过程,具体为接收中频板通过srio链路传输过来的srio数据包,并通过所述对应协议之间的成帧和解帧,将协议数据格式转换,进一步划分为以下步骤:步骤2.1、cpri板卡将业务数据从srio帧中解析出来,并对错误的数据包进行过滤,记录接收数据包个数;步骤2.2、cpri板卡接收中频板的srio数据包,srio分包器通过检测所述srio数据包的源srio标识符,对所有接收的业务数据包进行分离,并将数据对应写入到对应数量的先进先出数据缓存器中;步骤2.3、cpri板卡对应2个基带板,多端口映射通过检测数据包中指定字段完成端口映射,将所有接收的srio包分别发送到对应的cpri光口上,对srio的业务数据进行校验与过滤;步骤2.4、控制器读取srio分包器存入先进先出缓存器的数据,并将srio数据包缓存一次业务数据;所述控制器为两个上行乒乓控制器,内部均包括一组乒乓先进先出缓存器;步骤2.5、cpri成帧器分别读取上行乒乓先进先出缓存器中的完整业务数据,按照cpri协议进行成帧,同步输出给对应的cpri ip核。

14.在进一步的实施例中,所述cpri数据包到中频板的srio数据包的映射过程,具体为接收基带板通过光纤链路传输过来的cpri数据包,并通过所述对应协议之间的成帧和解帧,将协议数据格式转换,进一步划分为以下步骤:步骤ⅰ、cpri解帧器实时检测cpri ip核的数据,当检测到业务数据传输时,将数据从cpri协议帧格式中解析出来;步骤ⅱ、下行缓存接收cpri解帧器的输出数据,并写入到缓存中供后面链路进行读取使用;步骤ⅲ、控制器读取下行缓存的数据,将数据存入到先进先出缓存器中,控制器输出为一次完整业务数据;所述控制器为两个下行乒乓控制器,内部均包含一组乒乓先进先出缓存器;步骤ⅳ、下行链路同时接收光口传输的数据,多路选择器采用多对一的映射方式,遍历读取下行乒乓控制器的数据;步骤

ⅴ

、srio成帧器将业务数据打包成srio协议帧格式,并根据业务数据中指定字段确定目的srio标识符,将srio包发送到对应的中频板块上。

15.在进一步的实施例中,所述步骤二在通信息数据形式转换时,进一步包括数据包的解析,在srio数据包进行数据传输时,srio业务帧只有一个帧头,包含了帧头识别字符,目标通道号指示当前业务数据应当路由到哪个cpri光口上,目标通道由8字节组成,系统应

用中定义两组信号会对控制交换模块的通道开关;所述两组信号集体为通道号为0的下光口通道,通道号为1的上光口通道;cpri数据包进行数据传输时,cpri的业务帧格式由iq映射、iq指示信号映射和控制模块组成。

16.在进一步的实施例中,所述多端口映射进一步为当srio数据到来时,在一个时钟周期内检测到业务帧头和目标通道号,根据通道号的指向将交换通道打开,并锁定正在传输的数据通路;所述cpri板卡的srio端和cpri端均设计为fifo接口,用于读srio fifo的数据,并写入到cpri fifo中;所述锁定正在传输的数据通路进一步为在传输的数据包中引入占据信号,用于对地址交换模块进行信号连接锁定;所述占据信号表示当前链路正在进行数据交换,用于避免其他链路上的信号与当前链路建立连接。

17.在进一步的实施例中,所述地址交换模块进一步为根据路由表的配置对srio fifo与cpri fifo之间的信号进行连接与释放;所述路由表包含通道协议定义表,根据设定的标识符,实现信号之间的连接与释放,完成数据的读取和输入;所述信号之间的连接与释放进一步采用轮询机制,通过一对多的逐个轮询,进行路由表的更新,完成数据交换映射。

18.在进一步的实施例中,所述轮询机制进一步包括并行轮询机制、均衡轮询机制;所述并行轮询机制包括两个先进先出模块,轮询时同时判断srio fifo是否有数据,是否已被锁定,无数据或被锁定则直接往下轮询,有数据而且未被锁定则判断是否为当前交换端口,轮询后的结果反映在路由寄存器上,当正在通信的链路信号为锁定时,则不再轮询当前的通信链路;所述先进先出模块包括cpri fifo 0轮询模块、cpri fifo 1轮询模块。

19.在进一步的实施例中,所述均衡轮询机制为当处理完一个srio fifo的数据后,查看之后的srio fifo是否有数据,若有数据则强制关闭当前srio fifo的开关,cpri fifo 0的轮询控制模块则可以继续处理下面的数据;若后面的srio fifo都无数据或已被关闭,则打开所有的srio fifo开关,开始第二次轮询。

20.有益效果:本发明提出了一种多路中频与基带高速交换路由的装置及其通信方法,在硬件连接中采用fpga硬连接的方式,实现多个射频拉远单元端口与多个基带处理单元端口之间的数据解析与交换,以及实现动态映射的“并行轮询”和“均衡轮询”,提高系统的可靠性、避免数据拥塞,进一步减少动态映射交换的延时。减少延时,交换速度快,且具有更好的可靠性。本发明支持多个不同数量的射频拉远单元端口的接入,方便扩容和缩容,因此,本发明装置具有低延时、可管理的特点,支持以太网实时监测,实用性强。

附图说明

21.图1为本发明8组中频板与2组基带板的接收链路的实现框图。

22.图2为本发明8组中频板与2组基带板的发送链路的实现框图。

23.图3为本发明公共无线电接口组帧的实现框图。

24.图4为本发明交换控制结构图。

25.图5为本发明srio fifo与cpri fifo之间的信号。

26.图6为本发明路由寄存器的结构图。

27.图7为本发明并行轮询处理的实现框图。

28.图8为本发明均衡轮询处理的实现框图。

29.图9为本发明通信方法流程框图。

具体实施方式

30.本发明通过一种多路中频与基带高速交换路由的装置及其通信方法,实现多路公共无线电接口通过高速光纤连接至交换机,从而实现数据通信的目的。下面通过具体实施例,并结合附图对本方案做进一步具体说明。

31.在本申请中,我们提出一种多路中频与基带高速交换路由的装置及其通信方法中,包含的一种多路中频与基带高速交换路由的装置,具体包括:中频板模块、公共无线电接口板卡模块、基带板模块、通信连接模块。

32.其中,中频板模块通过通信连接模块与公共无线电接口板卡模块构建数据通信链路,公共无线电接口板卡模块通过通信连接模块与中频板模块以及基带板模块构建数据通信链路,基带板模块与中频板模块通过公共无线电接口板卡模块与通信连接模块,进行数据的交换传输。

33.通信连接模块进一步包括srio协议链路模块、光纤链路模块。srio协议链路模块通过srio链路将中频板模块传输出的数据,发送至公共无线电接口板卡模块中的公共无线电接口板卡。光纤链路模块通过光纤的光口将公共无线电接口板卡模块中数据传输至基带板模块。其中,公共无线电接口板卡包括srio ip核、srio解帧器、srio分包器、多路处理器、pingpong控制器、cpri成帧器、cpri ip核。根据通信需求,多路处理器用于多端口映射和多路选择,当中频板与基带板形成接收链路时,多路处理器用于实现多端口映射;当中频板与基带板形成发送链路时,多处理器用于实现多路选择。

34.公共无线电接口板卡模块中进行数据通信时,通信数据包中进一步包括cpri业务帧、srio业务帧,其中cpri业务帧业务帧组成cpri组帧模块进一步包含iq映射模块、iq指示信号映射模块和控制模块。控制模块中添加了相应的控制信息降低了数据传输的延时,提高系统的吞吐量。

35.cpri板卡的srio端和cpri端均设计为fifo接口,用于读srio fifo的数据,并写入到cpri fifo中。

36.由于cpri协议与srio协议数据位宽和速率不匹配,所以公共无线电接口板卡使用乒乓先进先出缓存器,将srio异步数据转换为cpri的同步数据,进行数据缓存和速率匹配,并采用动态映射的“并行轮询”和“均衡轮询”,提高系统的可靠性、避免srio fifo数据拥塞,减少动态映射交换的延时。

37.一种多路中频与基带高速交换路由的通信方法,基于上述装置,具体为八个中频板与两个基带板之间的数据通信,包括以下步骤:步骤一、构建通信链路并发送通信数据;该步骤构建用于传输通信数据的通信链路,具体包括中频板与cpri板卡之间的srio链路、cpri板卡与基带板之间的光纤链路。srio链路在中频板到基带板的通信中,用于接收中频板中的通信数据并发送至cpri板卡;在基带板到中频板的通信中,用于将cpri板卡中打包成srio协议帧格式的业务数据,根据业务数据中指定字段确定目的标识符,将srio包发送到对应的中频板中。光纤链路在中频板与基带板之间的数据通信过程中,通过cpri板卡中的cpri光口与基带板,利用光纤传输通信数据。

38.步骤二、接收通信数据,并转换通信息数据形式;该步骤在数据通信过程中,利用cpri板卡中对应协议之间的成帧和解帧,实现中频板与基带板之间通信数据的格式转换;

所述格式转换包括srio数据包到cpri光口的映射、cpri数据包到中频板的srio数据包的映射。

39.其中,srio数据包到cpri光口的映射过程,具体为接收中频板通过srio链路传输过来的srio数据包,并通过所述对应协议之间的成帧和解帧,将协议数据格式转换,进一步划分为以下步骤:步骤2.1、cpri板卡将业务数据从srio帧中解析出来,根据数据包的校验功能,对错误的数据包进行过滤,记录接收数据包个数。

40.步骤2.2、cpri板卡接收八个中频板的srio数据包,srio分包器通过检测所述srio数据包的源srio标识符,对所有接收的业务数据包进行分离,并将数据对应写入到八个先进先出数据缓存器中;步骤2.3、cpri板卡对应两个基带板,多端口映射通过检测数据包中指定字段完成82端口映射,将所有接收的srio包分别发送到对应的cpri光口上,对srio的业务数据进行校验与过滤,从而保证链路正常。

41.步骤2.4、srio为异步传输方式,而且srio包无法一次传输完整业务数据,所以cpri板卡中采用两个上行乒乓控制器,用于读取srio分包器存入先进先出缓存器的数据,并将srio数据包缓存一次业务数据,从而满足cpri同步传输的方式。其中,两个上行乒乓控制器内部均包括一组乒乓先进先出缓存器。

42.步骤2.5、cpri成帧器分别读取上行乒乓先进先出缓存器中的完整业务数据,按照cpri协议进行成帧,同步输出给对应的cpri ip核。cpri成帧器在cpri板卡中有两个,且分别对应两个cpri ip核。

43.cpri数据包到中频板的srio数据包的映射过程,具体为接收基带板通过光纤链路传输过来的cpri数据包,并通过所述对应协议之间的成帧和解帧,将协议数据格式转换,进一步划分为以下步骤:步骤ⅰ、cpri解帧器实时检测cpri ip核的数据,当检测到业务数据传输时,将数据从cpri协议帧格式中解析出来。

44.步骤ⅱ、下行缓存接收cpri解帧器的输出数据,并写入到缓存中供后面链路进行读取使用,该步骤cpri到srio协议的转换为同步传输到异步输出方式的变换。

45.步骤ⅲ、控制器读取下行缓存的数据,将数据存入到先进先出缓存器中,控制器输出为一次完整业务数据;其中,控制器为两个下行乒乓控制器,内部均包含一组乒乓先进先出缓存器。

46.步骤ⅳ、下行链路同时接收两个光口传输的数据,多路选择器采用21的映射方式,遍历读取两个下行乒乓控制器的数据。

47.步骤

ⅴ

、srio成帧器将业务数据打包成srio协议帧格式,并根据业务数据中指定字段确定目的srio标识符,将srio包发送到对应的中频板块上。

48.在通信息数据形式转换时,进一步包括数据包的解析,在srio数据包进行数据传输时,每一个srio包最多包含256字节数据,中频板一个业务包需要多个srio组成。xilinx提供的cpri光口数据接口位宽是16字节,需要连续将一个业务帧的数据以16字节位宽发送出去,例如x15倍带宽的数据一个时隙内有1440个符号,每一个符号32字节,即1440*32字

节,cpri光口传输时需要对整个业务包进行不间断传输。因此srio到cpri是一个异步传输到同步传输的过程,需要一定空间的缓存保证cpri光口数据的连续性。

49.传输协议中,srio业务帧只有一个帧头,包含了帧头识别字符,目标通道号指示当前业务数据应当路由到哪个cpri光口上,目标通道由8字节组成,系统应用中定义下光口通道号为0,上光口通道号为1,这两组信号会对控制交换模块的通道开关。cpri数据包进行数据传输时,cpri的业务帧格式由iq映射、iq指示信号映射和控制模块组成。

50.多路控制器在实现多端口映射的步骤中,具体为采用first world fall through模式,当srio数据到来时,在一个时钟周期内检测到业务帧头和目标通道号,根据通道号的指向将交换通道打开,并锁定正在传输的数据通路。

51.srio端和cpri端均设计为fifo接口,即读srio fifo的数据,写入到cpri fifo中,因此要控制srio fifo接口与cpri fifo接口读写控制线相连接,且在读写数据时不能由于其他srio fifo的数据到来而进行切换,也就是要锁定正在传输的数据通路。

52.所述轮询机制进一步包括并行轮询机制、均衡轮询机制;所述并行轮询机制包括两个先进先出模块,轮询时同时判断srio fifo是否有数据,是否已被锁定,无数据或被锁定则直接往下轮询,有数据而且未被锁定则判断是否为当前交换端口,轮询后的结果反映在路由寄存器上,当正在通信的链路信号为锁定时,则不再轮询当前的通信链路;所述先进先出模块包括cpri fifo 0轮询模块、cpri fifo 1轮询模块。

53.所述均衡轮询机制为当处理完一个srio fifo的数据后,查看之后的srio fifo是否有数据,若有数据则强制关闭当前srio fifo的开关,cpri fifo 0的轮询控制模块则可以继续处理下面的数据;若后面的srio fifo都无数据或已被关闭,则打开所有的srio fifo开关,开始第二次轮询。

54.在具体实施例中,如图5所示当srio fifo 0与cpri fifo 0建立起连接时,同时输出busy信号对map模块进行信号连接锁定,防止其他srio fifox与当前cpri fifo建立连接,等数据传输完成后则释放busy信号,同时释放srio fifo 0与cpri fifo 0的信号连接,等待新的srio fifo与之再次建立。

55.map模块进一步为根据路由表的配置对srio fifo与cpri fifo之间的信号进行连接与释放;所述路由表包含通道协议定义表,根据设定的标识符,实现信号之间的连接与释放,完成数据的读取和输入;所述信号之间的连接与释放进一步采用轮询机制,通过一对多的逐个轮询,进行路由表的更新,完成数据交换映射。通道协议定义表如下表1所示,其中设定的信号标识srio_data和cpri_data信号进行连接,用于srio与cpri数据传输,srio_rd与cpri_rd信号相连,用于读出srio fifo数据,再写入到cpri fifo中。

56.表1 通道协议定义表

信号线功能定义功能描述srio_datasriofifo的输出数据64bitscpri_datacprififo的输入数据64bitsemptysriofifo空指示当fifo中有数据时,empty拉低validcprififo写使能控制valid与取反的empty信号相连,进行数据有效性控制,empty为0时写cprififo有效srio_rdsrio读使能 cpri_rdcpri端口控制的读使能 具体实施例中,设计一个8x2=16位的路由寄存器,某1位为1则表示连接,为0则表示释放。如下图6所示的路由寄存器map,0

‑

7位表示8个srio fifo与cpri fifo 0连接关系,

8

‑

15位表示8个srio fifo与cpri fifo 1连接关系。例如当第第二位为1时,表示srio fifo2与cpri fifo 0相连,当第十二位为1时表示srio fifo 5与cpri fifo 1相连。

57.由于同一时间内一个cpri fifo只能与一个srio fifo相连,因此0

‑

7位至多有1位为1,其他都为0,8

‑

15位也至多1位为1,其他位为0,整个路由表中至多存在2个标识为1。而且同一时间内不会存在同一个srio fifo同时连接两个cpri fifo,例如不存在第二位为1时,第十位也为1。即通过srio fifo中第一个数据头部指示字节,控制map路由寄存器,从而决定srio fifo与cpri fifo连接关系,但会存在多个srio fifo均要连接到cpri fifo中,例如srio fifo 0和srio fifo 1都要连接cpri fifo 0,当cpri fifo 0已连接srio fifo0时,对信号进行锁定,即busy拉高,防止后面srio fifo1与cpri fifo 0相连。

58.cpri fifo 0和cpri fifo 1同时对8个srio fifo采用一种轮询机制,即cpri fifo 0对从srio fifo 0至fifo 7逐个轮询,同时cpri fifo 1也对8个srio fifo轮询,若有srio fifo中匹配端口号的业务数据,则进行map路由表更新,完成数据交换映射。并行轮询处理如图7所示,均衡轮询处理如图8所示。

59.其中,实现并行轮询的方式为,采用cpri fifo 0轮询模块和cpri fifo 1轮询模块,并行从srio fifo 0

‑

srio fifo 7逐个轮询。轮询结果反映在路由寄存器map上。当某个srio fifo已经被锁定,则不再轮询当前srio fifo。例如srio fifo 2已经和cpri fifo 0连接并锁定,则cpri fifo1在轮询时跳过srio fifo2,从而提高轮询效率。轮询时同时判断srio fifo是否有数据,是否已被锁定,无数据或被锁定则直接往下轮询,有数据而且未被锁定则判断是否为当前交换端口。同时,使用if条件判断的组合逻辑,在一个时钟周期内对8个srio fifo进行交换关系的判断。

60.为了提高轮询效率,而且均衡处理掉8个srio fifo中的数据,即不能一直处理同一个srio fifo,导致其他srio fifo数据堆积,最后造成srio fifo满。

61.为了满足均衡轮询的条件,则控制srio fifo可接入的开关。当处理完一个srio fifo的数据后,查看之后的srio fifo是否有数据,若有数据则强制关闭当前srio fifo的开关,cpri fifo 0的轮询控制模块则继续处理下面的数据。若后面的srio fifo都无数据或已被关闭,则打开所有的srio fifo开关,开始第二次轮询。例如cpri fifo 0已连接srio fifo 2,同时检测后面srio fifo是否有数据,srio fifo 7中有数据,则关闭cpri fifo 0与srio fifo2的使用,即使srio fifo 2中仍然有可用数据进行传输。当cpri fifo 0与srio fifo 7建立连接后则可将上面的srio fifo开关均打开,开始第二次轮询,因为后面已无srio fifo。

62.步骤三、输出转换后的通信数据,完成数据通信。

63.如上所述,尽管参照特定的优选实施例已经表示和表述了本发明,但其不得解释为对本发明自身的限制。在不脱离所附权利要求定义的本发明的精神和范围前提下,可对其在形式上和细节上做出各种变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1