一种基于RTL网表的时钟网络提取方法与流程

一种基于rtl网表的时钟网络提取方法

技术领域

1.本发明属于电子设计自动化技术领域,特别是涉及一种基于rtl网表的时钟网络提取方法。

背景技术:

2.当数字信号跨时钟域传输时,就会产生亚稳态问题。亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。每一个触发器都有其规定的建立和保持时间参数, 在这个时间窗口内,输入信号在时钟的上升沿是不允许发生改变的。如果触发器的数据输入端口上数据在这个时间窗口内发生变化(或者数据更新),那么就会产生时序违规,触发器的输出将徘徊在不可预知的电平状态,即亚稳态。随着设计的复杂度越来越高,多时钟域的使用也越来越普遍。因此,跨时钟域导致的设计错误问题日渐突显。而跨时钟域分析的首要任务就是对设计中的时钟网络进行提取。

3.传统的时钟网络提取是通过人工完成的。随着设计规模的不断扩大,逻辑功能越来越复杂,人工分析的效率和准确性都大打折扣。

技术实现要素:

4.针对以上技术问题,本发明提供一种基于rtl网表的时钟网络提取方法。

5.本发明解决其技术问题采用的技术方案是:一种基于rtl网表的时钟网络提取方法,方法包括以下步骤:s100:获取rtl网表,收集rtl网表的所有时序逻辑器件,从rtl网表的时序逻辑器件回溯推导,得到输入信号源到时序逻辑器件的信号路径;s200:获取配置文件,根据配置文件判断是否提供了时钟信号源,若是,根据时钟信号源进行正向推导,得到时钟信号源到第一层时序节点的信号路径;s300:使用s200获得的时钟信号源到第一层时序节点的信号路径对s100中获得的输入信号源到时序逻辑器件的信号路径进行过滤,去除输入信号源到时序逻辑器件的信号路径中与时钟信号源到第一层时序节点的信号路径没有吻合的信号路径,得到过滤后的输入信号源到时序逻辑器件的信号路径;s400:对过滤后的输入信号源到时序逻辑器件的信号路径和时钟信号源到第一层时序节点的信号路径进行合并,得到时钟网络。

6.优选地,s100包括:s110:获取rtl网表,收集rtl网表的所有时序逻辑器件,对每个时序逻辑器件的输入端口进行分析,筛选出时钟端口进行前向跟踪;s120:在前向跟踪过程中,若遇到组合逻辑电路,则对组合逻辑电路的每个输入端口进行反向跟踪;若遇到时序逻辑器件,则选取时序逻辑器件的时钟端口进行反向跟踪,直至回溯到输入信号源,得到输入信号源到时序逻辑器件的信号路径。

7.优选地,s200包括:

从时钟信号源出发,向后搜索与时钟信号源连接的信号线或器件,直到遇到时序逻辑器件,得到时钟信号源到第一层时序节点的信号路径。

8.优选地,s300包括:s310:从输入信号源到时序逻辑器件的信号路径中任选一条作为检查对象;s320:使用时钟信号源到第一层时序节点的信号路径中的每一条与检查对象进行对比,如果路径存在部分重合则认可该路径,如果所有时钟信号源到第一层时序节点的信号路径中都没有与检查对象存在重合的路径,则舍弃检查对象;s330:重复s310和s320,直到所有输入信号源到时序逻辑器件的信号路径均被检查完毕,得到过滤后的输入信号源到时序逻辑器件的信号路径。

9.优选地,s400包括:s410:从多条输入信号源到时序逻辑器件的信号路径和多条时钟信号源到第一层时序节点的信号路径中任选一条作为初始化时钟网络;s420:将剩下的所有的信号路径合并至初始化时钟网络中,得到完整的时钟网络。

10.优选地,s200中还包括:若未提供时钟信号源,则对多条输入信号源到时序逻辑器件的信号路径进行合并,得到时钟网络。

11.优选地,对多条输入信号源到时序逻辑器件的信号路径进行合并,得到时钟网络,包括:从多条输入信号源到时序逻辑器件的信号路径任选一条作为初始化时钟网络;将剩下的所有的信号路径合并至初始化时钟网络中,得到完整的时钟网络。

12.优选地,合并包括:将待合并的信号路径从输入信号源开始与当前时钟网络中的节点进行对比,若存在相同的节点,则将当前时钟网络中的节点与待合并的信号路径中的合并后的前驱节点连接,待合并的信号路径中的后续节点从当前时钟网络中的相同节点处重复合并过程,直到待合并的信号路径中的所有节点都合并完成。

13.优选地,将待合并的信号路径从信号源开始与当前时钟网络中的节点进行对比之后,还包括:若不存在相同的节点,则在当前时钟网络中新建该节点,并与待合并的信号路径中的合并后的前驱节点连接,待合并的信号路径中的后续节点从新建的节点处重复合并过程,直到待合并的信号路径中的所有节点都合并完成。

14.上述一种基于rtl网表的时钟网络提取方法,以rtl网表为必须输入,时钟信号源为可选输入,从rtl网表中的时序逻辑器件回溯推导,获取输入信号源到时序逻辑器件的信号路径并过滤;再通过提供的时钟源信息正向推导,得到时钟信号源到第一层时序节点的信号路径,解决门控时钟带来的路径混淆问题;最后对过滤后的输入信号源到时序逻辑器件的信号路径和时钟信号源到第一层时序节点的信号路径进行合并得到一个完整的时钟网络。

15.对设计中的时钟网络的分析和提取提供了一种高效的处理方法,能够方便地用于时钟相关分析方法和工具中,大幅提高传统人工分析方法的工作效率。

附图说明

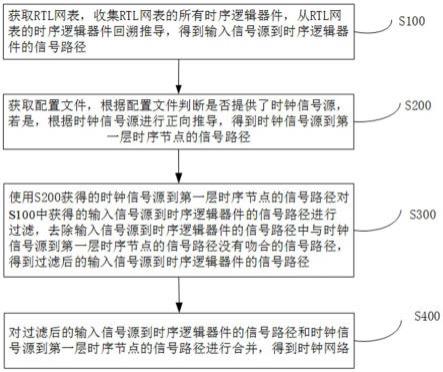

16.图1为本发明一实施例中提供的一种基于rtl网表的时钟网络提取方法流程图;图2为本发明一实施例中提供的一种正向推导解决回溯推导导致的门控时钟混淆问题的示意图;图3为本发明另一实施例中提供的一种基于rtl网表的时钟网络提取方法流程图。

具体实施方式

17.为了使本技术领域的人员更好地理解本发明的技术方案,下面结合附图对本发明作进一步的详细说明。

18.在一个实施例中,如图1所示,一种基于rtl网表的时钟网络提取方法,方法包括以下步骤:s100:获取rtl网表,收集rtl网表的所有时序逻辑器件,从rtl网表的时序逻辑器件回溯推导,得到输入信号源到时序逻辑器件的信号路径。

19.具体地,rtl在电子科学中指的是寄存器转换级电路(register transfer level)的缩写,也叫暂存器转移层次。

20.在一个实施例中,s100包括:s110:获取rtl网表,收集rtl网表的所有时序逻辑器件,对每个时序逻辑器件的输入端口进行分析,筛选出时钟端口进行前向跟踪;s120:在前向跟踪过程中,若遇到组合逻辑电路,则对组合逻辑电路的每个输入端口进行反向跟踪;若遇到时序逻辑器件,则选取时序逻辑器件的时钟端口进行反向跟踪,直至回溯到输入信号源,得到输入信号源到时序逻辑器件的信号路径。

21.具体地,从时序节点的时钟端口出发,向前搜索与该端口连接的信号线或器件,遇到组合逻辑器件(没有时钟驱动端口的器件)则继续向前搜索其所有输入端口,遇到时序逻辑器件(带有时钟驱动端口的器件)则继续向前探索其时钟端口,直到搜索至输入信号源,即该信号线不再有前驱节点。通过该回溯搜索过程得到从输入信号源至所有时序逻辑器件的信号路径(以线性链表方式存储)。

22.s200:获取配置文件,根据配置文件判断是否提供了时钟信号源,若是,根据时钟信号源进行正向推导,得到时钟信号源到第一层时序节点的信号路径。

23.具体地,配置文件是指约束文件等能够指定时钟信号源的文件。基于提供的时钟信号源进行正向推导,直到推导至时序器件的时钟端口或下层模块的输入端口。正向推导由于源的可靠性以及多扇出器件相对较少,能够对门控时钟造成的时钟信号源混淆起到很好的过滤。如下图2所示,门控时钟的情况下,如果仅使用回溯推导,会将使能信号误判为时钟信号源,得到多余的错误时钟信号路径(即使能-》与门-》寄存器),但在从时钟出发的正向推导中就可以得到且仅得到正确的时钟信号路径(即时钟-》与门-》寄存器)。

24.进一步地,时钟信号源到第一层时序节点的信号路径实际上就是从时钟信号源(一般为用户提供的时钟输入端口或时钟生成模块的输出端口)出发,正向推导直到的第一个时序逻辑器件的路径。

25.在一个实施例中,s200包括:从时钟信号源出发,向后搜索与时钟信号源连接的信号线或器件,直到遇到时序

逻辑器件,得到时钟信号源到第一层时序节点的信号路径。

26.s300:使用s200获得的时钟信号源到第一层时序节点的信号路径对s100中获得的输入信号源到时序逻辑器件的信号路径进行过滤,去除输入信号源到时序逻辑器件的信号路径中与时钟信号源到第一层时序节点的信号路径没有吻合的信号路径,得到过滤后的输入信号源到时序逻辑器件的信号路径。

27.在一个实施例中,s300包括:s310:从输入信号源到时序逻辑器件的信号路径中任选一条作为检查对象;s320:使用时钟信号源到第一层时序节点的信号路径中的每一条与检查对象进行对比,如果路径存在部分重合则认可该路径,如果所有时钟信号源到第一层时序节点的信号路径中都没有与检查对象存在重合的路径,则舍弃检查对象;s330:重复s310和s320,直到所有输入信号源到时序逻辑器件的信号路径均被检查完毕,得到过滤后的输入信号源到时序逻辑器件的信号路径。

28.s400:对过滤后的输入信号源到时序逻辑器件的信号路径和时钟信号源到第一层时序节点的信号路径进行合并,得到时钟网络。

29.在一个实施例中,s400包括:s410:从多条输入信号源到时序逻辑器件的信号路径和多条时钟信号源到第一层时序节点的信号路径中任选一条作为初始化时钟网络;s420:将剩下的所有的信号路径合并至初始化时钟网络中,得到完整的时钟网络。

30.在一个实施例中,如图3所示,s200中还包括:若未提供时钟信号源,则对多条输入信号源到时序逻辑器件的信号路径进行合并,得到时钟网络。

31.在一个实施例中,对多条输入信号源到时序逻辑器件的信号路径进行合并,得到时钟网络,包括:从多条输入信号源到时序逻辑器件的信号路径任选一条作为初始化时钟网络;将剩下的所有的信号路径合并至初始化时钟网络中,得到完整的时钟网络。

32.在一个实施例中,合并包括:将待合并的信号路径从输入信号源开始与当前时钟网络中的节点进行对比,若存在相同的节点,则将当前时钟网络中的节点与待合并的信号路径中的合并后的前驱节点连接,待合并的信号路径中的后续节点从当前时钟网络中的相同节点处重复合并过程,直到待合并的信号路径中的所有节点都合并完成。

33.在一个实施例中,将待合并的信号路径从信号源开始与当前时钟网络中的节点进行对比之后,还包括:若不存在相同的节点,则在当前时钟网络中新建该节点,并与待合并的信号路径中的合并后的前驱节点连接,待合并的信号路径中的后续节点从新建的节点处重复合并过程,直到待合并的信号路径中的所有节点都合并完成。

34.具体地,从得到的信号路径集合中任意选取一条作为初始化时钟网络,将余下的信号路径逐条合并至时钟网络中。合并过程如下:将待合并的信号路径从信号源开始与当前时钟网络中的节点进行对比,若存在相同的节点,则将时钟网络中的节点与信号路径中的合并后的前驱节点连接,信号路径中的后续节点从该时钟网络中的相同节点处重复合并

过程。若不存在相同的节点,则在时钟网络中新建该节点,并与信号路径中的合并后的前驱节点连接,信号路径中的后续节点从该新建的节点处重复合并过程。直到信号路径中的所有节点都合并完成。

35.上述一种基于rtl网表的时钟网络提取方法,以rtl网表为必须输入,时钟信号源为可选输入,从rtl网表中的时序逻辑器件回溯推导,获取输入信号源到时序逻辑器件的信号路径并过滤;再通过提供的时钟源信息正向推导,得到时钟信号源到第一层时序节点的信号路径,解决门控时钟带来的路径混淆问题。最后对过滤后的输入信号源到时序逻辑器件的信号路径和时钟信号源到第一层时序节点的信号路径进行合并得到一个完整的时钟网络。

36.对设计中的时钟网络的分析和提取提供了一种高效的处理方法,能够方便地用于时钟相关分析方法和工具中,大幅提高传统人工分析方法的工作效率。

37.以上对本发明所提供的一种基于rtl网表的时钟网络提取方法进行了详细介绍。本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本发明进行若干改进和修饰,这些改进和修饰也落入本发明权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1