一种图像数据接口的输入处理方法及电路与流程

本发明涉及图像处理,具体涉及一种图像数据接口的输入处理方法及电路。

背景技术:

1、目前,通常的非压缩视频接口会使用类似于cea-861提供的接口方式。该接口用来传输非压缩视频图像,会传输帧消隐区vblank、行消隐区hblank和有效图像,其中包含有帧同步vsync、行同步hsync、数据有效信号de(data enable)、像素时钟(pix_clk)和非压缩视频数据。帧同步/行同步/数据有效信号时序关系如图1所示,在图1中,de在有效区会一直连续,不得出现断续的情况。

2、像素时钟为传输像素速率倍数的时钟,最常见的是和像素速率一致,也有为像素速率两倍的或更多倍数的,在某些情况下也有为像素速率一半的情况。像素时钟一个比较常见的情况是高清1920x1080p@60。这时候像素时钟通常是148.5mhz,和像素传输速率相同。

3、非压缩视频数据传输图像,是从上到下逐行传输,每行是从左到右逐像素点传输。(某些情况下也不完全是绝对的逐行逐点,但是基本是这种顺序)。

4、如图2所示,图2左侧为第三方输入进来的rgb图像数据,经过输入处理电路后,数据保持之前的时序发给hdmi tx控制器,经过hdmi协议处理后发给hdmi tx phy,最后由电视接收。整个过程中都没有把数据放入到dram缓冲。

5、其中,hdmi tx ctrl控制器处理需要的时钟由hdmi txphy提供,因为精度要求很高,不能使用rgb发送过来的时钟,而是由hdmi txphy的pll提供,这就造成了这两个时钟频率不可能完全成整数比例的情况。因此必须使用异步fifo进行处理。然而,如果单纯使用传统的异步fifo,就会导致图像出现部分像素缺失的情况,表现在电视上就是会感觉图像不稳定。

6、另外,当接收到这种非压缩视频接口,需要用不同的时钟转接(依然使用这种非压缩的接口方式)——例如相对于输入接口的像素时钟,输出的接口数据后面需要使用其他相应倍率关系的时钟(比如两倍像素时钟)来处理,但由于无法使用输入的像素时钟来产生那些时钟,则需要用另一个时钟产生器来产生一个输出时钟和后面用于处理的相应时钟(比如两倍像素时钟),这里输出时钟和输入时钟频率基本相同——但由于输入和输出的时钟频率上一定会有些微的差异,例如差1/1000(这种差异来自于两个时钟来自不同源的时钟产生器)。

7、由于输入和输出有不同时钟,因此通常情况下就会使用异步fifo来处理,如图3和图6所示。图3中,push_tx是外部控制逻辑发过来的写数据请求,如果此时遇到fifo满(即full为真),则不能写数据,一直等到不满的时候才能写数据,采用一个与非门,输入信号为full信号逻辑取反及push_tx,输出信号为对fifo的写信号push_en,基本逻辑就是push_tx为真,且full为假的时候,push_en才为真;pop_tx是外部控制逻辑发来的读数据请求,和push_tx的逻辑类似,empty取代了full来成为抑制读的信号。

8、但是这样做可能会导致两种情况:

9、1、保证输入和输出的数据完全相同,不会丢失数据。输入数据(push_data)为vsync/hsync/de/data,当异步fifo为非满状态时(full为假)写数据到异步fifo;当异步fifo为非空状态时(empty为假)从里面读取数据。push_en为真表示写数据,pop_en为真表示读数据。由于输入和输出的时钟频率不完全相同,因此工作时一定会出现满(full为真)或者空(empty为假)的时候。如果出现满状态,则无法写入输入的接口数据,这对于接收端是不可以接受的,因为前面提到的接口里面每个时钟都在传输数据,这种传输不能被暂停,如果一旦无法写入,则输入数据会丢失,和前面的预期不符;如果出现空状态,则pop_en会出现断续的现象,那么输出的de也就可能会断续,这也不符合本接口的要求。所以这样做异步fifo逻辑不符合需求。

10、2、保证输入和输出都不会出现暂停这样的断续情况,即push_en和pop_en始终为真。但是这样一来还是会出现空或者满的状态。如果出现满,异步fifo就不会在那一时刻输入push_data(因为此时内部已经没有空间装载新的数据了),那么在输出端后面读取的时候就会少一笔数据;如果出现空,异步fifo就不会在那一刻输出pop_data(因为此时已经没有数据了),输出的数据就会出现断续的情况。当然,也可以在出现空的时候,输出数据还是保持输出上一次的数据以便保证输出不会断续,但这样一来会导致输出端多了一笔数据。因此,这样做的结果是输出端可能会出现丢失数据或者多了数据的情况。具体到图像上,就是有可能出现每隔一些行就有某条线相对其他线多了一个点(甚至多于一个)或者少了一个点(甚至多于一个)的情况。这可能会导致屏幕上画面不是很稳定的现象。具体如图4和图5所示,其中,图4为异步fifo经常出现满时最终图像会出现的表现,图5为异步fifo经常出现空时最终图像会出现的表现。

11、因此,为了杜绝出现上面的情况,使得接收方每条线收到的像素点数目相同,减少接收方数据处理的难度,是目前急需解决的一个技术难题。

技术实现思路

1、为了克服现有技术的不足,本发明的目的在于提供一种图像数据接口的输入处理方法及其电路,该方法和电路用于解决经过异步fifo处理的有效图像数据不够完整,接收方处理数据难度较大等问题。

2、为解决上述问题,本发明所采用的技术方案如下:

3、一种图像数据接口的输入处理方法,应用于一种图像数据接口的输入处理电路,该方法包括:

4、确定异步fifo的内存大小以及所述异步fifo的预满和预空信号出现的阈值条件,所述异步fifo用于转接输入和输出时钟不同的图像数据信号;

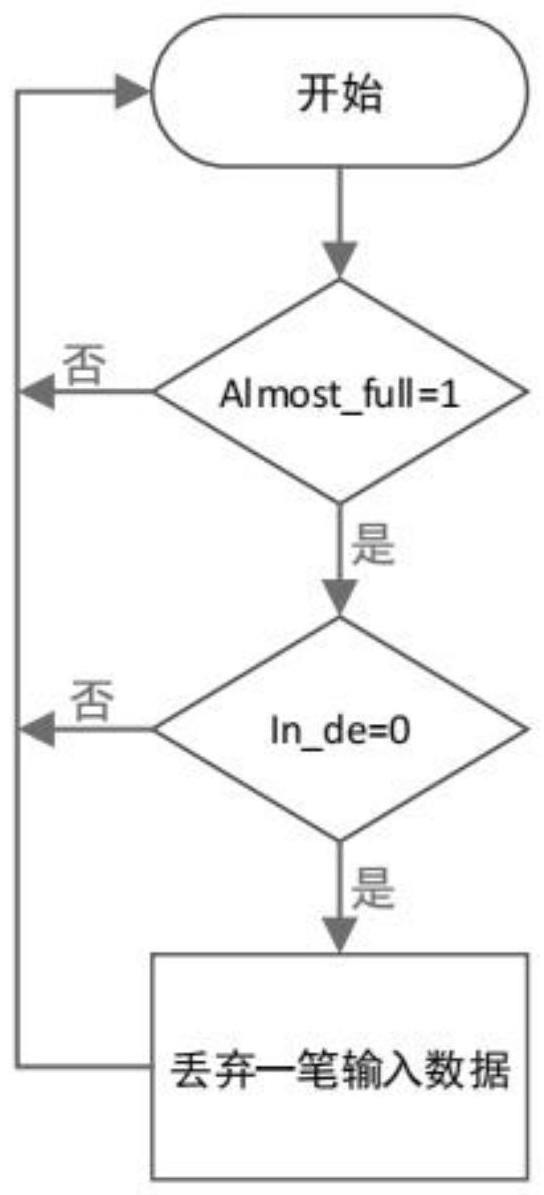

5、在所述异步fifo的输入端,判断所述预满信号是否为真;

6、如判断结果为是,则继续判断当前正在输入的是否为有效图像数据;

7、如是,则继续向所述异步fifo写入数据,如否,则暂停一次向所述异步fifo写入数据;

8、如果判断所述预满信号为假,则向所述异步fifo写入实时数据;

9、在所述异步fifo的输出端,判断所述预空信号是否为真;

10、如判断结果为是,则继续判断出现预空信号前最后一个时钟周期输出的是否为有效图像数据;

11、如是有效数据,则输出实时数据,如不是有效数据,则复制所述出现预空信号前最后一个时钟周期的数据后输出;

12、如判断结果为所述预空信号为假,则输出实时信号。

13、所述确定异步fifo的标志信号的阈值条件,包括:设图像水平像素为m,时钟误差范围为-n~n,n为百分数,则确定异步fifo的预满信号和预空信号的阈值为k:k=m*n*2,当所述异步fifo内还剩k个像素的空余位置时,进入预满状态;当所述异步fifo内还剩k个像素的数据时,进入预空状态。例如:假设图像水平像素m为4096,时钟误差范围n为正负0.5%,则阈值k为m*n*2=41。这里乘以2是因为n最小为-0.5%,最大为0.5%,两者的差是n*2。

14、以上技术方案的发明构思为:在进入almost_full状态时,此时异步fifo还有k个空余位置用来填入像素值,在异步fifo处于刚进入图像有效线的位置,则需要连续输入m个像素才会到blank区域;由于异步fifo的输入时钟比输出时钟快出n值,当连续输入完成m个像素的时候,输出约为l个像素,m>l,因为异步fifo里面留有k个空余位置,所以不会造成上溢。当一条线连续像素输入完成之后进入到blank区域,异步fifo在确认进入blank区域后,会连续忽略输入数据,此时输入数据为blank数据,直到退出预满状态。

15、在一些实施方式中,所述有效图像数据由de信号表示,所述de信号是一个有效数据选通信号,在de信号为真期间所对应的视频数据信号为有效图像数据信号。

16、与上述方法对应的一种图像数据接口的输入处理电路,用于实现一个不同时钟的图像协议输入处理,其包括:异步fifo电路以及与所述异步fifo电路交互的协议控制逻辑电路。

17、在一些实施方式中,所述协议控制逻辑电路用于:根据预满信号以及当前输入的数据是否为有效数据,判断是否继续向异步fifo写入数据并执行写入,以及,根据预空信号及预空信号出现之前最后一个时钟周期的数据是否为有效数据,判断输出实时数据还是输出复制的无效数据并执行输出。

18、其中一种实施方式为:

19、所述协议控制逻辑电路包括预满控制单元及预空控制单元;

20、所述预满控制单元包括第一逻辑取反电路、第一与非门及第一与门,异步fifo的almost_full信号与第一与非门的一个输入端连接,输入的de信号经所述第一逻辑取反电路后与第一与非门的另一个输入端连接,第一与非门的输出端与第一与门的一个输入端连接,外部控制逻辑发过来的写数据请求push_tx与第一与门的另一个输入端连接,第一与门的输出端与所述异步fifo的输入端连接;

21、所述预空控制单元包括第二逻辑取反电路、第二与非门及第二与门,异步fifo的almost_empty信号与第二与非门的一个输入端连接,输入的de信号经所述第二逻辑取反电路后与第二与非门的另一个输入端连接,第二与非门的输出端与第二与门的一个输入端连接,外部控制逻辑发来的读数据请求请求pop_tx是与第二与门的另一个输入端连接,第二与门的输出端与所述异步fifo的输出端连接。所述输出控制单元包括寄存器和选择器,寄存器的输入端和pop_data连接,寄存器的输出端与选择器的一个输入端连接,选择器的另一个输入端与pop_data连接,选择器的输出端输出数据。当判断为需要输出所述的出现almost_empty之前最后一个时钟周期输出的无效数据时,该寄存器不会存储新的数据数据,其他时刻均需要存储fifo的输出数据。

22、相较于现有技术,本发明具有以下优点:

23、本发明在当前异步fifo设计的基础上增加一个协议控制逻辑电路,用于实现不同时钟的图像协议输入处理,通过在输入端丢弃部分无效数据以及在输出端复制部分无效数据,可以确保经过异步fifo处理的数据格式的有效图像数据足够完整,从而减少了接收方处理数据的难度。

24、下面结合附图和具体实施方式对本发明作进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!