一种摄像头系统图像数据传输方法、摄像头系统和计算机程序产品与流程

本发明涉及摄像头系统图像数据传输方法、摄像头系统和计算机程序产品,尤其涉及单mipi d-phy 连接多路cmos图像传感器的图像数据传输方法。

背景技术:

1、mipi:全称移动行业处理器接口(mobile industry processor interface)。mipi是由mipi联盟发起的为移动应用处理器制定的开放标准。mipi可分为物理层和逻辑层两大部分。mipi按照物理层(physical standard)划分可分为:d-phy、c-phy、m-phy三种。d-phy的逻辑层主要是面向摄像头(csi)、显示屏(dsi)等用途,d-phy中的d是罗马数字500的意思,d-phy最初版本是可以支持500mbits/s。d-phy采用差分信号传输方式(不全是差分,lp是单端传输),每条lane由2根信号线组成,分别是p和n,clock lane是必不可少的,datalane的数量可以根据数据传输的吞吐率来选择,至少要有一个data lane。

2、目前采用多个cis(cmos image sensor)的多目摄像头越来越多的出现在市场上,这些摄像头实现方案中,需要将多个cis的图像数据传输到单个摄像头的soc芯片,普遍采用了方案1 和方案2。

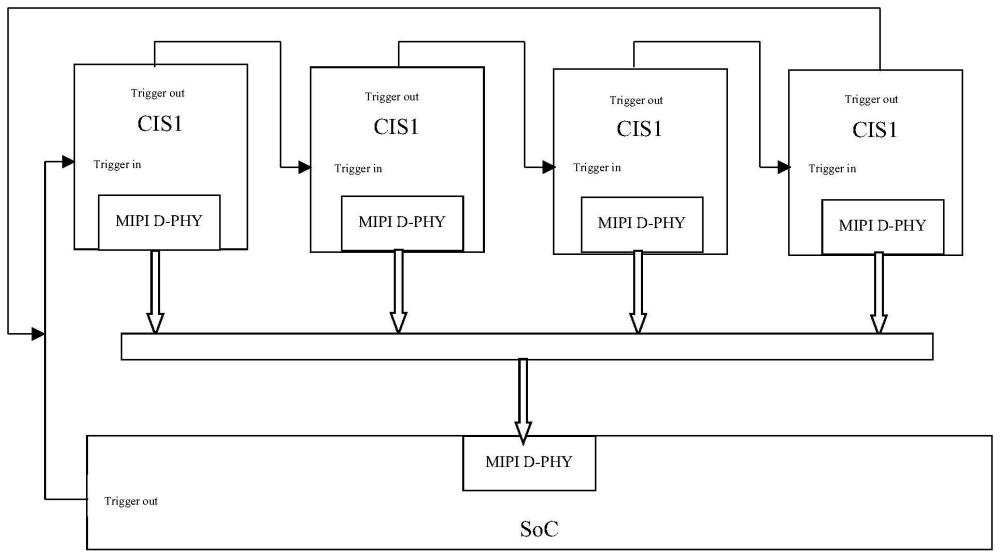

3、方案1如图1所示,soc芯片上有4个mipi d-phy,通过4根cable并行接收cis1到cis4的数据。图像数据传输控制逻辑如下:上电后cis1~cis4根据配置,连续输出图像数据,soc通过4个mipi d-phy分别接受到cis1~cis4图像数据,并存储到对应内存缓冲区。方案1需要有多个mipi d-phy,相对于只有单个mipi-phy的方案,设计生产的摄像头soc芯片时需要占用较多的晶元面积来实现,同时多个mipi接口在封装时需要引出更多的管脚,这两点都会增加摄像头soc芯片的成本,从而增加摄像头方案实现的成本。

4、方案2如图2所示,soc上只有1个mipi d-phy,通过1个cable于mipi switch 芯片连接,4个cis通过4根cable也于mipi switch 连接,soc通过switch ctl 信号控制mipiswitch 芯片在4个通道间切换,分时接受cis1~cis4的数据。图像数据传输控制逻辑如下:上电后cis1~cis4根据配置,连续输出图像数据;step1: soc先通过switch ctl控制mipiswitch 切换到1通道,当soc 接受到cis1完整的一帧图像数据后,存储到对应内存缓冲区后;step2: soc再通过switch ctl 控制mipi switch 切换到2通道,当soc 接受到cis2完整的一帧图像数据后,存储到对应内存缓冲区后;step3: soc再通过switchctl 控制mipi switch 切换到3通道,当soc 接受到cis3完整的一帧图像数据后,存储到对应内存缓冲区后;step4: soc再通过switch ctl 控制mipi switch 切换到4通道,当soc 接受到cis4完整的一帧图像数据后,存储到对应内存缓冲区后;循环执行step1-4,轮询接收cis1-cis4的图像数据, 并存储到对应内存缓冲区。方案2 需要增加一个mipi switch 芯片,因此也会增加整体摄像机方案实现的成本。

技术实现思路

1、为了解决上述的技术问题,本发明的目的是提供一种单mipi d-phy 连接多路cmos图像传感器的图像数据传输方法,该方法由于只需要一个mipi d-phy,可以减少多目摄像头soc的设计生产成本,从而降低摄像头方式实现的成本。

2、为了实现上述的目的,本发明采用了以下的技术方案:

3、一种单mipi d-phy 连接多路cmos图像传感器的图像数据传输方法,摄像头soc芯片上至少设置1个mipi d-phy芯片和1个控制摄像头图像传感器cis的io,soc芯片和n个摄像头图像传感器cis1~cisn的mipi dphy芯片间通过星型总线直连;图像数据传输控制逻辑如下:

4、上电后,初始状态下,根据配置cis1~cisn的mipi d-phy都处于高阻态;

5、step1: cis1收到trigger后开始,输出1帧图像数据,cis1输出的图像数据带有符合mipi virtual channel 规范的vc标记信息, cis1输出完毕后,将mipi d-phy恢复到高阻态,并根据预先配置的延时参数,延时后,通过trigger out口输出trigger 信号到cis2trigger in口;

6、step2: cis2收到trigger后开始,输出1帧图像数据,cis2输出的图像数据带有符合mipi virtual channel 规范的vc标记信息, cis2输出完毕后,将mipi d-phy恢复到高阻态,并根据预先配置的延时参数,延时后,通过trigger out口输出trigger 信号到cis3trigger in口;

7、以此类推;

8、stepn-1: cisn-1完毕后收到trigger后开始输出1帧图像数据,cis n-1输出的图像数据带有符合mipi virtual channel 规范的vc标记信息, cis n-1输出完毕后,将mipid-phy恢复到高阻态,并根据预先配置的延时参数,延时后,通过trigger out口输出trigger 信号到cisn trigger in口;

9、stepn: cisn完毕后收到trigger后开始输出1帧图像数据,cisn输出的图像数据带有符合mipi virtual channel 规范的vc标记信息, cisn输出完毕后,将mipi d-phy恢复到高阻态,并根据预先配置的延时参数,延时后,通过trigger out口输出trigger 信号到cis1 trigger in口;

10、循环执行step1~stepn,soc的mipi d-phy 不断收到图像数据,并根据数据中的vc标记信息,将cis1~cisn的图像数据存储在对应的内存缓冲区。

11、作为优选,所述vc标记信息允许多个图像数据源通过单一的物理通道传输数据;数据包的头部包含用于区分来自不同虚拟通道的数据的虚拟通道标识符vcid。

12、作为再优选,所述数据包由短数据包和长数据包两部分组成,两种类型的数据包都包含vcid字段;

13、短数据包:包括数据类型,虚拟通道id,以及6位的数据字段;

14、长数据包:包括数据类型,虚拟通道id,数据长度,然后是一个变长的数据负载,最后是一个crc校验。

15、作为优选,所述step1~stepn中当多个cis通过一个物理通道传输数据给soc时,每个cis 传输数据结束后,设置延时参数延时,再触发下一个cis传输数据,这个延时量通过soc配置给cis,能够控制单位时间数据的传输量,以和soc的数据处理能力相匹配。

16、作为优选,所述n≥2;优选为4-10。

17、作为另外一种实施方式,本发明还提供了另外一个技术方案:

18、一种单mipi d-phy 连接多路cmos图像传感器的图像数据传输方法,摄像头soc芯片上至少设置1个mipi d-phy芯片和n个控制摄像头图像传感器cis的io,soc芯片和n个摄像头图像传感器cis1~cisn的mipi d-phy芯片间通过星型总线直连;图像数据传输控制逻辑如下:

19、上电后,初始状态下,根据配置cis1~cisn的mipi d-phy都处于高阻态;

20、setp1: soc 通过trigger out-1口输出trigger信号到cis1 trigger in口;cis1收到trigger后开始,输出1帧图像数据, cis1输出完毕后,将mipi d-phy恢复到高阻态;

21、setp2: soc 通过trigger out-2口输出trigger信号到cis2 trigger in口;cis2收到trigger后开始,输出1帧图像数据, cis2输出完毕后,将mipi d-phy恢复到高阻态;

22、以此类推;

23、stepn-1:soc 通过trigger out-n-1口输出trigger信号到cisn-1 trigger in口;cisn-1到trigger后开始,输出1帧图像数据, cisn-1输出完毕后,将mipi d-phy恢复到高阻态;

24、stepn: soc 通过trigger out-n口输出trigger信号到cisn trigger in口;cisn收到trigger后开始,输出1帧图像数据, cisn输出完毕后,将mipi d-phy恢复到高阻态;

25、循环执行step1-n,soc的mipi d-phy 不断收到图像数据,并根据trigger out的状态信息,将cis1~cisn的图像数据存储在对应的内存缓冲区。

26、作为优选,n≥2;优选为4-10。

27、进一步,本发明还提供了一种监控摄像头系统,该系统包括摄像头soc芯片和n个摄像头图像传感器cis1~cisn;摄像头soc芯片上设置1个mipi d-phy芯片和1个控制摄像头图像传感器cis的io,soc芯片和n个摄像头图像传感器cis1~cisn的mipi dphy芯片间通过星型总线直连;或者,所述像头soc芯片上设置1个mipi d-phy芯片和n个控制摄像头图像传感器cis的io,soc芯片和n个摄像头图像传感器cis1~cisn的mipi d-phy芯片间通过星型总线直连;图像数据传输控制逻辑采用上述的方法。

28、进一步,本发明还提供了一种计算机设备,包括存储器、处理器及存储在存储器上的计算机程序,其特征在于,所述处理器执行所述计算机程序以实现所述方法。

29、进一步,本发明还提供了一种计算机可读存储介质,其上存储有计算机程序或指令,该计算机程序或指令被处理器执行时实现所述方法。

30、本发明由于采用了上述的技术方案,由于只需要一个mipi d-phy,可以减少多目摄像头soc的设计生产成本,从而降低摄像头方式实现的成本。

- 还没有人留言评论。精彩留言会获得点赞!