ARINC818解码与eDP显示系统及方法与流程

本发明涉及arinc818视频总线与机载显示处理的,尤其涉及一种arinc818解码与edp显示系统及方法。

背景技术:

1、arin818是一种非压缩的视频编解码标准,广泛应用于机载座舱显示系统中,采用非压缩视频的点对点传输。传统的arinc818视频编码应用大部分采用单lane链路模式,链路速率大部分不高于4.25gbps。受限于arinc818的链路带宽,其传输的视频的分辨率及视频帧率无法提高,因此无法传输更高分辨率及高刷新率的视频。

2、随着机载视频分辨率以及视频刷新率的提高,迫切需要提高arinc818的传输带宽。提高arinc818的传输带宽有两种方式,一种是提高链路数量,另外一种是提高链路速率。另外,对于显示领域来说,一般采用edp接口增大视频显示的带宽。本文针对高带宽arinc818传输的场合,提出了一种4lanearinc818视频解码与edp显示系统及方法,单线链路速率为10gbps,可以实现最大40gbps的链路带宽。另外,首次完成了arinc818视频解码到edp视频输出的转化,转化过程采用逻辑实现,避免了引入视频帧存带来的额外的延时,可以实现微妙级别的视频处理延时。

技术实现思路

1、有鉴于此,本发明提供的一种arinc818解码与edp显示系统,解决机载航电显示领域高带宽arinc818解码与edp显示方法,实现4lane arinc818视频解码,链路带宽达到40gbps,具备高带宽edp显示功能,并且采用fifo行缓存进行低延时视频转化处理。

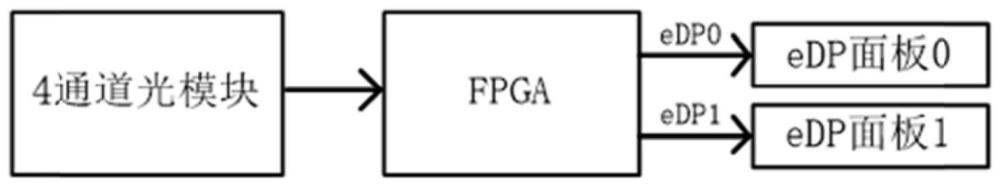

2、一种arinc818解码与edp显示系统,适用于机载上座舱显示系统数据处理,座舱显示系统设置有显示器,包括配置有4个数据通道的光模块、fpga模块和edp面板,光模块接收机载系统的数据,其中,

3、所述光模块的每个数据通道传输不同像素分布格式的数据,并arinc818解码协议物理层的光电转化单元,且所述fpga模块进行通讯,每个所述数据通道的单线链路速率为10gbps;

4、所述fpga模块对应的接收每个数据通道传输的数据,通过高速串行bank直接输出edp信号至所述edp面板;

5、所述edp面板用于图像的分区显示,且包括edp面板0和edp面板1,edp面板0和edp面板1分别用于不同像素分布格式数据的显示。

6、有益效果

7、该系统可以实现多lane的arinc818解码,解码带宽可以实现40gbps的无压缩视频解码,去掉了功耗较大的ddr、sram等器件,避免采用了常规的帧缓存方式,采用行缓存的方式,可以实现一幅视频转两路edp视频输出,延时达到微妙级别,同时降低了系统的功耗,并且,该系统可以作为机载座舱显示的最新技术参考,为新型机载显示器的研制提供一种架构思路,可以极大提高解码与传输带宽,包括提高视频的分辨率和视频的帧率。

技术特征:

1.一种arinc818解码与edp显示系统,适用于机载上座舱显示系统数据处理,座舱显示系统设置有显示器,其特征在于,包括配置有4个数据通道的光模块、fpga模块和edp面板,光模块接收机载系统的数据,其中,

2.根据权利要求1所述的arinc818解码与edp显示系统,其特征在于,所述fpga模块至少包括3个高速串行收发bank,且每个所述高速串行收发bank包括4个高速串行收发器,至少分配一个高速串行收发bank用于4lane数据通道的arinc818解码,且分配2高速串行收发bank用于edp面板的显示。

3.根据权利要求2所述的arinc818解码与edp显示系统,其特征在于,所述fpga模块包括多个arinc818_decoder模块,每个所述arinc818_decoder模块匹配一个数据通道,根据arinc818协议的进行数据解码。

4.根据权利要求3所述的arinc818解码与edp显示系统,其特征在于,所述fpga模块还包括video-data-distribution模块,所述video-data-distribution模块包括axis_data_width_converter模块、axis_data_fifo模块、axis_data_spilit模块、vid_timing_gen模块和data_fifo模块,其中,

5.根据权利要求4所述的arinc818解码与edp显示系统,其特征在于,所述vid_tming_gen模块接口包括4像素视频接口,能够产生vid_data96、视频行同步信号hs、视频场同步信号vs和视频数据有效信号de,输入至所述edp面板。

6.根据权利要求5所述的arinc818解码与edp显示系统,其特征在于,

7.根据权利要求5所述的arinc818解码与edp显示系统,其特征在于,

8.根据权利要求7所述的arinc818解码与edp显示系统,其特征在于,

9.根据权利要求8所述的arinc818解码与edp显示系统,其特征在于,所述fpga模块还包括displayport模块,所述displayport模块包括dp_subsystem模块、vphy模块和microblaze模块,所述dp_subsystem模块、vphy模块分别通过axi lite总线配置有寄存器,其中,

10.一种arinc818解码与edp显示方法,其特征在于,使用如权利要求9所述的rinc818解码与edp显示系统,其特征在于,其方法包括

技术总结

本发明的ARINC818解码与eDP显示系统,包括光模块、FPGA模块和eDP面板,光模块接收机载系统的数据,光模块的每个数据通道传输不同像素分布格式的数据,并ARINC818解码协议物理层的光电转化单元;所述FPGA模块对应的接收每个数据通道传输的数据,通过高速串行bank直接输出eDP信号至所述eDP面板;所述eDP面板用于图像的分区显示。实现ARINC818视频解码到eDP视频输出的转化,转化过程采用逻辑实现,避免了引入视频帧存带来的额外的延时,可以实现微妙级别的视频处理延时。

技术研发人员:杨炳伟,高伟林,范威,辛春明,闫欣宇,贺龙龙

受保护的技术使用者:苏州长风航空电子有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!