MCU与FPGA驱动液晶屏的电路、显示屏及电子设备的制作方法

mcu与fpga驱动液晶屏的电路、显示屏及电子设备

技术领域

1.本实用新型涉及显示屏技术领域,尤其涉及mcu与fpga驱动液晶屏的电路、显示屏及电子设备。

背景技术:

2.很多设备都需要界面交互,一般的情况下单独使用mcu驱动液晶屏绘图。某些需要大量高速运算的绘图,也会单独使用fpga驱动液晶屏绘图。而上述两种方式存在以下缺点:第一,mcu进行大量运算的时候太慢了,无法使用在需要大量运算的绘图中;第二,fpga使用verilog之类的硬件描述语言,使用复杂,开发工程量大,开发速度慢。

技术实现要素:

3.针对现有技术存在的不足,本实用新型的目的是提供mcu与fpga驱动液晶屏的电路进行显示屏驱动,至少用于解决现有显示屏驱动电路存在的运算慢,硬件描述语言使用复杂,开发工程量大,开发速度慢中的一个技术问题。

4.根据本实用新型的第一个方面,提供了mcu与fpga驱动液晶屏的电路,包括fpga单元和mcu单元;

5.fpga单元用于第一图层数据处理;

6.mcu单元的输入端与fpga单元的输出端连接,mcu单元的输出端与显示屏单元的输入端连接,mcu单元用于第二图层数据处理,mcu单元还用于将第一图层数据和第二图层数据进行硬件图层混合处理后传输给显示屏单元。

7.本实用新型的mcu与fpga驱动液晶屏的电路,先通过fpga单元处理第一图层数据,mcu单元处理第二图层数据,然后再通过mcu单元将第一图层数据和第二图层数据进行硬件图层混合处理,即对图层数据先进行同时分布处理,再进行硬件图层混合处理,以便同时获得mcu单元的开发简单灵活高的效果和fpga单元的高速并行运算功能,以此来解决单一处理单元处理图层数据存在的运算慢,硬件描述语言使用复杂,开发工程量大,开发速度慢等问题。

8.在一些实施方式中,mcu单元为f1c100s芯片。

9.在一些实施方式中,mcu单元的晶振连接端连接有晶振单元。

10.在一些实施方式中,mcu单元与显示屏单元通过rgb通信接口连接。

11.在一些实施方式中,fpga单元为xc6slx25芯片。

12.在一些实施方式中,fpga单元与mcu单元通过csi通信接口连接。

13.根据本实用新型的第二个方面,提供显示屏,该显示屏包括上述任一项的mcu与fpga驱动液晶屏的电路和显示屏单元。

14.根据本实用新型的第三个方面,提供电子设备,该电子设备包括上述的显示屏。

15.与现有技术相比,本实用新型的mcu与fpga驱动液晶屏的电路、显示屏及电子设备,先通过fpga单元处理第一图层数据,mcu单元处理第二图层数据,然后再通过mcu单元将

第一图层数据和第二图层数据进行硬件图层混合处理,即对图层数据先进行同时分布处理,再进行硬件图层混合处理,以便同时获得mcu单元的开发简单灵活高的效果和fpga单元的高速并行运算功能,以此来解决单一处理单元处理图层数据存在的运算慢,硬件描述语言使用复杂,开发工程量大,开发速度慢等问题。

附图说明

16.图1为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的电路结构示意图;

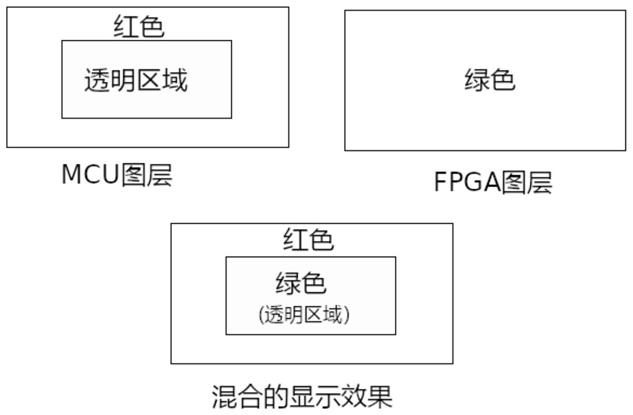

17.图2为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的mcu单元进行硬件图层混合示意图;

18.图3为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的fpga单元的电路原理图;

19.图4为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的mcu单元的电路原理图;

20.图5为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的mcu单元的晶振单元的电路原理图;

21.图6为为本实用新型一实施方式的mcu与fpga驱动液晶屏的电路的显示屏单元的连接端的电路原理图。

22.附图标号说明:fpga单元100,mcu单元200,显示屏单元300。

具体实施方式

23.下面结合附图对本实用新型作进一步详细的说明。

24.图1示意性地显示了根据本实用新型的一种实施方式的mcu与fpga驱动液晶屏的电路。如图1所示,该mcu与fpga驱动液晶屏的电路包括fpga单元100和mcu单元200;fpga单元100用于第一图层数据处理;mcu单元200的输入端与fpga单元100的输出端连接,mcu单元200的输出端与显示屏单元300的输入端连接,mcu单元200用于第二图层数据处理,mcu单元200还用于将第一图层数据和第二图层数据进行硬件图层混合处理后传输给显示屏单元300。本实施方式先通过fpga单元100处理第一图层数据,mcu单元200处理第二图层数据,然后再通过mcu单元200将第一图层数据和第二图层数据进行硬件图层混合处理,即对图层数据先进行同时分布处理,再进行硬件图层混合处理,以便同时获得mcu单元200的开发简单灵活高的效果和fpga单元100的高速并行运算功能,以此来解决单一处理单元处理图层数据存在的运算慢,硬件描述语言使用复杂,开发工程量大,开发速度慢等问题。

25.如图2所示,硬件图层混合实现方式为采用mcu单元200的硬件图层混合功能;fpga单元100传输到mcu单元200的第一图层数据(fpga图层)放在mcu单元200的内存中,mcu单元200的第二图层数据(mcu图层)也在mcu单元200的内存中;mcu单元200内存中的图层数据(即第一图层数据和第二图层数据)与显示屏单元300像素点的颜色对应;透明区域的点对应特殊值(如32位显示颜色时,值为0);传输到显示屏单元300时,mcu单元200的第一图层中的透明区域,使用fpga单元100的第二图层相对应的区域。当然上述方式只是为了解释硬件图层混合过程,其并不是对本实施方式的限制,本实施方式还可以采用其它现有的图层混合方式。

26.如图3-4所示,fpga单元100为xc6slx25芯片,mcu单元200为f1c100s芯片,f1c100s芯片能够实现上述的硬件图层混合功能,其中,xc6slx25芯片和f1c100s芯片通过csi通信接口连接(即fpga单元与mcu单元通过csi通信接口连接);具体的连接方式为xc6slx25芯片的csipclk端、csihs端、csivs端、csid0端、csid1端、csid2端、csid3端、csid4端、csid5端、csid6端、csid7端分别与f1c100s芯片的csipclk端(第47脚)、csihs端(第49脚)、csivs端(第48脚)、csid0端(第46脚)、csid1端(第45脚)、csid2端(第44脚)、csid3端(第43脚)、csid4端(第42脚)、csid5端(第41脚)、csid6端(第40脚)、csid7端(第49脚)对应连接。

27.如图5所示,f1c100s芯片的晶振连接端连接有晶振单元(即mcu单元200的晶振连接端连接有晶振单元),晶振单元包括晶振y2、电容c208和电容c209,晶振y2的in端与f1c100s芯片的hosc1端(第51脚)连接,晶振y2的in端通过电容c208接地,晶振y2的out端与f1c100s芯片的hosc0端(第52脚)连接,晶振y2的out端通过电容c209接地。

28.根据本实用新型的第二个方面,提供显示屏,该显示屏包括上述任一项的mcu与fpga驱动液晶屏的电路和显示屏单元300,f1c100s芯片与显示屏单元300通过rgb通信接口连接,显示屏单元300的连接端如图6所示,具体的连接方式为显示屏单元300的lcdde端、lcdvs端、lcdhs端、lcdclk端、lcdd2端、lcdd3端、lcdd4端、lcdd5端、lcdd6端、lcdd7端、lcdd10端、lcdd11端、lcdd12端、lcdd13端、lcdd14端、lcdd15端、lcdd18端、lcdd19端、lcdd20端、lcdd21端、lcdd22端、lcdd23端分别与f1c100s芯片的lcdde端(第27脚)、lcdvs端(第29脚)、lcdhs端(第28脚)、lcdclk端(第26脚)、lcdd2端(第6脚)、lcdd3端(第7脚)、lcdd4端(第8脚)、lcdd5端(第9脚)、lcdd6端(第10脚)、lcdd7端(第11脚)、lcdd10端(第12脚)、lcdd11端(第13脚)、lcdd12端(第14脚)、lcdd13端(第15脚)、lcdd14端(第16脚)、lcdd15端(第17脚)、lcdd18端(第18脚)、lcdd19端(第19脚)、lcdd20端(第21脚)、lcdd21端(第23脚)、lcdd22端(第24脚)、lcdd23端(第25脚)连接。

29.根据本实用新型的第三个方面,提供电子设备,该电子设备包括上述的显示屏。

30.以上所述的仅是本实用新型的一些实施方式。对于本领域的普通技术人员来说,在不脱离本实用新型创造构思的前提下,还可以做出若干变形和改进,这些都属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1