一种显示面板及显示装置的制作方法

1.本发明涉及显示技术领域,尤其涉及一种显示面板及显示装置。

背景技术:

2.对于具有摄像功能的显示面板,为了提高面板的屏占比,通常在面板的显示区内设置一个高透光区,并在该高透光区设置摄像组件。以液晶显示面板为例,面板在进行摄像时,高透光区内的液晶分子在像素电极和公共电极所形成的电场的作用下旋转,外界环境光透过液晶分子射入摄像组件,实现对外界环境光的采集,进而实现成像。

3.但是,基于现有的液晶显示面板的结构,外界环境光射入后会产生较为明显的衍射现象,从而对成像质量产生不良影响。

技术实现要素:

4.本发明提供一种显示面板及显示装置,以降低衍射现象对成像质量的影响。

5.第一方面,本发明实施例提供一种显示面板,包括第一显示区和第二显示区,所述第一显示区的光线透过率大于所述第二显示区的光线透过率;

6.所述第一显示区包括多个第一子像素,至少部分所述第一子像素包括电极组,所述电极组包括第一电极和第二电极;沿第一方向上,所述第一电极的正投影与所述第二电极的正投影至少部分交叠,所述第一方向平行于所述显示面板的出光面;在拍摄阶段,所述第一电极与所述第二电极之间的电压差大于零伏;所述第一电极与所述第二电极之间夹压的相性随帧反转。

7.第二方面,本发明实施例提供一种显示装置,包括第一方面所述的显示面板。

8.本发明实施例中,第一电极和第二电极在平行于显示面板所在平面的方向上的投影交叠,即,第一电极和第二电极在与显示面板所在平面垂直的一个平面上的投影交叠。第一电极和第二电极之间会形成一个水平电场。从而使得位于第一电极和第二电极之间的液晶分子的旋转方向一致,从而使得跟随电场方向旋转的液晶分子排列方向一致。避免了现有技术中对称弧形电场导致的两种角度的液晶分子,避免了两种角度液晶分子的形成的光栅结构,从而外界环境光透过角度一致的液晶分子后的相位相同,光波在叠加后不会形成明显的衍射条纹,从而有效降低了衍射条纹对成像质量的影响。在本发明实施例中,第一电极和第二电极在压差的作用下所形成的电场是强度均一的横向电场,不同位置处的液晶分子的旋转程度趋于相同,有效弱化了液晶分子的旋转程度差异,提高了第一显示区的透光均一性。而且,在该横向电场的驱动下,液晶分子旋转后的角度均趋于该压差对应的预设旋转角度,还可进一步提高第一显示区的整体透光率。进而在第一显示区进行画面显示时,提高第一显示区的亮度及亮度均匀性,优化画面显示效果,当第一显示区进行摄像时,提高经由第一显示区射入的外界环境光的量,优化成像效果。进一步地,在拍摄阶段,第一电极与第二电极之间夹压的相性随帧反转,即,假设在一帧中,电场方向沿第一方向由第一电极指向第二电极,在下一帧中,电场方向沿第一方向由第二电极指向第一电极,液晶分子受到的

电场方向随帧反转,从而防止液晶分子的极化现象的发生,进而防止出现液晶逐渐失去旋转特性而影响画面显示阶段的显示效果的问题。

附图说明

9.图1为现有技术中液晶显示面板的俯视图;

10.图2为图1沿a1

’‑

a2’方向的剖视图;

11.图3为现有技术中电极不加电时产生的衍射条纹的示意图;

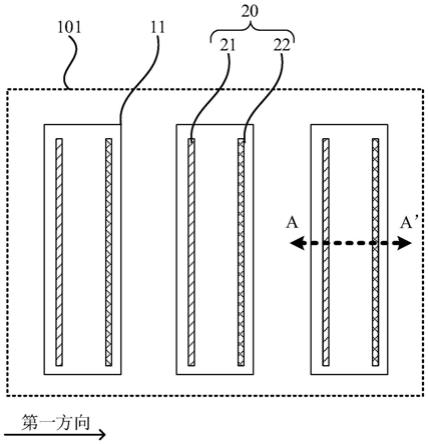

12.图4为本发明实施例提供的一种显示面板的俯视结构示意图;

13.图5为图4中第一显示区的俯视结构示意图;

14.图6为沿图5中aa’的剖面结构示意图;

15.图7为本发明实施例提供的一种显示面板的剖面结构示意图;

16.图8为本发明实施例提供的一种显示区的俯视结构示意图;

17.图9为沿图8中bb’的剖面结构示意图;

18.图10为本发明实施例提供的另一种显示面板的剖面结构示意图;

19.图11为本发明实施例提供的一种作为对比例的显示面板的剖面结构示意图;

20.图12为本发明实施例提供的另一种显示面板的剖面结构示意图;

21.图13为本发明实施例提供的另一种显示面板的剖面结构示意图;

22.图14为本发明实施例提供的另一种显示面板的剖面结构示意图;

23.图15为本发明实施例提供的另一种显示面板的剖面结构示意图;

24.图16为本发明实施例提供的另一种显示面板的剖面结构示意图;

25.图17为本发明实施例提供的另一种显示面板的剖面结构示意图;

26.图18为本发明实施例提供的另一种显示面板的剖面结构示意图;

27.图19为本发明实施例提供的另一种显示面板的剖面结构示意图;

28.图20为本发明实施例提供的另一种显示面板的剖面结构示意图;

29.图21为本发明实施例提供的另一种第一显示区的俯视结构示意图;

30.图22为本发明实施例提供的一种第一电极和第二电极施加电信号的示意图;

31.图23为本发明实施例提供的另一种显示面板的俯视结构示意图;

32.图24为本发明实施例提供的另一种显示面板的俯视结构示意图;

33.图25为本发明实施例提供的另一种显示面板的俯视结构示意图;

34.图26为本发明实施例提供的另一种显示面板的俯视结构示意图;

35.图27为本发明实施例提供的另一种显示面板的俯视结构示意图;

36.图28为本发明实施例提供的一种信号控制电路的电路示意图;

37.图29为本发明实施例提供的另一种信号控制电路的电路示意图;

38.图30为本发明实施例提供的另一种显示面板的俯视结构示意图;

39.图31为本发明实施例提供的另一种信号控制电路的电路示意图;

40.图32为本发明实施例提供的另一种信号控制电路的电路示意图;

41.图33为本发明实施例提供的另一种信号控制电路的电路示意图;

42.图34为本发明实施例提供的另一种信号控制电路的电路示意图;

43.图35为本发明实施例提供的另一种信号控制电路的电路示意图;

44.图36为本发明实施例提供的另一种信号控制电路的电路示意图;

45.图37为本发明实施例提供的另一种第一电极和第二电极施加电信号的示意图;

46.图38为本发明实施例提供的另一种显示面板的俯视结构示意图;

47.图39为沿图38中cc’的剖面结构示意图;

48.图40为本发明实施例提供的另一种显示面板的剖面结构示意图;

49.图41为本发明实施例提供的另一种显示面板的俯视结构示意图;

50.图42为本发明实施例提供的另一种显示面板的俯视结构示意图;

51.图43为本发明实施例提供的另一种显示面板的俯视结构示意图;

52.图44为本发明实施例提供的另一种显示面板的俯视结构示意图;

53.图45为沿图44中dd’的剖面结构示意图;

54.图46为本发明实施例提供的另一种显示面板的俯视结构示意图;

55.图47为本发明实施例提供的另一种显示面板的俯视结构示意图;

56.图48为本发明实施例提供的一种显示装置的结构示意图。

具体实施方式

57.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

58.如图1和图2所示,图1为现有技术中液晶显示面板的俯视图,图2为图1沿a1

’‑

a2’方向的剖视图,液晶显示面板的显示区1’包括高透光区2’,高透光区2’设置有摄像组件。液晶显示面板包括相对设置的阵列基板3’和彩膜基板4’,阵列基板3’和彩膜基板4’之间设有液晶分子5’。阵列基板3’内设有多个像素单元6’,像素单元6’包括像素电极7’和公共电极8’。

59.液晶显示面板进行摄像时,高透光区2’内的像素电极7’接收驱动电压,液晶分子5’在像素电极7’和公共电极8’所形成的电场的作用下旋转,外界环境光透过液晶分子5’射入摄像组件。

60.发明人研究发现,高透光区2’内原有的像素单元6’的开口区已经呈周期性排布,即使不给电极加电,外界环境光进入这种周期性排布后也会产生衍射现象,衍射条纹如图3所示。而对电极加电后,液晶分子5’在电极所形成的电场的作用下会呈更密集的周期性旋转排布,外界环境光进入这种更密集的周期性排布后,衍射现象更加明显。

61.以边缘场开关模式(fringe field switching,ffs)为例,在该种模式下,请再次参见图1和图2,像素电极7’和公共电极8’在垂直于显示面板所在平面的方向上交叠,像素电极7’为梳状结构,像素电极7’包括间隔排布的多个电极条9’。对像素电极7’加电后,像素电极7’中的每个电极条9’均会和两侧的公共电极8’形成不同方向的电场,液晶分子5’在不同方向电场的作用下沿不同方向旋转,多列液晶分子5’形成了密集的周期性旋转排布。外界环境光在进入液晶分子5’这种密集的周期性排布后,射出的光具有一定的相位差,在后续传输过程中更容易发生周期性干涉,导致衍射现象加剧。

62.图4为本发明实施例提供的一种显示面板的俯视结构示意图,图5为图4中第一显示区的俯视结构示意图,参考图4和图5,显示面板包括第一显示区101和第二显示区102,第

一显示区101的光线透过率大于第二显示区102的光线透过率,第一显示区101为显示区103内设置的一个高透光区,在该高透光区可以设置摄像组件。第一显示区101包括多个第一子像素11,至少部分第一子像素11包括电极组20,电极组20包括第一电极21和第二电极22。在一实施方式中,任一第一子像素11均包括第一电极21和第二电极22。在另一实施方式中,一部分第一子像素11包括第一电极21和/或第二电极22,另一部分第一子像素11不设置第一电极21和第二电极22。沿第一方向上,第一电极21的正投影与第二电极22的正投影至少部分交叠,第一方向平行于显示面板的出光面,即,第一方向平行于显示面板所在平面。在拍摄阶段,第一电极21与第二电极22之间的电压差大于零伏,第一电极21与第二电极22之间夹压的相性随帧反转。

63.本发明实施例中,第一电极21和第二电极22在平行于显示面板所在平面的方向上的投影交叠,即,第一电极和第二电极在与显示面板所在平面垂直的一个平面上的投影交叠。第一电极21和第二电极22之间会形成一个水平电场。从而使得位于第一电极21和第二电极22之间的液晶分子的旋转方向一致,从而使得跟随电场方向旋转的液晶分子排列方向一致。避免了现有技术中对称弧形电场导致的两种角度的液晶分子,避免了两种角度液晶分子的形成的光栅结构,从而外界环境光透过角度一致的液晶分子后的相位相同,光波在叠加后不会形成明显的衍射条纹,从而有效降低了衍射条纹对成像质量的影响。在本发明实施例中,第一电极和第二电极在压差的作用下所形成的电场是强度均一的横向电场,不同位置处的液晶分子的旋转程度趋于相同,有效弱化了液晶分子的旋转程度差异,提高了第一显示区的透光均一性。而且,在该横向电场的驱动下,液晶分子旋转后的角度均趋于该压差对应的预设旋转角度,还可进一步提高第一显示区的整体透光率。进而在第一显示区进行画面显示时,提高第一显示区的亮度及亮度均匀性,优化画面显示效果,当第一显示区进行摄像时,提高经由第一显示区射入的外界环境光的量,优化成像效果。进一步地,在拍摄阶段,第一电极21与第二电极22之间夹压的相性随帧反转,即,假设在一帧中,电场方向沿第一方向由第一电极21指向第二电极22,在下一帧中,电场方向沿第一方向由第二电极22指向第一电极21,液晶分子受到的电场方向随帧反转,从而防止液晶分子的极化现象的发生,进而防止出现液晶逐渐失去旋转特性而影响画面显示阶段的显示效果的问题。需要说明的是,第一子像素11通常包括开口区和围绕所述开口区设置的非开口区,上述第一电极21和第二电极22的设置位置可与开口区交叠,如附图5所示,也可以与非开口区交叠,当第一电极21和第二电极22设置位置与开口区交叠时,第一电极21和第二电极22由透明导电材料制成,如此设置,可以使得开口区保持较高的透光率,避免第一电极21、第二电极21对开口区的正常出光造成影响。

64.由于需要第一电极21和第二电极22之间形成的电场为水平电场,当第一电极21和第二电极22对置表面积越大,在第一电极21和第二电极22之间形成的平行电场面积强度越大,从而使更多位置处的液晶分子的旋转状态一致,不同位置处光线的穿透率也就更接近。尤其地,当第一电极21和第二电极22的高度等于阵列基板与彩膜基板之间的间距时,第一电极21和第二电极22之间各个位置处光线的穿透率的差异较小,从而使各个位置处射入的外界环境光的数量趋于相同。因此增加此第一电极21和第二电极22在垂直于显示面板所在平面的方向上的高度,可提高横向电场的分布范围,充分保证液晶分子在横向电场作用下旋转,使第一显示区101保持较高的透光率。在对置长度不变的情况下,第一电极21、第二电

极22沿显示面板出光方向上的高度越大,对置面积也就越大。第一电极21和第二电极22在垂直于显示面板所在平面的方向上具有较大的高度时,可提高了横向电场的分布范围,充分保证液晶分子在横向电场作用下旋转,使第一显示区101保持较高的透光率。通过堆叠第一电极21、第二电极22在垂直于显示面板所在平面的方向上的高度是实现上述技术效果的一种手段。然而,为达到上述目的,也可通过其他的实施方式得以实现。例如,通过设置辅助支撑物垫高第一电极21、第二电极22的高度。

65.图6为沿图5中aa’的剖面结构示意图,参考图4

‑

图6,显示面板还包括多个凸台30,凸台30对应第一显示区101设置,沿第一方向,凸台30包括相对设置的第一侧面301和第二侧面302。同一个电极组20中,第一电极21至少部分覆盖第一侧面301,第二电极22至少部分覆盖第二侧面302。本发明实施例中,显示面板在第一显示区101还设置有多个凸台30,凸台30的第一侧面301和第二侧面302为第一电极21和第二电极22提供了倾斜表面,第一电极21和第二电极22分别设置于凸台30的第一侧面301和第二侧面302上,受到目前电极工艺能力的限制,若直接利用导电材料形成电极(包括第一电极21和第二电极22),电极无法做的过高。通过设置凸台30,不仅可以提高第一电极21和第二电极22的对置表面积,此外,鉴于第一电极21和第二电极22只需沉积在凸台30的表面,可以在凸起部表面覆盖导电层的方式形成电极,电极高度无需再受到电极工艺能力的限制,高度设计更为灵活,有助于应用在高盒厚的显示面板中。第一电极21和第二电极22的厚度可减小,在一定程度上,降低了第一电极21和第二电极22制程工艺的难度,进一步节省第一电极21和第二电极22的材料用量。进一步地,由于第一电极21和第二电极22分别设置于凸台30的第一侧面301和第二侧面302上,凸台30的第一侧面301和第二侧面302为第一电极21和第二电极22提供依靠和支撑,从而提高了第一电极21和第二电极22的结构稳定性。在其他实施方式中,同一个电极组20中,第一电极21至少部分覆盖第二侧面302,第二电极22至少部分覆盖第一侧面301。

66.图7为本发明实施例提供的一种显示面板的剖面结构示意图,参考图7显示面板包括阵列基板40、对置基板50和液晶层60。液晶层60位于阵列基板40和对置基板50之间,液晶层60包括液晶分子,在拍摄阶段,液晶分子在第一电极21和第二电极22之间的电场驱动下旋转,用于将外界光线投射至感光元件上用于成像。凸台30可以位于阵列基板40和/或对置基板50上。第一电极21可以位于阵列基板40和/或对置基板50上,第二电极22可以位于阵列基板40和/或对置基板50上。

67.参考图7,凸台30包括第一凸台31,第一凸台31位于阵列基板40朝向对置基板50的表面。第一电极21和第二电极22均位于阵列基板40上。可以理解的是,显示面板中的各种驱动晶体管和信号走线通常设置在阵列基板40内,因此,将第一电极21和第二电极22设置在阵列基板40上,当利用驱动晶体管或是驱动信号线向电极传输信号时,第一电极21和第二电极22直接通过过孔和与其对应的驱动晶体管或连接走线电连接即可,工艺难度较低,连接可靠性也更强。而且,阵列基板40上用于间隔信号走线的绝缘膜层较多,可以选择其中的至少一个绝缘膜层来制作第一凸台31,以满足第一凸台31的高度要求,并简化了制作工艺。凸台30可以采用现有面板中的平坦化层、光学胶等有机膜层制作,或是由氮化硅等无机材料制作。

68.图8为本发明实施例提供的一种显示区的俯视结构示意图,图9为沿图8中bb’的剖面结构示意图,参考图8和图9,第二显示区102包括多个第二子像素12,第二子像素12包括

公共电极121和像素电极122,公共电极121与像素电极122均位于阵列基板40上。在显示阶段,液晶分子在公共电极121与像素电极122之间的电场驱动下旋转,实现正常的画面显示。第一电极21、第二电极22与公共电极121和/或像素电极122在同一膜层工艺中形成。也就是说,第一电极21和第二电极22可以与公共电极121在同一膜层工艺中形成,第一电极21和第二电极22也可以与像素电极122在同一膜层工艺中形成,第一电极21、第二电极22、公共电极121和像素电极122可以在同一膜层工艺中形成。本发明实施例中,第一电极21、第二电极22与公共电极121和/或像素电极122在同一膜层工艺中形成,无需为第一电极21和第二电极22设置单独的膜层工艺,从而简化了工艺制程。

69.图10为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图10,阵列基板40还包括第一基板41,第一基板41作为阵列基板40的衬底,在第一基板41上还可以形成阵列基板40中的像素驱动电路等结构。第一基板41可以为刚性基板或者柔性基板。公共电极121位于第一基板41与像素电极122之间。显示面板还包括第三电极23和第四电极24,第三电极23位于凸台30的第一侧面301与第一电极21之间,第四电极24位于凸台30的第二侧面302与第二电极22之间。第一电极21、第二电极22与像素电极122在同一膜层工艺中形成,第三电极23、第四电极24与公共电极121在同一膜层工艺中形成。本发明实施例中,在形成公共电极121时,采用同一膜层工艺形成第三电极23和第四电极24。在形成像素电极122时,采用同一膜层工艺形成第一电极21和第二电极22。从而简化了工艺制程。另一方面,第三电极23与第一电极21形成的存储电容可以维持第一电极21上电压一段时间,第四电极24与第二电极22形成的存储电容可以维持第二电极22上电压一段时间,从而,在拍摄阶段,无需时时刻刻为第一电极21和第二电极22供电,提升成像的稳定性。

70.可选地,参考图10,显示面板还包括钝化层123和电极间隔层25。钝化层123位于公共电极121与像素电极122之间,钝化层123起到电绝缘公共电极121与像素电极122的作用。电极间隔层25位于第一电极21与第三电极23之间,以及位于第二电极22与第四电极24之间。位于第一电极21与第三电极23之间的电极间隔层25起到电绝缘第一电极21与第三电极23的作用,位于第二电极22与第四电极24之间的电极间隔层25起到电绝缘第二电极22与第四电极24的作用。电极间隔层25与钝化层123在同一膜层工艺中形成,在形成钝化层123时,采用同一膜层工艺形成电极间隔层25,无需为电极间隔层25设置单独的膜层工艺,从而简化了工艺制程。

71.图11为本发明实施例提供的一种作为对比例的显示面板的剖面结构示意图,参考图11,垂直于第一基板41的方向上,第一电极21完全覆盖第三电极23临近第一基板41的端部。第三电极23在靠近第一基板41一端的延伸范围未超出第一电极21的覆盖范围。垂直于第一基板41的方向上,第二电极22完全覆盖第四电极24临近第一基板41的端部。第四电极24延伸并超出第二电极22的覆盖范围(如图11中虚线圆圈所示)。第三电极23延伸并超出第一电极21的部分,以及第四电极24延伸并超出第二电极22的部分均会形成边缘电场,影响水平电场的形成。

72.继续参考图10,第三电极23临近第一基板41的端部在显示面板的出光面的垂直投影位于第一电极21在显示面板的出光面的垂直投影内,第四电极24临近第一基板41的端部在显示面板的出光面的垂直投影位于第二电极22在显示面板的出光面的垂直投影内。本发明实施例中,垂直于第一基板41的方向上,第一电极21完全覆盖第三电极23临近第一基板

41的端部,第二电极22完全覆盖第四电极24临近第一基板41的端部。从而避免了第三电极23临近第一基板41的端部和第四电极24临近第一基板41的端部形成边缘电场,提高了拍摄阶段液晶分子的均一性,进一步地破坏了液晶分子的排列周期性,光波在叠加后不会形成明显的衍射条纹,提高了拍摄阶段的成像质量。

73.图12为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图12,第二显示区102包括多个第二子像素12,第二子像素12包括公共电极121和像素电极122,公共电极121与像素电极122均位于阵列基板40上,且公共电极121与像素电极122同层设置。在一实施方式中,第三电极23、第四电极24与公共电极121在同一膜层工艺中形成,第一电极21、第二电极22与像素电极122在同一膜层工艺中形成。在另一实施方式中,第一电极21、第二电极22与公共电极121在同一膜层工艺中形成,第三电极23、第四电极24与像素电极122在同一膜层工艺中形成。在另一实施方式中,第一电极21、第二电极22、公共电极121与像素电极122在同一膜层工艺中形成。在另一实施方式中,第三电极23、第四电极24、公共电极121与像素电极122在同一膜层工艺中形成。

74.图13为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图4和图13,第一显示区101包括开口区111和围绕开口区111的非开口区112(图13中未示出第二显示区102)。类似的,第二显示区102包括开口区111和围绕开口区111的非开口区112。对置基板50包括遮光层51,遮光层51在显示面板的出光面上的正投影覆盖非开口区112。开口区111为透光区,背光源发射的光线可以透过开口区111出射到显示面板外,实现预设的发光亮度和发光颜色。非开口区112为遮光区,通常可以在非开口区112设置有不透光的金属走线以及遮光层51等元件。凸台30包括第二凸台32,第二凸台32位于对置基板50朝向阵列基板40的表面,第二凸台32在显示面板的出光面上的正投影与遮光层51在显示面板的出光面上的正投影交叠。第一电极21和第二电极22均位于对置基板50上。本发明实施例中,第一电极21和第二电极22直接设置在对置基板50上,第一电极21以及第二电极22与遮光层51之间的相对位置关系不会受到对置基板50和阵列基板40的对位偏差等因素的影响,当电极采用金属材料形成时,避免出现由对位精度导致的遮光层51无法完全覆盖住电极的情况。进一步地,垂直于第一基板41的方向上,第二凸台32与遮光层51交叠,第二凸台32上的第一电极21和第二电极22采用金属材料形成时,遮光层51可以对第一电极21和第二电极22进行遮挡,避免第一电极21和第二电极22反射外界环境光至人眼。

75.示例性地,参考图13,对置基板50还包括第二基板52,第二基板52与第一基板41相对,第二基板52作为对置基板50的衬底,在第二基板52上可以形成对置基板50中的遮光层51等结构。

76.图14为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图14,凸台30包括第一凸台31和第二凸台32,第一凸台31位于阵列基板40朝向对置基板50的表面,第二凸台32位于对置基板50朝向阵列基板40的表面。第一凸台31以及第二凸台32均与遮光层51在显示面板的出光面上的正投影交叠。第一电极21位于第二凸台32上,第二电极22位于第一凸台31上。第二凸台32上的第一电极21与第一凸台31上的第二电极22形成水平电场。进一步地,垂直于第一基板41的方向上,第一凸台31和第二凸台32均与遮光层51交叠,第二凸台32上的第一电极21和第一凸台31上的第二电极22采用金属材料形成时,遮光层51可以对第一电极21和第二电极22进行遮挡,避免第一电极21和第二电极22反射外界环境光至人

眼。

77.图15为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图15,第一电极21位于第一凸台31上,第二电极22位于第二凸台32上。第一凸台31上的第一电极21与第二凸台32上的第二电极22形成水平电场。

78.图16为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图16,电极组20包括第一电极组201和第二电极组202,第一电极组201中的第一电极21和第二电极22均位于第一凸台31上,第二电极组202中的第一电极21和第二电极22均位于第二凸台32上。本发明实施例中,第一电极组201中的第一电极21和第二电极22均位于第一凸台31上,第一电极组201中的第一电极21和第二电极22之间形成水平电场,第二电极组202中的第一电极21和第二电极22均位于第二凸台32上,第二电极组202中的第一电极21和第二电极22之间形成水平电场。

79.可选地,参考图16,第一电极组201中的第一电极21在显示面板的出光面上的正投影与第二电极组202中的第一电极21在显示面板的出光面上的正投影交叠。第一电极组201中的第二电极22在显示面板的出光面上的正投影与第二电极组202中的第二电极22在显示面板的出光面上的正投影交叠。本发明实施例中,垂直于第一基板41的方向上,第一电极组201中的第一电极21与第二电极组202中的第一电极21交叠,交叠的第一电极组201中的第一电极21与第二电极组202中的第一电极21具有相同的电压。第一电极组201中的第二电极22与第二电极组202中的第二电极22交叠,交叠的第一电极组201中的第二电极22与第二电极组202中的第二电极22具有相同的电压。相对于仅在第一凸台31或者仅在第二凸台32上设置电极(包括第一电极21和第二电极22)而言,形成水平电场的电极高度更大,增加了水平电场的范围。另一方面,由于在第一凸台31和第二凸台32上均设置有第一电极21以及第二电极22,相对于仅在第一凸台31或者仅在第二凸台32上设置电极而言,第一凸台31和第二凸台32的高度可以设置的较小,对工艺制程能力要求较低。

80.图17为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图17,第一电极组201中的第一电极21和第二电极22均位于第一凸台31上,第二电极组202中的第一电极21和第二电极22均位于第二凸台32上。第一电极组201中的第一电极21在显示面板的出光面上的正投影与第二电极组202中的第一电极21在显示面板的出光面上的正投影不交叠。第一电极组201中的第二电极22在显示面板的出光面上的正投影与第二电极组202中的第二电极22在显示面板的出光面上的正投影不交叠。沿第一方向,第一电极组201和第二电极组202一一间隔排列,即,第一电极组201、第二电极组202、第一电极组201、第二电极组202

……

。

81.可选地,继续参考图6,凸台30还包括顶面303和底面304,顶面303和底面304均平行于显示面板的出光面。第一侧面301和第二侧面302均连接顶面303与底面304,顶面303与底面304之间的垂直距离h大于2.7微米。即,凸台30的高度大于2.7微米。可以理解的是,凸台30的高度越大,则形成在第一侧面301和/或第二侧面302上的第一电极21的高度越大,形成在第一侧面301和/或第二侧面302上的第二电极22的高度越大,增加了水平电场的范围。

82.可选地,参考图6,凸台30的顶面303的面积小于凸台30的底面的面积。参考图7,顶面303和底面304均平行于第一基板41所在平面。第一凸台31的底面304位于第一凸台31的顶面303与阵列基板40之间。参考图13,第二凸台32的底面304位于第二凸台32的顶面303与

对置基板50之间。沿第一方向,多个凸台30排列成行。凸台30的第一侧面301为凸台30朝向第一方向一侧的侧面,第二侧面302为凸台30为凸台30背离第一方向一侧的侧面。具体地,参考图7,沿第一方向,多个第一凸台31排列成行,第一凸台31的第一侧面301和与之相邻第一凸台31的第二侧面302相邻,第一凸台31的第二侧面302和与之相邻第一凸台31的第一侧面301相邻。参考图13,沿第一方向,多个第二凸台32排列成行,第二凸台32的第一侧面301和与之相邻第二凸台32的第二侧面302相邻,第二凸台32的第二侧面302和与之相邻第二凸台32的第一侧面301相邻。

83.可选地,参考图6,凸台30呈棱台状,凸台30沿第一方向的截面为梯形。一方面,在通过刻蚀等工艺形成凸台30时,容易控制刻蚀工艺,使得对待刻蚀膜层的顶部刻蚀速度大于底部刻蚀速度,以形成上小下大的棱台状结构,并不会增加工艺难度。另一方面,凸台30呈棱台状,凸台30的稳定性比较好,不容易脱落,且在上小下大的棱台状的凸台30的侧面上形成电极时,工艺难度较小。

84.图18为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图18,阵列基板40包括第一基板41和平坦化层42,平坦化层42位于第一基板41与第一凸台31之间,平坦化层42可以用于覆盖像素驱动电路等结构,以为后续在平坦化层42上形成的公共电极121和像素电极122提供平坦表面。本发明实施中,第一凸台31位于阵列基板40上时,第一凸台31位于平坦化层42远离第一基板41一侧。平坦化层42与第一凸台31可以在同一膜层工艺中形成,在形成平坦化层42时,采用同一膜层工艺形成第一凸台31,无需为第一凸台31设置单独的膜层工艺,从而简化了工艺制程。在其他实施方式中,在第一基板41的一侧形成平坦化层42之后,再在平坦化层远离第一基板41一侧形成第一凸台31。

85.图19为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图19,对置基板50还包括支撑柱53,支撑柱53在显示面板的出光面上的正投影与遮光层51在显示面板的出光面上的正投影交叠。在阵列基板40和对置基板50对盒后,至少部分支撑柱53与阵列基板40抵接,用于维持阵列基板40与对置基板50之间的距离,即用于保持液晶盒厚。第二凸台32与支撑柱53在同一膜层工艺中形成。一方面,在形成支撑柱53时,采用同一膜层工艺形成第二凸台32,无需为第二凸台32设置单独的膜层工艺,从而简化了工艺制程。另一方面,第二凸台32与支撑柱53在同一膜层工艺中形成,第二凸台32与支撑柱53均位于遮光层51与阵列基板40之间,第二凸台32还可以起到保持液晶盒厚的作用。

86.图20为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图20,第二显示区102包括多个第二子像素12(图20中示例性地示意出一个第二子像素12),第二子像素12包括公共电极121和像素电极122。显示面板包括阵列基板40、对置基板50和液晶层60,液晶层60位于阵列基板40和对置基板50之间,公共电极121与像素电极122均位于阵列基板40上。凸台30与公共电极121在同一膜层工艺中形成。本发明实施例中,在形成公共电极121时,采用同一膜层工艺形成凸台30,无需为凸台30设置单独的膜层工艺,从而简化了工艺制程。进一步地,凸台30与公共电极121在同一膜层工艺中形成,凸台30与公共电极121采用相同的材料,凸台30包括导电材料,从而凸台30与第一电极21之间可以形成存储电容,凸台30与第二电极22之间可以形成存储电容,凸台30与第一电极21之间形成的存储电容可以维持第一电极21上电压一段时间,凸台30与第二电极22之间形成的存储电容可以维持第二电极22上电压一段时间。从而,在拍摄阶段,无需时时刻刻为第一电极21和第二电极22供电。进

一步地,相对于采用绝缘材料形成凸台30而言,由于凸台30与第一电极21以及第二电极22之间均可以形成存储电容,无需再专门形成第三电极23和第四电极24,减少了膜层的数量,并简化了工艺制程。

87.需要说明的是,本发明各实施例不仅限于将公共电极121和像素电极122设置于阵列基板40上。在一些实施方式中,像素电极122还可以位于阵列基板40上,公共电极121还可以位于对置基板50上。对应地,与公共电极121在同一膜层工艺中形成的结构也位于对置基板50上。

88.继续参考图2,沿第一方向,第一电极21和第二电极22一一间隔排布。也就是说,沿第一方向,多个电极的排列方式为:第一电极21、第二电极22、第一电极21、第二电极22

……

。

89.图21为本发明实施例提供的另一种第一显示区的俯视结构示意图,参考图21,沿第一方向,多个电极组20依次排布,第一电极21与相邻电极组20中的第一电极21相邻,第二电极22与相邻电极组20中的第二电极22相邻。也就是说,沿第一方向,多个电极的排列方式为:第一电极21、第二电极22、第二电极22、第一电极21、第一电极21、第二电极22

……

。

90.继续参考图4和图5,第一子像素11包括高透子像素,高透子像素包括第一电极21和第二电极22。第一子像素11包括高透子像素,高透子像素的位置不设置色阻,外界环境光通过高透子像素时,不会被色阻的过滤,光线损耗也就较少。因此,将高透子像素作为实现摄像功能的成像子像素,能够提高外界环境光的透过率。

91.示例性地,参考图19,对置基板50还可以包括色阻54,多个色阻54可以包括红色色阻、绿色色阻和蓝色色阻,红色色阻用于将透过其的光线过滤为红色,绿色色阻用于将透过其的光线过滤为绿色,蓝色色阻用于将透过其的光线过滤为蓝色。色阻54与第二显示区102内的开口区111交叠,用于使显示面板实现彩色显示。

92.由于在第一电极21与第二电极22之间的位置固定的情况下,第一电极21与第二电极22之间的电压差越大,第一电极21与第二电极22之间的水平电场的强度越大,水平电场对液晶分子的驱动力越强,拍摄阶段液晶分子的均一性越好。第一电极21与第二电极22之间的电压差越小,第一电极21与第二电极22之间的水平电场的强度越小,水平电场对液晶分子的驱动力越弱,拍摄阶段液晶分子的均一性越差。本发明实施例中,在拍摄阶段,为第一电极21与第二电极22施加电压的差值大于或者等于10v,以提高拍摄阶段液晶分子的均一性,进一步地破坏了液晶分子的排列周期性,提高了拍摄阶段的成像质量。

93.在显示面板中,为第一电极21与第二电极22施加电压的差值大于或者等于10v,如果为第一电极21施加的电压大于或者等于0v,则需要为第二电极22施加的电压大于或者等于10v,对于显示面板来说,提供高于10v的电压会对绝缘膜层的绝缘性能以及各种元器件的电学性能产生影响。通常的显示面板中,供电电压一般不超过5.7v。本发明实施例中,在拍摄阶段,为第一电极21施加的电压与第二电极22施加电压的绝对值相等且电性相反。例如,为第一电极21施加的电压为+5v,为第二电极22施加的电压为

‑

5v,从而控制第一电极21上电压与第二电极22上电压不至于过大。进一步地,为第一电极21施加的电压与第二电极22施加电压的绝对值相等且电性相反,从而使得在为第一电极21和第二电极22施加电压时,为第一电极21与第二电极22施加电压的差值可以达到最大值,以提高拍摄阶段液晶分子的均一性。

94.可选地,在显示阶段,为第一电极21施加公共电压,第二电极22施加像素电压;或者,为第一电极21施加像素电压,第二电极22施加公共电压。本发明实施例中,在显示阶段,为第一电极21和第二电极22中的一个施加像素电压,另一个施加公共电压,从而第一电极21和第二电极22之间的液晶分子受到公共电压和像素电压产生电场的驱动,发生旋转,并控制第一子像素11在显示阶段的透过率,使第一显示区101内的第一子像素11在显示阶段配合第二显示区102内的第二子像素12发光。

95.图22为本发明实施例提供的一种第一电极和第二电极施加电信号的示意图,参考图22,第一显示区101包括至少一个第一子像素行,第一子像素行包括沿第二方向排布的多个第一子像素11,第一方向与第二方向的夹角大于或者等于0

°

且小于90

°

。需要说明的是,第一电极21和第二电极22沿第一方向排布,第一子像素行中的多个第一子像素11沿第二方向排布。为简便起见,本发明各实施例中,均以第一方向平行于第二方向为例,实际上,第一方向还可以不平行于第二方向,只要第一方向与第二方向的夹角大于或者等于0

°

且小于90

°

即可。在拍摄阶段,位于同一第一子像素行的相邻两个第一电极21分别施加电性相反的第一信号,位于同一第一子像素行的相邻两个第二电极22分别施加电性相反的第二信号。

96.示例性地,参考图22,沿第一方向,第一电极21和第二电极22一一间隔排布。在拍摄阶段,依次为多个第一电极21施加的电信号为:正性的第一信号s1+、负性的第一信号s1

‑

、正性的第一信号s1+、负性的第一信号s1

‑……

。依次为多个第二电极22施加的电信号为:正性的第二信号s2+、负性的第二信号s2

‑

、正性的第二信号s2+、负性的第二信号s2

‑……

。其中,正性的电信号代表电压为正的电信号,负性的电信号代表该电压为负的电信号。

97.示例性地,参考图22,在拍摄阶段,依次为多个第一电极21和多个第二电极22施加的电信号为:正性的第一信号s1+、负性的第二信号s2

‑

、负性的第一信号s1

‑

、正性的第二信号s2+、正性的第一信号s1+、负性的第二信号s2

‑

,

……

。施加正性的第一信号s1+的第一电极21与施加负性的第二信号s2

‑

的第二电极22之间形成水平电场。施加负性的第一信号s1

‑

的第一电极21与施加正性的第二信号s2+的第二电极22之间形成水平电场。

98.可选地,第一信号包括数据电压信号,第二信号包括源电压信号。其中,数据电压信号为在拍摄阶段经过多路选择器处理后的电压信号,源电压信号为在拍摄阶段不经过多路选择器,直接由驱动芯片输出的电压信号。需要说明的是,施加在第一电极21或者第二电极22上的像素电压也是经过多路选择器处理后的电压,与数据电压信号不同的是,像素电压为在显示阶段经过多路选择器处理后的电压信号。

99.图23为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图1和图23,显示面板还包括台阶区104,台阶区104位于显示区103的外围。通常地,如图7所示的阵列基板40的面积大于对置基板50的面积,垂直于第一基板41所在平面的方向上,对置基板50不能完全覆盖阵列基板40,阵列基板40上未被对置基板50覆盖的区域对应于台阶区104。显示面板还包括多路选择器43,多路选择器43位于台阶区104。显示面板还包括第一连接线71和第二连接线72,第一连接线71与第二连接线72分别与不同的第一电极21电连接。在拍摄阶段,第一连接线71上的第一信号与第二连接线72上的第一信号电性相反。第一连接线71和第二连接线72均与多路选择器43电连接。本发明实施例中,第一连接线71和第二连接线72均与多路选择器43电连接。在拍摄阶段,第一连接线71与第二连接线72分别施加电性相反

的第一信号,从而,位于同一第一子像素行的相邻两个第一电极21分别施加电性相反的数据电压信号。

100.示例性地,参考图23,驱动芯片ic包括多个源极端so,多个源极端so包括第一源极端so1和第二源极端so2。多路选择器43包括第一选择开关431、第二选择开关432、第三选择开关433、第四选择开关434、第五选择开关435和第六选择开关436。第一选择开关431的栅极以及第四选择开关434的栅极均与第一时钟控制端ckhr电连接,第二选择开关432的栅极以及第五选择开关435的栅极均与第二时钟控制端ckhg电连接,第三选择开关433的栅极以及第六选择开关436的栅极均与第三时钟控制端ckhb电连接。第一选择开关431的第一极、第三选择开关433的第一极以及第五选择开关435的第一极均与第一连接线71电连接,第一选择开关431的第二极、第三选择开关433的第二极以及第五选择开关435的第二极均与第一源极端so1电连接。第二选择开关432的第一极、第四选择开关434的第一极以及第六选择开关436的第一极均与第二连接线72电连接,第二选择开关432的第二极、第四选择开关434的第二极以及第六选择开关436的第二极均与第二源极端so2电连接。第一时钟控制端ckhr将第一选择开关431和第四选择开关434导通时,第一源极端so1将电压信号施加到与第一选择开关431电连接的第一连接线71上,第二源极端so2将电压信号施加到与第四选择开关434电连接的第二连接线72上。第二时钟控制端ckhg将第二选择开关432和第五选择开关435导通时,第一源极端so1将电压信号施加到与第二选择开关432电连接的第二连接线72上,第二源极端so2将电压信号施加到与第五选择开关435电连接的第一连接线71上。第三时钟控制端ckhb将第三选择开关433和第六选择开关436导通时,第一源极端so1将电压信号施加到与第三选择开关433电连接的第一连接线71上,第二源极端so2将电压信号施加到与第六选择开关436电连接的第二连接线72上。可以理解的是,每三个第一电极21可以共用同一个源极端so,从而减少源极端so的使用数量。

101.可选地,参考图23,显示面板还包括多条扫描线45(图23中以一条扫描线45为例进行示意),多条扫描线45中的至少部分位于第一显示区101,多条扫描线45沿第二方向延伸。显示面板还包括第一开关管461,第一开关管461位于第一显示区101,第一开关管461的栅极与扫描线45电连接,第一开关管461的第一极与第一电极21电连接,第一开关管461的第二极与第一连接线71或者第二连接线72电连接。本发明实施例中,第一电极21通过第一开关管461与第一连接线71或者第二连接线72电连接。在显示阶段,第二电极22接收公共电压,第一开关管461在扫描线45提供的有效电平的作用下导通,第一连接线71和第二连接线72上传输的像素电压经由导通的第一开关管461传输至第一电极21,液晶分子在第一电极21和第二电极22所形成的电场的作用下旋转,实现正常的画面显示。在拍摄阶段,第一开关管461在扫描线45提供的有效电平的作用下导通,第一连接线71与第二连接线72分别施加电性相反的第一信号,从而,位于同一第一子像素行的相邻两个第一电极21分别施加电性相反的数据电压信号。

102.图24为本发明实施例提供的另一种显示面板的俯视结构示意图,需要说明的是,为了清楚示意第二电极22的连接关系以及信号传递关系,图24中省略了第一电极21的部分连接关系以及信号传递关系,参考图24,显示面板还包括第三连接线73和第四连接线74,第三连接线73和第四连接线74分别与不同的第二电极22电连接。在拍摄阶段,第三连接线73上的第二信号与第四连接线74上的第二信号电性相反。第三连接线73和第四连接线74均与

驱动芯片ic电连接。本发明实施例中,第三连接线73和第四连接线74均与驱动芯片ic电连接。在拍摄阶段,第三连接线73与第四连接线74分别施加电性相反的第二信号,从而,位于同一第一子像素行的相邻两个第二电极22分别施加电性相反的数据电压信号。在显示阶段,第三连接线73和第四连接线74分别施加公共电压,从而使得第二电极22接收公共电压。

103.示例性地,参考图24,驱动芯片ic包括多个源极端so,多个源极端so包括第三源极端so3和第四源极端so4。奇数列的第二电极22通过第三连接线73与第三源极端so3电连接,第三源极端so3将电压信号施加到第三连接线73上,进而施加到奇数列的第二电极22上。偶数列的第二电极22通过第四连接线74与第四源极端so4电连接,第四源极端so4将电压信号施加到第四连接线74上,进而施加到偶数列的第二电极22上。

104.可选地,参考图24,每一个第一子像素11均包括一个第二电极22。第二电极22与第三连接线73通过第一过孔471电连接,第二电极22与第四连接线74通过第二过孔472电连接。第一过孔471以及第二过孔472均位于第一显示区101。沿第二方向,第一过孔471以及第二过孔472均位于相邻两个第一子像素11之间。本发明实施例中,第一过孔471位于相邻两个第一子像素11之间的间隙中,第二过孔472位于相邻两个第一子像素11之间的间隙中,第一过孔471和第二过孔472不会占用第一子像素11的空间,不会影响第一子像素11的发光显示。

105.图25为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图25,显示面板还包括多条扫描线45,多条扫描线45中的至少部分位于第一显示区101,多条扫描线45沿第二方向延伸。显示面板还包括第二开关管462,第二开关管462的栅极与扫描线45电连接,第二开关管462的第一极与第二电极22电连接,第二开关管462的第二极与第三连接线73或者第四连接线74电连接。本发明实施例中,第二电极22通过第二开关管462与第三连接线73或者第四连接线74电连接。在显示阶段,扫描线45提供的有效电平,将同一第一子像素行中的第二开关管462导通,第三连接线73和第四连接线74上传输的公共电压经由导通的第二开关管462传输至第二电极22。进一步地,由于第二电极22通过第二开关管462与第三连接线73或者第四连接线74电连接,在一个第一子像素行中的第二开关管462导通时,控制其余第一子像素行中的第二开关管462截止,从而,在显示阶段以及在拍摄阶段,仅需驱动一个第一子像素行中的第二电极22,无需驱动所有的第二电极22。

106.进一步地,参考图25,第一开关管461的栅极以及第二开关管462的栅极与同一条扫描线45电连接。在拍摄阶段,扫描线45提供的有效电平,将同一第一子像素行中的第一开关管461和第二开关管462同时导通,同一第一子像素行中的第一电极21和第二电极22同时进行充电。在一个第一子像素行中的第一电极21和第二电极22充电时,控制其余第一子像素行中的第一电极21和第二电极22不充电。故而,实现了多个第一子像素行中第一电极21和第二电极22的逐行充电,以及同一第一子像素行中的第一电极21和第二电极22的同步刷新,避免了成像闪烁的问题。

107.示例性地,参考图25,在显示阶段,扫描线45提供的有效电平,将同一第一子像素行中的第一开关管461和第二开关管462同时导通,第一连接线71和第二连接线72上传输的像素电压经由导通的第一开关管461传输至第一电极21,第三连接线73和第四连接线74上传输的公共电压经由导通的第二开关管462传输至第二电极22。图26为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图26,多个第一子像素行沿第三方向排列,第三

方向与第一方向以及第二方向均交叉。在一实施方式中,第二方向与第三方向可以相互垂直。在另一实施方式中,第二方向与第三方向可以不垂直,并呈大于0

°

且小于90

°

的夹角。沿第三方向,排列成一列的多个第一子像素11共用同一个第二电极22。本发明实施例中,沿第三方向排列成一列的多个第一子像素11与同一个第二电极22交叠,从而无需为沿第三方向排列成一列的多个第一子像素11提供多个连接过孔,减小了连接过孔占据的第一显示区101的空间,增大了第一子像素11占据的第一显示区101的空间,提高了第一显示区101的透过率。进一步地,将沿第三方向排列成一列的多个第一子像素11所共用的第二电极22连接至第三连接线73或者第四连接线74,从而可以将第二电极22与第三连接线73或者第四连接线74的连接过孔设置到第一显示区101外,提高了第一显示区101的透过率。

108.图27为本发明实施例提供的另一种显示面板的俯视结构示意图,图28为本发明实施例提供的一种信号控制电路的电路示意图,参考图27和图28,驱动芯片ic包括第一控制端cg1、第二控制端cg2和源极端so。显示面板还包括信号控制电路80,信号控制电路80包括第一电压输入单元81、第二电压输入单元82、开关单元83和公共电压输入单元84。第一电压输入单元81的第一端与第一电源端vsp电连接,第一电压输入单元81的第二端与开关单元83的第一端电连接。第二电压输入单元82的控制端与源极端so电连接,第二电压输入单元82的第一端与开关单元83的第一端电连接,第二电压输入单元82的第二端与第二电源端vsn电连接。开关单元83的控制端与第一控制端cg1电连接,开关单元83的第二端与第三连接线73或者第四连接线74电连接(图28中,以信号控制电路80驱动第三连接线73为例进行示意)。公共电压输入单元84的控制端与第二控制端cg2电连接,公共电压输入单元84的第一端与开关单元83的第二端电连接,公共电压输入单元84的第二端与公共电压端com电连接。在拍摄阶段,由于需要使第一显示区101的透过率尽可能大,即,使第一显示区101透过的外界环境光尽可能多,这就要求第一电极21与第二电极22之间的电压差比较大,提高了对驱动第一电极21与第二电极22的驱动电路的要求。本发明实施例中,采用信号控制电路80来驱动第三连接线73以及第四连接线74,信号控制电路80为专门设置的驱动电路,信号控制电路80的驱动能力比较强,从而提高了对第三连接线73以及第四连接线74的驱动能力。

109.示例性地,参考图27和图28,多个源极端so包括第五源极端so5和第六源极端so6。显示面板包括两个信号控制电路80,分别为第一信号控制电路801和第二信号控制电路802。第一控制端cg1、第二控制端cg2和第五源极端so5均与第一信号控制电路801电连接,第一信号控制电路801与第三连接线73电连接,用于驱动第三连接线73。第一控制端cg1、第二控制端cg2和第六源极端so6均与第二信号控制电路802电连接,第二信号控制电路802与第四连接线74电连接,用于驱动第四连接线74。第一信号控制电路801与第二信号控制电路802可以具有相同的电路结构,或者具有不同的电路结构。

110.示例性地,参考图28,在拍摄阶段,第五源极端so5和第六源极端so6分别输出电性相反的信号,从而第三连接线73和第四连接线74分别施加电性相反的信号,进一步地,位于同一第一子像素行的相邻两个第一电极21分别施加电性相反的信号。第五源极端so5和第六源极端so6输出的信号可以为随帧翻转的数据电压信号,从而位于同一第一子像素行的相邻两个第一电极21分别施加电性相反的数据电压信号,第一电极21与第二电极22之间夹压的相性随帧反转。需要说明的是,拍摄阶段的一帧指的是为所有第一电极21和第二电极

22完成一次完整充电的时间。

111.示例性地,参考图28,第一电源端vsp输出的电压大于第二电源端vsn输出的电压,例如第一电源端vsp输出的电压为+5v,第二电源端vsn输出的电压为

‑

5v。或者,第一电源端vsp输出的电压为+5.7v,第二电源端输出的电压为

‑

5.7v。公共电压端com输出公共电压,公共电压例如可以为0v。信号控制电路80(以信号控制电路80驱动第三连接线73为例)的工作过程包括:正电压输出过程,第一控制端cg1控制开关单元83导通,第二控制端cg2控制公共电压输入单元84截止,第五源极端so5控制第二电压输入单元82截止,第一电源端vsp输出的电信号由第一电压输入单元81的第一端传输到开关单元83的第一端,并经过开关单元83的第二端传输至第三连接线73。负电压输出过程,第一控制端cg1控制开关单元83导通,第二控制端cg2控制公共电压输入单元84截止,第五源极端so5控制第二电压输入单元82导通,第二电源端vsn输出的电信号由第二电压输入单元82的第一端传输到开关单元83的第一端,并经过开关单元83的第二端传输至第三连接线73。公共电压输出过程,第一控制端cg1控制开关单元83截止,第二控制端cg2控制公共电压输入单元84导通,公共电压端com输出的公共电压由公共电压输入单元84的第二端传输至第三连接线73。

112.图29为本发明实施例提供的另一种信号控制电路的电路示意图,参考图29,第一电压输入单元81包括第一电阻r1,第一电阻r1的第一端与第一电源端vsp电连接,第一电阻r1的第二端与开关单元83的第一端电连接。本发明实施例中,第一电压输入单元81包括第一电阻r1,第一电压输入单元81的结构简单,无需为第一电压输入单元81设置控制端,简化了信号控制电路80的电路结构。本发明实施例通过设置第一电阻r1,降低线路中电流,防止电流过大造成第一电源端vsp和第二电源端vsn之间导通时线路短路。如此,第一电阻r1的电阻可以大于1000欧姆。

113.图30为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图29和图30,显示面板还包括台阶区104,台阶区104位于显示区103的外围。显示面板还包括柔性电路板fpc,柔性电路板fpc绑定于台阶区104,第一电阻r1设置于柔性电路板fpc上。本发明实施例中,将第一电阻r1设置于柔性电路板fpc上,一方面,避免第一电阻r1占用台阶区104的空间。另一方面,便于对第一电阻r1进行更换,以实现对信号控制电路80的调试和维护。

114.示例性地,第一电阻r1的阻值大于或者等于100000欧姆且小于或者等于1000000欧姆。

115.图31为本发明实施例提供的另一种信号控制电路的电路示意图,参考图31,第一电压输入单元81包括第一晶体管t1,第一晶体管t1的栅极与源极端so(以第五源极端so5为例)电连接,第一晶体管t1的第一极与第一电源端vsp电连接,第一晶体管t1的第二极与开关单元83的第一端电连接。本发明实施例中,第一电压输入单元81包括第一晶体管t1,第一晶体管t1的栅极和第二电压输入单元82的控制端均与源极端so电连接,第一晶体管t1导通时,第二电压输入单元82截止,第一电源端vsp输出的电信号经过第一晶体管t1传输至开关单元83的第一端。第一晶体管t1截止时,第二电压输入单元82导通,第二电源端vsn输出的电信号经过第二电压输入单元82传输至开关单元83的第一端。

116.图32为本发明实施例提供的另一种信号控制电路的电路示意图,参考图32,第二电压输入单元82包括第二晶体管t2,第二晶体管t2的栅极与源极端so(以第五源极端so5为例)电连接,第二晶体管t2的第一极与开关单元83的第一端电连接,第二晶体管t2的第二极

与第二电源端vsn电连接。本发明实施例中,源极端so为第二晶体管t2的栅极施加有效电平时,控制第二晶体管t2导通,第二电源端vsn输出的电信号经过第二晶体管t2传输至开关单元83的第一端。

117.图33为本发明实施例提供的另一种信号控制电路的电路示意图,参考图33,开关单元83包括第三晶体管t3,第三晶体管t3的栅极与第一控制端cg1电连接,第三晶体管t3的第一极与第一电压输入单元81的第二端电连接,第三晶体管t3的第一极与第二电压输入单元82的第二端电连接,第三晶体管t3的第二极与第三连接线73或者第四连接线74(以信号控制电路80驱动第三连接线73为例)电连接。本发明实施例中,第一控制端cg1为第三晶体管t3的栅极施加有效电平时,控制第三晶体管t3导通,第一电源端vsp输出的电信号或者第二电源端vsn输出的电信号经过第三晶体管t3传输至第三连接线73或者第四连接线74。

118.图34为本发明实施例提供的另一种信号控制电路的电路示意图,参考图34,公共电压输入单元84包括第四晶体管t4,第四晶体管t4的栅极与第二控制端cg2电连接,第四晶体管t4的第一极与开关单元83的第二端电连接,第四晶体管t4的第二极与公共电压端com电连接。本发明实施例中,第二控制端cg2为第四晶体管t4的栅极施加有效电平时,控制第四晶体管t4导通,公共电压端com输出的公共电压经过第四晶体管t4传输至第三连接线73或者第四连接线74。

119.示例性地,参考图34,第三晶体管t3和第四晶体管t4均为n型晶体管。在拍摄阶段,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,向第二控制端cg2施加第二电平,控制第四晶体管t4截止。在显示阶段,向第一控制端cg1施加第二电平,控制第三晶体管t3截止,向第二控制端cg2施加第一电平,控制第四晶体管t4导通。其中,第一电平大于第二电平,相对而言,第一电平为高电平,第二电平为低电平。本发明实施例中,在拍摄阶段,向第一控制端cg1施加高电平,向第二控制端cg2施加低电平,控制第三晶体管t3导通,控制第四晶体管t4截止。在显示阶段,向第一控制端cg1施加低电平,向第二控制端cg2施加高电平,控制第三晶体管t3截止,控制第四晶体管t4导通。

120.在另一实施方式中,第三晶体管t3和第四晶体管t4还可以均为p型晶体管。在拍摄阶段,向第一控制端cg1施加第二电平,控制第三晶体管t3导通,向第二控制端cg2施加第一电平,控制第四晶体管t4截止。在显示阶段,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,向第二控制端cg2施加第二电平,控制第四晶体管t4截止。其中,第一电平大于第二电平,相对而言,第一电平为高电平,第二电平为低电平。

121.图35为本发明实施例提供的另一种信号控制电路的电路示意图,参考图35,第三晶体管t3为n型晶体管,第四晶体管t4为p型晶体管,或者,第三晶体管t3为p型晶体管,第四晶体管t4为n型晶体管。第一控制端cg1与第二控制端cg2电连接。本发明实施例中,第三晶体管t3和第四晶体管t4中的一个为p型晶体管,另一个为n型晶体管,第一控制端cg1与第二控制端cg2电连接,从而第一控制端cg1和第二控制端cg2可以合并为一个端口,减少了对驱动芯片ic上端口的占用。

122.可选地,参考图35,第三晶体管t3为n型晶体管,第四晶体管t4为p型晶体管时。在拍摄阶段,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,以及控制第四晶体管t4截止,第一电源端vsp输出的电信号或者第二电源端vsn输出的电信号经过第三晶体管t3传输至第三连接线73或者第四连接线74。在显示阶段,向第一控制端cg1施加第二电平,控

制第三晶体管t3截止,以及控制第四晶体管t4导通,公共电压端com输出的公共电压经过第四晶体管t4传输至第三连接线73或者第四连接线74。其中,第一电平大于第二电平,相对而言,第一电平为高电平,第二电平为低电平。

123.在另一实施方式中,第三晶体管t3还可以为p型晶体管,第四晶体管t4还可以为n型晶体管,第一控制端cg1与第二控制端cg2电连接。此时,在拍摄阶段,向第一控制端cg1施加第二电平,控制第三晶体管t3导通,以及控制第四晶体管t4截止。在显示阶段,向第一控制端cg1施加第一电平,控制第三晶体管t3截止,以及控制第四晶体管t4导通。其中,第一电平大于第二电平,相对而言,第一电平为高电平,第二电平为低电平。

124.示例性地,参考图32

‑

图35中的任意一幅,第一晶体管t1的栅极与第二晶体管t2的栅极均与同一个源极端so电连接。第一晶体管t1为p型晶体管,第二晶体管t2为n型晶体管。在其他实施方式中,第一晶体管t1还可以为n型晶体管,第二晶体管t2还可以为p型晶体管。

125.图36为本发明实施例提供的另一种信号控制电路的电路示意图,参考图36,第一电压输入单元81包括第一电阻r1。第一电阻r1的第一端与第一电源端vsp电连接,第一电阻r1的第二端与开关单元83的第一端电连接。第二晶体管t2、第三晶体管t3和第四晶体管t4均为n型晶体管。在其他实施方式中,第二晶体管t2、第三晶体管t3和第四晶体管t4还可以均为p型晶体管。本发明实施例中,第二晶体管t2、第三晶体管t3和第四晶体管t4具有相同的类型,信号控制电路80中所有晶体管具有相同的类型,从而可以采用同种材料以及相同的膜层工艺形成信号控制电路80中所有晶体管,降低了信号控制电路80的工艺难度。

126.示例性地,参考图35,信号控制电路80(以信号控制电路80驱动第三连接线73为例)的工作过程包括:在拍摄阶段,正电压输出过程中,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,以及控制第四晶体管t4截止。向第五源极端so5施加第二电平,控制第一晶体管t1导通,以及控制第二晶体管t2截止。第一电源端vsp输出的电信号由第一晶体管t1的第一极传输到第三晶体管t3的第一极,并经过第三晶体管t3的第二极传输至第三连接线73。在拍摄阶段,负电压输出过程中,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,以及控制第四晶体管t4截止。向第五源极端so5施加第一电平,控制第一晶体管t1截止,以及控制第二晶体管t2导通。第二电源端vsn输出的电信号由第二晶体管t2的第一极传输到第三晶体管t3的第一极,并经过第三晶体管t3的第二极传输至第三连接线73。在显示阶段,向第一控制端cg1施加第二电平,控制第三晶体管t3截止,以及控制第四晶体管t4导通。公共电压端com输出的公共电压由第四晶体管t4的第二极传输至第三连接线73。

127.示例性地,参考图36,信号控制电路80(以信号控制电路80驱动第三连接线73为例)的工作过程包括:在拍摄阶段,正电压输出过程中,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,向第二控制端cg2施加第二电平,控制第四晶体管t4截止。向第五源极端so5施加第二电平,控制第二晶体管t2截止。第一电源端vsp输出的电信号由第一电阻r1的第一端传输到第三晶体管t3的第一极,并经过第三晶体管t3的第二极传输至第三连接线73。在拍摄阶段,负电压输出过程中,向第一控制端cg1施加第一电平,控制第三晶体管t3导通,向第二控制端cg2施加第二电平,控制第四晶体管t4截止。向第五源极端so5施加第一电平,控制第二晶体管t2导通。第二电源端vsn输出的电信号由第二晶体管t2的第一极传输到第三晶体管t3的第一极,并经过第三晶体管t3的第二极传输至第三连接线73。需要说明的是,由于第一电源端vsp输出的电信号经过第一电阻r1后才传导至第三晶体管t3的第一

极,而第二电源端vsn输出的电信号无需经过电阻就可以到达第三晶体管t3的第一极,第三晶体管t3的第一极的电压表现为第二电源端vsn输出的电信号的电压。在显示阶段,向第一控制端cg1施加第二电平,控制第三晶体管t3截止,向第二控制端cg2施加第一电平,控制第四晶体管t4导通。公共电压端com输出的公共电压由第四晶体管t4的第二极传输至第三连接线73。

128.继续参考图27,信号控制电路80位于台阶区104。从而信号控制电路80不会占用显示区103的空间,不会降低显示面板的屏占比。另一方面,信号控制电路80位于台阶区104,信号控制电路80与驱动芯片ic的距离较近,便于信号控制电路80与驱动芯片ic的第一控制端cg1、第二控制端cg2以及源极端so电连接。

129.示例性地,参考图27,驱动芯片ic位于台阶区104,即,驱动芯片ic绑定于显示面板的台阶区104。在其他实施方式中,驱动芯片ic还可以位于柔性电路板fpc上,并将柔性电路板fpc绑定于台阶区104,驱动芯片ic通过柔性电路板fpc与显示面板中的其他电路部分电连接。

130.图37为本发明实施例提供的另一种第一电极和第二电极施加电信号的示意图,参考图37,第一显示区101包括至少一个第一子像素行(图37中以一个第一子像素行为例进行示意),第一子像素行包括沿第二方向排布的多个第一子像素11,第一方向与第二方向的夹角大于或者等于0

°

且小于90

°

。在拍摄阶段,同一个电极组20中,位于同一第一子像素行中相邻的第一电极21和第二电极22分别施加电性相反的第三信号。

131.示例性地,参考图37,沿第一方向,第一电极21和第二电极22一一间隔排布。在拍摄阶段,依次为多个第一电极21和多个第二电极22施加的电信号为:正性的第三信号s3+、负性的第三信号s3

‑

、正性的第三信号s3+、和负性的第三信号s3

‑

。施加正性的第三信号s3+的第一电极21与施加负性的第三信号s3

‑

的第二电极22之间形成水平电场。

132.可选地,第三信号包括数据电压信号。其中,数据电压信号为在拍摄阶段经过多路选择器处理后的电压信号。

133.图38为本发明实施例提供的另一种显示面板的俯视结构示意图,图39为沿图38中cc’的剖面结构示意图,参考图38和图39,显示面板还包括台阶区104和多路选择器43,台阶区104位于显示区103的外围,多路选择器43位于台阶区104。显示面板还包括第五连接线75和第六连接线76,第五连接线75与第一电极21电连接,第六连接线76与第二电极22电连接。在拍摄阶段,第五连接线75上的第三信号与第六连接线76上的第三信号电性相反。第五连接线75和第六连接线76均与多路选择器43电连接。本发明实施例中,第五连接线75和第六连接线76均与多路选择器43电连接。在拍摄阶段,第五连接线75与第六连接线76分别施加电性相反的第三信号,从而,位于同一电极组20中的第一电极21和第二电极22分别施加电性相反的数据电压信号。在显示阶段,可以为同一个电极组20内的第一电极21与第二电极22中的一个提供公共电压,另一个提供像素电压。

134.示例性地,参考图38,在显示阶段,为第一电极21提供像素电压,为第二电极22提供公共电压。第一显示区101还包括多个第三子像素13,第一子像素11透过率大于第三子像素13的透过率。多个第三子像素13包括沿第二方向排列的红色子像素、绿色子像素和蓝色子像素。为第一电极21提供的像素电压可以根据与第一电极21相邻的红色子像素和绿色子像素的显示数据进行调整,或者,根据与第一电极21相邻的蓝色子像素和红色子像素的显

示数据进行调整,或者,根据与第一电极21相邻的绿色子像素和蓝色子像素的显示数据进行调整。

135.可选地,参考图38和图39,第一显示区101还包括多个第三子像素13,第一子像素11透过率大于第三子像素13的透过率。第一子像素11为第一显示区101内的高透子像素,具有较高的透过率,用于透过摄像光线。第三子像素13为第一显示区101内的显示子像素,用于图像显示。沿第二方向,第一子像素11的宽度为w1。沿第二方向,第三子像素13的宽度为w2。w1小于或者等于w2。同一个电极组20内的第一电极21与第二电极22之间间隔两个第一子像素11。本发明实施例中,一个第一子像素11包括第一电极21,另一个第一子像素11包括第二电极22,同一个电极组20内的第一电极21与第二电极22占据两个第一子像素11。可以理解的是,在第一电极21的电压与第二电极22的电压差值固定的情况下,第一电极21与第二电极22的距离越远,则第一电极21与第二电极22形成的电场强度越小,第一电极21与第二电极22的距离越近,则第一电极21与第二电极22形成的电场强度越大。同一个电极组20内的第一电极21与第二电极22占据两个第一子像素11,第一电极21与第二电极22的距离较近,则第一电极21与第二电极22形成的电场强度较大,对液晶分子的驱动能力较强。需要进一步说明的是,在第二方向上,第一子像素11的宽度大于第三子像素13的宽度,可以提高第一子像素11在第一显示区101中的面积占比,提高第一显示区101的光线透过率。

136.图40为本发明实施例提供的另一种显示面板的剖面结构示意图,参考图40,第一显示区101和第二显示区102均包括开口区111和围绕开口区111的非开口区112。显示面板包括阵列基板40、对置基板50和液晶层60,液晶层60位于阵列基板40和对置基板50之间,对置基板50包括遮光层51,遮光层51在显示面板的出光面上的正投影覆盖非开口区112。第一显示区101中,开口区111与沿第二方向排列的两个第一子像素11交叠。本发明实施例中,第一子像素行中,沿第二方向排列的两个第一子像素11之间的区域不设置遮光层51,从而增加第一显示区101的透光面积,提高了第一显示区101的透过率。

137.图41为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图41,沿第二方向(以第一方向平行于第二方向为例,实际上,第一电极21和第二电极22沿着第一方向进行排列),第一电极21和第二电极22一一间隔排布。显示面板还包括多条数据线48,多条数据线48中的至少部分位于第一显示区101。多条数据线48沿第二方向排布。数据线48还可以沿第三方向延伸。第一电极21与数据线48电连接,第二电极22与数据线48电连接。第一电极21以及相邻电极组20中的第二电极22与同一条数据线48电连接,第二电极22以及相邻电极组20中的第一电极21与同一条数据线48电连接。在拍摄阶段,沿第二方向,相邻的数据线48分别施加电性相反的第三信号。本发明实施例中,第一电极21以及第二电极22均与数据线48电连接,数据线48复用为第一电极21和第二电极22的连接线,从而可以通过显示面板中原有的数据线48为第一电极21和第二电极22提供电信号。在拍摄阶段,沿第二方向,相邻的数据线48分别施加电性相反的第三信号,从而,位于同一电极组20中的第一电极21和第二电极22分别施加电性相反的数据电压信号。在显示阶段,可以为同一个电极组20内的第一电极21与第二电极22中的一个提供公共电压,另一个提供像素电压。

138.示例性地,参考图41,在显示阶段,为第一电极21提供像素电压,为第二电极22提供公共电压。第一显示区101还包括多个第三子像素13,第一子像素11透过率大于第三子像素13的透过率。多个第三子像素13包括沿第二方向排列的红色子像素、绿色子像素和蓝色

子像素。为第一电极21提供的像素电压可以根据与第一电极21相邻的红色子像素和绿色子像素的显示数据进行调整,或者,根据与第一电极21相邻的蓝色子像素和红色子像素的显示数据进行调整,或者,根据与第一电极21相邻的绿色子像素和蓝色子像素的显示数据进行调整。

139.可选地,参考图41,第二显示区102包括多个第二子像素12,第二子像素12包括像素电极122。显示面板还包括多条扫描线45、第三开关管463和第四开关管464。扫描线45沿第二方向延伸。多条扫描线45包括第一扫描线451和第二扫描线452。第一扫描线451至少部分位于第一显示区101,第二扫描线452位于第一显示区101。第三开关管463的栅极与第一扫描线451电连接,第三开关管463的第一极与数据线48电连接。第三开关管463的第二极与第一电极21或者像素电极122电连接。具体地,第一子像素11所对应的第三开关管463的第二极与第一电极21电连接,第二子像素12以及第三子像素13所对应的第三开关管463的第二极均与像素电极122电连接。第四开关管464的栅极与第二扫描线452电连接,第四开关管464的第一极与数据线48电连接,第四开关管464的第二极与第二电极22电连接。本发明实施例中,第一电极21通过第三开关管463与数据线48电连接。第二电极22通过第四开关管464与数据线48电连接。在拍摄阶段,第一扫描线451提供的有效电平,将第三开关管463导通,数据线48为第一电极21提供正性的第三信号s3+,或者,数据线48为第一电极21提供负的第三信号s3

‑

。按照逐行扫描的方式,在第一扫描线451提供有效电平之后,第二扫描线452提供的有效电平,将第四开关管464导通,数据线48为第二电极22提供负的第三信号s3

‑

,或者,数据线48为第二电极22提供正性的第三信号s3+。

140.需要说明的是,在拍摄阶段,第二显示区102中的数据线48无需提供数据电压信号。在显示阶段,第一扫描线451提供的有效电平,将第三开关管463导通,第一显示区101内的数据线48为第一电极21提供像素电压,第二显示区102内的数据线48为像素电极122提供像素电压。其中,为第一电极21提供像素电压可以为固定值,也可以根据第二子像素12和/或第三子像素13的像素电压做调整,以将第一子像素11的发光亮度与其周围第二子像素12和/或第三子像素13的发光亮度相适配,避免色淡。按照逐行扫描的方式,在第一扫描线451提供有效电平之后,第二扫描线452提供的有效电平,将第四开关管464导通,第一显示区101内的数据线48为第二电极22提供公共电压。

141.可选地,参考图41,在拍摄阶段,向第一扫描线451施加扫描导通信号(即有效电平),将第三开关管463导通,向数据线48施加第一拍摄电压。向第二扫描线452施加扫描导通信号,将第四开关管464导通,向数据线48施加第二拍摄电压。其中,第一拍摄电压和第二拍摄电压的绝对值相等且电性相反。

142.示例性地,参考图41,在当前帧中,在拍摄阶段,第一扫描线451提供的有效电平,将第三开关管463导通,数据线48为第一电极21提供的电压为5.7v。之后,第二扫描线452提供的有效电平,将第四开关管464导通,数据线48为第二电极22提供的电压为

‑

5.7v。在下一帧中,在拍摄阶段,第一扫描线451提供的有效电平,将第三开关管463导通,数据线48为第一电极21提供的电压为

‑

5.7v。之后,第二扫描线452提供的有效电平,将第四开关管464导通,数据线48为第二电极22提供的电压为5.7v。

143.示例性地,数据线48与多路选择器43(图41中未示出)电连接,并通过多路选择器43的六个连接端对应连接于驱动芯片ic(图41中)中的两个源极端so。

144.图42为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图42,显示面板还包括多个级联的移位寄存器vsr,移位寄存器vsr与扫描线45电连接,用于为扫描线45提供有效电平。其中,像素驱动电路中与扫描线45电连接的晶体管采用p型晶体管时,扫描线45上的有效电平为低电平,像素驱动电路中与扫描线45电连接的晶体管采用n型晶体管时,扫描线45上的有效电平为高电平。像素驱动电路用于驱动子像素(包括第一子像素11、第二子像素12和第三子像素13)发光。移位寄存器vsr的数量等于第一扫描线451与第二扫描线452的数量之和。本发明实施例中,移位寄存器vsr与第一扫描线451或者第二扫描线452电连接,用于为第一扫描线451或者第二扫描线452提供有效电平。除与第一扫描线451电连接的移位寄存器vsr外,还增设了与第二扫描线452电连接的移位寄存器vsr,且各移位寄存器vsr依次级联,实现了多个扫描线45的逐条扫描。

145.示例性地,第二子像素12和第三子像素13均用于发光显示,为可视彩色子像素,第一子像素11用于透过外界环境光,不是彩色可视子像素。另一方面,第一子像素11还可以作为白色可视子像素,用于提升显示阶段的显示亮度。显示面板包括2400行彩色可视子像素。第一显示区101对应于第m行至第m+60行彩色可视子像素,其中,m为正整数。则在第m+1行至第m+60行彩色可视子像素的子像素行中,需要设置120个移位寄存器vsr,其中的60个移位寄存器vsr需要与第一显示区101中的第二扫描线452电连接。

146.示例性地,参考图42,显示面板包括显示区103和非显示区105,其中,非显示区105包括台阶区104。移位寄存器vsr位于非显示区105中台阶区104之外的区域中。

147.图43为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图43,显示面板还包括第七连接线77和第八连接线78,第七连接线77与第一电极21电连接,第八连接线78与第二电极22电连接。在拍摄阶段,第七连接线77上的第三信号与第八连接线78上的第三信号电性相反。第七连接线77的输入端和第八连接线78的输入端均与驱动芯片ic电连接。本发明实施例中,第七连接线77的输入端和第八连接线78的输入端均与驱动芯片ic电连接,在拍摄阶段,第七连接线77和第八连接线78分别施加电性相反的第三信号,从而,位于同一电极组20中的第一电极21和第二电极22分别施加电性相反的第三信号。

148.图44为本发明实施例提供的另一种显示面板的俯视结构示意图,图45为沿图44中dd’的剖面结构示意图,参考图44和图45,第七连接线77包括首尾连接的第一子线段771和第二子线段772。第一子线段771沿第三方向延伸,第一子线段771可以位于第二方向上排列的相邻子像素之间,或者位于子像素列的一侧。第二子线段772沿第一方向延伸,第二子线段772可以位于沿第三方向上排列的相邻子像素之间,或者位于子像素行(包括第一子像素行)的一侧。第三方向与第一方向交叉。第八连接线78包括首尾连接的第三子线段781和第四子线段782,第三子线段781沿第三方向延伸,第三子线段781可以位于第二方向上排列的相邻子像素之间,或者位于子像素列的一侧。第四子线段782沿第一方向延伸。第四子线段782可以位于沿第三方向上排列的相邻子像素之间,或者位于子像素行(包括第一子像素行)的一侧。本发明实施例中,第七连接线77和第八连接线78均呈“弓”字型,从而仅需一条第七连接线77便可以连接所有的第一电极21,仅需一条第八连接线78便可以连接所有的第二电极22,减少了连接线的数量,从而增加第一显示区101的透光面积,提高了第一显示区101的透过率。

149.可选地,第二子线段772和第四子线段782交叠,但为了清晰地示意出第二子线段

772和第四子线段782,将相互交叠的第二子线段772和第四子线段782在各附图中错开一定的距离进行示意。参考图44和图45,第二显示区102包括多个第二子像素12,第二子像素12包括公共电极121和像素电极122。第一子线段771、第三子线段781、第四子线段782与像素电极122同层设置。第二子线段772包括第一次子线段7721、第二次子线段7722和跨桥7723,跨桥7723连接第一次子线段7721和第二次子线段7722,第一次子线段7721和第二次子线段7722均与像素电极122同层,第一次子线段7721和第二次子线段7722均不与第四子线段782交叠。跨桥7723与公共电极121同层,跨桥7723与第四子线段782交叠。本发明实施例中,在第二子线段772和第四子线段782交叠的位置处,为第二子线段772设置跨桥7723,跨桥7723与第四子线段782异层交叠,从而避免了第二子线段772与第四子线段782的电性连接,继而避免了第七连接线77与第八连接线78的电性连接。

150.图46为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图46,第七连接线77的输出端与第一侦测电压端91电连接,第八连接线78的输出端与第二侦测电压端92电连接。在检测阶段,向第七连接线77的输入端in和第八连接线78的输入端in均施加检测电压信号,通过第一侦测电压端91侦测第七连接线77上的检测电压信号,以判断第七连接线77是否断路,以及通过第二侦测电压端92侦测第八连接线78上的检测电压信号,以判断第八连接线78是否断路。本发明实施例中,第七连接线77的输出端与第一侦测电压端91电连接,第八连接线78的输出端与第二侦测电压端92电连接,从而在绑定驱动芯片ic之前,可以先通过第一侦测电压端91来判断第七连接线77是否断路,例如在第一侦测电压端91侦测到的电压值小于第一预设值或者无法侦测到电压时,确定第七连接线77断路。在第一侦测电压端91侦测到的电压值大于或者等于第一预设值或者可以侦测到电压值时,确定第七连接线77未发生断路。类似地,通过第二侦测电压端92来判断第八连接线78是否断路,例如在第二侦测电压端92侦测到的电压值小于第一预设值或者无法侦测到电压时,确定第八连接线78断路。在第二侦测电压端92侦测到的电压值大于或者等于第一预设值或者可以侦测到电压值时,确定第八连接线78未发生断路。故而,第七连接线77和第八连接线78发生断路时,可以被第一侦测电压端91和第二侦测电压端92提前侦测,以避免在次品的显示面板上绑定驱动芯片ic情况的发生,节省了成本。

151.示例性地,参考图44和图46中的任意一幅,同一个第一子像素行中,相邻两个电极组20之间间隔一个第一子像素11,即,每间隔一个第一子像素11设置一个电极组20。

152.示例性地,参考图6,显示面板在第一显示区101还设置有多个凸台30,凸台30的第一侧面301和第二侧面302为第一电极21和第二电极22提供了倾斜表面,第一电极21和第二电极22分别设置于凸台30的第一侧面301和第二侧面302上,第一电极21和第二电极22存在一定的断线风险。即,在凸台30侧面形成的第一电极21和第二电极22时,由于工艺的限制,存在断路风险。继续参考图46,在绑定驱动芯片ic之前,以及确定第七连接线77和第八连接线78未发生断路之后,可以先通过第一侦测电压端91来判断第一电极21是否断路,通过第二侦测电压端92来判断第二电极22是否断路。示例性地,在第一侦测电压端91侦测到的电压值大于第二预设值时,确定连接至第七连接线77的第一电极21中,存在至少一个第一电极21发生断路。其中,第二预设值大于第一预设值。在第一侦测电压端91侦测到的电压值大于或者等于第一预设值且小于或者等于第二预设值时,确定连接至第七连接线77的第一电极21未发生断路。类似的,在第二侦测电压端92侦测到的电压值大于第二预设值时,确定连

接至第八连接线78的第二电极22中,存在至少一个第二电极22发生断路。在第二侦测电压端92侦测到的电压值大于或者等于第一预设值且小于或者等于第二预设值时,确定连接至第八连接线78的第二电极22未发生断路。

153.图47为本发明实施例提供的另一种显示面板的俯视结构示意图,参考图47,任一第一子像素11包括第一电极21和第二电极22。沿第二方向,任意两个相邻第一子像素11之间设置第一子线段771和第三子线段781。沿第三方向,任意一列第一子像素11的端部设置第二子线段772和第四子线段782。第七连接线77呈“弓”字型,一条第七连接线77连接所有的第一电极21。第八连接线78呈“弓”字型,一条第八连接线78连接所有的第二电极22。

154.示例性地,参考图44和图47中的任意一幅,第一电极21通过第七连接线77与第三源极端so3电连接,第三源极端so3将电压信号施加到第七连接线77上,进而施加到第一电极21上。第二电极22通过第八连接线78与第四源极端so4电连接,第四源极端so4将电压信号施加到第八连接线78上,进而施加到第二电极22上。

155.需要说明的是,在另一实施方式中,第七连接线77和第八连接线78还可以与信号控制电路80电连接,采用信号控制电路80来驱动第七连接线77和第八连接线78,信号控制电路80为专门设置的驱动电路,信号控制电路80的驱动能力比较强,从而提高了对第七连接线77和第八连接线78的驱动能力。

156.本发明实施例还提供了一种显示装置。图48为本发明实施例提供的一种显示装置的结构示意图,参考图48,显示装置包括本发明实施例提供的任意一种显示面板。显示装置具体可以为手机、平板电脑、车载显示装置以及智能可穿戴设备等。

157.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整、相互结合和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1