Lvds多对接收装置及Lvds多对发送装置的制作方法

lvds多对接收装置及lvds多对发送装置

【技术领域】

1.本发明涉及集成电路芯片技术领域,尤其涉及一种lvds多对接收装置及lvds多对发送装置。

背景技术:

2.当前主流的lvds传输系统的传输速率较低。多通道的lvds数据只能以固定的顺序进行传输,使得个人计算机(personal computer,pc)端可能需要进行一定的排序,这样会延长pc端的数据处理时间,效率大大降低。

技术实现要素:

3.本发明的目的在于提供了一种lvds多对接收装置。

4.为达到上述目的,本发明提供了一种lvds多对接收装置,包括差分转单端模块,信号延时模块,高速io时钟驱动模块,高速io时钟分频模块,串并转换模块;

5.所述差分转单端模块,用于接收lvds差分时钟并转换为单端时钟信号;

6.所述信号延时模块,用于接收所述单端时钟信号并进行动态或者静态延时调整生成延时调整信号;

7.所述高速io时钟驱动模块,用于接收所述延时调整信号并提供高速时钟;

8.所述高速io时钟分频模块,用于接收所述高速时钟并提供低速时钟;

9.所述串并转换模块,用于将接收的多对数据转换为并行数据。

10.优选的,还包括位调整和字节对齐模块;

11.所述位调整和字节对齐模块,用于根据特殊数据和校准字节比较生成延时调整信号并发送至所述信号延时模块。

12.本发明还提供了一种lvds多对发送装置,包括pll时钟模块,高速io时钟驱动模块,高速io时钟分频模块,数据生成模块,并串转换模块,单端信号转化为差分信号模块;

13.pll时钟模块,用于生成采样的时钟信号;

14.高速io时钟驱动模块,用于接收所述时钟信号并提供高速时钟;

15.高速io时钟分频模块,用于接收所述高速时钟并提供低速时钟;

16.数据生成模块,用于生成并行数据并发送至所述并串转换模块;

17.并串转换模块,用于将接收所述并行数据转换为串行数据;

18.单端信号转化为差分信号模块,用于接收所述串行数据并转换为lvds信号。

19.本发明的有益效果在于:lvds多对发送装置和lvds多对接收装置具有高速的io时钟,提高传输效率。

【附图说明】

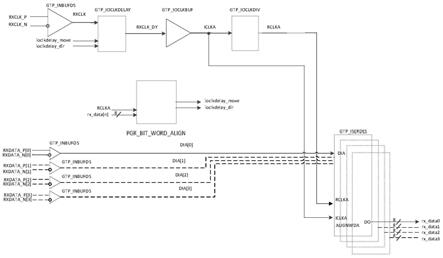

20.图1为本发明实施例lvds多对接收装置的结构图;

21.图2为本发明实施例lvds多对发送装置的结构图。

【具体实施方式】

22.为使本说明书的目的、技术方案和优点更加清楚,下面将结合本说明书具体实施例及相应的附图对本说明书技术方案进行清楚、完整地描述。显然,所描述的实施例仅是本说明书一部分实施例,而不是全部的实施例。基于本说明书中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本说明书保护的范围。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。

23.本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”和“第三”等是用于区别不同对象,而非用于描述特定顺序。此外,术语“包括”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

24.本发明提供一种lvds(low voltage differential signaling,低电压差分信号)多对接收装置,包括差分转单端模块,信号延时模块,高速io时钟驱动模块,高速io时钟分频模块,串并转换模块。

25.所述差分转单端模块,用于接收lvds差分时钟并转换为单端时钟信号;

26.所述信号延时模块,用于接收所述单端时钟信号并进行动态或者静态延时调整生成延时调整信号;

27.所述高速io时钟驱动模块,用于接收所述延时调整信号并提供高速时钟;

28.所述高速io时钟分频模块,用于接收所述高速时钟并提供低速时钟;

29.所述串并转换模块,用于将接收的多对数据转换为并行数据。

30.在其中一个实施例中,如图1所示,lvds多对接收装置,包括差分转单端模块,信号延时模块gtp_ioclkdelay,高速io时钟驱动模块gtp_ioclkbuf,高速io时钟分频模块gtp_ioclkdiv,串并转换模块。

31.所述差分转单端模块,用于接收lvds差分信号并转换为单端信号;

32.所述信号延时模块gtp_ioclkdelay,用于接收所述单端信号并进行动态或者静态延时调整生成延时调整信号rxclk_dy;

33.所述高速io时钟驱动模块gtp_ioclkbuf,用于接收所述延时调整信号rxclk_dy并提供高速时钟iclka;

34.所述高速io时钟分频模块gtp_ioclkdiv,用于接收所述高速时钟iclka并提供低速时钟rclka;

35.所述串并转换模块,用于将接收的多对数据转换为并行数据。

36.本发明实施例的lvds多对接收装置,差分时钟rxclk_p\rxclk_n经差分转单端模块转换为单端时钟信号rxclk,再经高速io时钟驱动模块gtp_ioclkbuf生成延时调整后的信号延时调整信号rxclk_dy,延时调整信号rxclk_dy经高速io时钟驱动模块gtp_ioclkbuf生成高速时钟iclka提供给串并转换模块作为其高速时钟,同时,高速时钟iclka经高速io时钟分频模块gtp_ioclkdiv分频后的低速时钟rclka提供给串并转换模块作为其低速时钟,串并转换模块,将接收的多对数据转换为并行数据。

37.具体的,串并转换模块根据高速时钟iclka采样多对数据,并在低速时钟rclka的低频时钟域下转换为系统并行数据。

38.在其中一个实施例中,lvds多对接收装置还包括位调整和字节对齐模块pgr_bit_word_align。

39.所述位调整和字节对齐模块pgr_bit_word_align,通过接收rx_data数据和模块中定义的标准数据进行比较,生成延时调整信号ioclkdelay_move、ioclkdelay_dir并发送至所述信号延时模块gtp_ioclkdelay进行动态调整。

40.具体的,信号延时模块gtp_ioclkdelay在进行延时调整时,位调整和字节对齐模块pgr_bit_word_align采集rx_data中传递的特殊数据和模块中定义的标准数据进行比较,生成延时调整信号ioclkdelay_move、ioclkdelay_dir传递给延时模块gtp_ioclkdelay动态调整,直到调整到数据接收正确。

41.在其中一个实施例中,差分转单端模块包括若干差分转单端子模块,其中,一差分转单端子模块gtp_inbufds用于将差分时钟rxclk_p\rxclk_n经转换为单端时钟信号rxclk,其余差分转单端子模块gtp_inbufds用于将多对数据转换为多个单端数据。

42.串并转换模块包括若干串并转换子模块gtp_iserdes,串并转换子模块gtp_iserdes将接收的多个单端数据转换为并行数据。

43.串并转换子模块gtp_iserdes为4个、7个或8个,以实现lvds多对接收装置支持1:4,1:7,1:8的比例因子。具体的,通过设置串并转换子模块gtp_iserdes的模式参数配置以选择不同的比例因子。

44.在其中一个实施例中,如图1所示,lvds多对接收装置,包括5个差分转单端子模块gtp_inbufds,信号延时模块gtp_ioclkdelay,高速io时钟驱动模块gtp_ioclkbuf,高速io时钟分频模块gtp_ioclkdiv,4个串并转换子模块gtp_iserdes。

45.1个差分转单端子模块gtp_inbufds,用于将差分时钟rxclk_p\rxclk_n经转换为单端时钟信号rxclk;其余4个差分转单端子模块gtp_inbufds,用于4对数据rxdata_p[0]与rxdata_n[0]、rxdata_p[1]与rxdata_n[1]、rxdata_p[2]与rxdata_n[2]、rxdata_p[3]与rxdata_n[3]转换为4个单端数据dia[0]、dia[1]、dia[2]、dia[3];

[0046]

所述信号延时模块gtp_ioclkdelay,用于接收所述单端信号并进行动态或者静态延时调整生成延时调整信号rxclk_dy;

[0047]

所述高速io时钟驱动模块gtp_ioclkbuf,用于接收所述延时调整信号rxclk_dy并提供高速时钟iclka;

[0048]

所述高速io时钟分频模块gtp_ioclkdiv,用于接收所述高速时钟iclka并提供低速时钟rclka;

[0049]

4个串并转换子模块gtp_iserdes与其余4个差分转单端子模块gtp_inbufds一一应对,4个串并转换子模块gtp_iserdes根据高速时钟iclka采样4个单端数据dia[0]、dia[1]、dia[2]、dia[3],并根据低速时钟rclka转换为并行数据rx_data0、rx_data1、rx_data2、rx_data3。

[0050]

其中图中,虚线表示有多个dia,4个串并转换子模块gtp_iserdes以堆叠结构表示,代表为多个相同的串并转换子模块gtp_iserdes。

[0051]

串并转换子模块gtp_iserdes的数据输入端dia用于接收单端数据dia[0]/dia[1]/dia[2]/dia[3],高频时钟端用于接收高速时钟iclka,低频时钟端用于接收低速时钟rclka,

[0052]

本发明另一实施例提供一种lvds多对发送装置,包括pll时钟模块,高速io时钟驱动模块,高速io时钟分频模块,数据生成模块,并串转换模块,单端信号转化为差分信号模块;

[0053]

pll时钟模块,用于生成采样的时钟信号;

[0054]

高速io时钟驱动模块,用于接收所述时钟信号并提供高速时钟;

[0055]

高速io时钟分频模块,用于接收所述高速时钟并提供低速时钟;

[0056]

数据生成模块,用于生成并行数据并发送至所述并串转换模块;

[0057]

并串转换模块,用于将接收所述并行数据转换为串行数据;

[0058]

单端信号转化为差分信号模块,用于接收所述串行数据并转换为lvds信号。

[0059]

在其中一个实施例中,并串转换模块包括5个并串转换子模块,单端信号转差分信号模块包括5个单端信号转差分信号子模块。

[0060]

如图2所示,lvds多对发送装置,包括pll时钟模块gtp_pll,高速io时钟驱动模块gtp_ioclkbuf,高速io时钟分频模块gtp_ioclkdiv,数据生成模块pgr_tdata_gen,5个并串转换子模块gtp_oserdes,5个单端信号转差分信号子模块gtp_outbufds。

[0061]

pll时钟模块gtp_pll,用于生成采样的时钟信号pll_clk;

[0062]

高速io时钟驱动模块gtp_ioclkbuf,用于接收所述时钟信号pll_clk并提供高速时钟oclka;

[0063]

高速io时钟分频模块gtp_ioclkdiv,用于接收所述高速时钟oclka并提供低速时钟rclka;

[0064]

数据生成模块pgr_tdata_gen,用于生成并行数据并发送至所述并串转换模块;

[0065]

并串转换模块,用于将接收所述并行数据转换为串行数据;

[0066]

单端信号转化为差分信号模块,用于接收所述串行数据并转换为lvds信号。

[0067]

本发明实施例的lvds多对发送装置,外部参考时钟ref_clk,经pll时钟模块gtp_pll生成采样的时钟信号pll_clk,时钟信号pll_clk经高速io时钟驱动模块生成高速时钟oclka提供给并串转换模块,同时,高速时钟oclka经高速io时钟分频模块gtp_ioclkdiv分频后生成低速时钟rclka提供给并串转换模块。

[0068]

具体的,所述数据生成模块pgr_tdata_gen的三个输入端分别接收注错信号force_err_n,发送端模式选择信号key_tx_mode_n,以及时钟信号rclka。

[0069]

其中,注错信号force_err_n,用于产生错误的数据信号;发送端模式选择信号key_tx_mode_n,用于选择不同的发送端数据模式;时钟信号rclka,用于驱动逻辑。

[0070]

1个并串转换子模块gtp_oserdes根据并串转换数据clk_pattern生成发送时钟doa_clk,发送时钟doa_clk经1个单端信号转差分信号子模块gtp_outbufds输出时钟差分信号tclk_p、tclk_n;其余4个并串转换子模块gtp_oserdes将数据生成模块pgr_tdata_gen生成的并行数据(有规律数据)tx_data转换为串行数据doa_dt,串行数据doa_dt经其余4个单端信号转差分信号子模块gtp_outbufds输出数据差分信号txdata_p、txdata_n。

[0071]

其中,其余4个并串转换子模块gtp_oserdes与其余4个单端信号转差分信号子模块gtp_outbufds一一对应。

[0072]

图中,虚线代表并行数据tx_data连接到多个并串转换子模块gtp_oserdes的di,采用堆叠结构代表有多个(其余4个)并串转换子模块gtp_oserdes和多个(其余4个)单端信

号转差分信号子模块gtp_outbufds。

[0073]

通过设置并串转换子模块gtp_oserdes的参数以选择不同的比例因子,本发明实施例的lvds多对发送装置支持4:1,7:1,8:1的比例因子。

[0074]

本发明实施例的lvds多对发送装置和lvds多对接收装置用于大数据传输或驱动高清液晶屏,具有高速的io时钟,提高传输效率。

[0075]

以上所述的仅是本发明的实施方式,在此应当指出,对于本领域的普通技术人员来说,在不脱离本发明创造构思的前提下,还可以做出改进,但这些均属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1