串行通信装置及在其中去除数据时钟偏斜的方法与流程

1.本技术涉及mipi d-phy相关技术领域,尤其是涉及一种串行通信装置及在串行通信装置中去除数据时钟偏斜的方法。

背景技术:

2.mipi(移动工业处理器接口)不仅是一个联盟,而且是一组接口协议规范的名称。它具有不同的工作组,以满足移动终端每个子系统的不同需求。不同的工作组负责制定特定的协议,并分别为不同硬件设备的移动设备定义一组内部接口标准,例如照相机串行接口(csi),显示串行接口(dsi),射频接口(digrf)等。d-phy是mipi协议之一。mipi d-phy提供在物理层上进行串行化信号传输的规范。

3.mipi d-phy协议定义了两种传输模式:高速模式(high speed,hs)和低功耗模式(low power,lp),两种模式使用不同的传输电平和传输机制。mipi d-phy协议支持最多5路传输通道(lane):时钟传输通道(clk lane)和四路独立数据传输通道(data lane),即,四个数据信号共用一个时钟信号。

4.由于mipi d-phy协议传输的信号在高速模式下相对于传统的tmds信号、lvds信号等,具有低电压摆幅,低功耗的优势,在低功耗模式下传输的信号速度较慢,较低的压摆不利于系统的稳定,因此通常,载荷数据(图像数据)使用高速模式,控制和状态信息的发送(在照相机/显示器和应用处理器之间)使用的是低功耗模式(利用低频信号)。因此在非连续模式下,信号传输在协议规定的参数范围内会进行低功耗模式和高速模式的切换,然而模拟时钟信号在从低功耗模式切换到高速模式过程中会产生毛刺(glitch),四路数据传输通道中的每一路接收包含不同毛刺的时钟信号,对自身传输的数据信号进行相应处理,并输出处理后的数据信号和处理后的时钟信号(word_clk),因而导致处理后的四路数据传输通道之间的数据信号和时钟信号存在偏斜(skew)。

技术实现要素:

5.有鉴于此,本公开实施例提供一种串行通信装置和一种在串行通信装置中去除数据时钟偏斜的方法,以解决现存的时钟偏斜。

6.根据本公开实施例的第一方面,提供一种串行通信装置,包括:mipid-phy物理层和其他层,所述mipi d-phy物理层包括:

7.时钟接收装置,用于从mipi d-phy物理层的串行链路的第一通道接收模拟的时钟信号,并经过处理后得到数字的初始时钟信号;

8.多个数据接收装置,每个数据接收装置从mipi d-phy物理层的串行链路的一个第二通道接收模拟的数据信号,从所述时钟接收装置获取所述初始时钟信号,经过处理后输出数字的数据信号及其对应的字时钟信号;

9.同步处理装置,用于对从所述多个数据接收装置接收到的多个数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差,其中,

多个校正后的有效数据和所述第一字时钟信号被提供给所述其他层,所述第一字时钟信号选自所述多个数据接收装置输出的多个字时钟信号。

10.在一些实施例中,所述同步处理装置包括:

11.控制信号生成电路,用于接收在所述初始时钟信号的时钟域产生的第一控制信号,并将第一控制信号同步到所述第一字时钟信号的时钟域以输出第二控制信号;

12.校准单元,用于从所述多个数据接收装置接收多个数据信号及其对应的字时钟信号,并基于所述第二控制信号对从所述多个数据接收装置的数据接收进行数据输入约束,并从接收到的多个数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与所述第一字时钟信号的相位偏差。

13.在一些实施例中,还包括:耦接在所述控制信号生成电路和所述校准单元之间的展宽电路,用于将所述第二控制信号展宽后输出给所述校准单元。

14.在一些实施例中,所述校准单元包括:

15.时钟域同步单元,用于先将从所述多个数据接收装置接收到的多个数据信号同步到各自对应的字时钟信号的时钟域,然后再同步到所述第一字时钟信号的时钟域;

16.时序控制单元,用于通过所述第二控制信号提供的数据输入约束对多个同步后的数据信号分别进行采样以得到多个采样信号;

17.偏差校正单元,用于分别将连续两个时钟周期的采样信号进行拼接以得到多个拼接信号,从多个拼接信号分别确定各自的有效数据的起点,并据此校正每个有效数据与所述第一字时钟信号的相位偏差。

18.在一些实施例中,在所述串行通信装置从低功耗模式切换到高速模式并保持设定时间后所述第一控制信号被拉高。

19.在一些实施例中,所述控制信号生成电路包括:

20.反相器,用于将所述第一字时钟信号反相,以得到第一反相字时钟信号;

21.第一采样电路,包括串联的n个第一d触发器,用于基于所述第一字时钟信号和所述第一反相字时钟信号对所述第一控制信号进行采样,并输出一个或多个第一采样信号;

22.第二采样电路,包括串联的n个第二d触发器,用于基于所述第一字时钟信号和所述第一反相字时钟信号对所述第一控制信号进行采样,并输出一个或多个第二采样信号;

23.逻辑运算单元,用于将所述一个或多个第一采样信号和所述一个或多个第二采样信号进行逻辑运算,以得到所述第二控制信号,n为大于1的整数。

24.在一些实施例中,所述第一采样电路包括三个第一d触发器,所述第二采样电路包括三个第二d触发器,

25.所述逻辑运算单元包括第一与门、第二与门和第一或门,所述第一与门的第一输入端耦接到所述三个第一d触发器的第二个第一d触发器的输出端,所述第一与门的第二输入端耦接到所述三个第二d触发器的第二个第二d触发器的输出端,

26.所述第二与门的第一输入端耦接到所述三个第一d触发器的第三个第一d触发器的输出端,所述第二与门的第二输入端耦接到所述三个第二d触发器的第三个第二d触发器的输出端,所述第一或门的两个输入端分别耦接到所述第一与门和所述第二与门的输出端。

27.在一些实施例中,所述展宽电路包括:串联的两个d触发器和第二或门,所述第二

或门的两个输入端分别耦接到所述两个d触发器的第一d触发器和第二d触发器的输出端。

28.在一些实施例中,所述时钟域同步单元包括:

29.第三采样电路,包括串联的第一d触发器和第二d触发器,所述第一d触发器的d端接收第一数据信号,clk端接收所述第一字时钟信号,所述第二d触发器的d端接收第一d触发器输出的数据信号,clk端接收所述第一字时钟信号;

30.至少一个第四采样电路,每个第四采样电路包括串联的第三d触发器和第四d触发器,所述第三d触发器的d端接收第二数据信号,clk端接收第二字时钟信号,所述第二d触发器的d端接收第三d触发器输出的数据信号,clk端接收所述第一字时钟信号。

31.在一些实施例中,所述时序控制单元包括:

32.多个门控单元,每个门控单元用于根据所述第二控制信号对数据接收进行数据输入约束;

33.多个d触发器,分别与所述多个门控单元耦接,每个d触发器接收与其耦接的门控单元输出的数据信号,并基于所述第一字时钟信号输出数据信号。

34.根据本公开实施例的第二方面,提供一种在串行通信装置中去除数据时钟偏斜的方法,包括:

35.从mipi d-phy物理层的串行链路的第一通道接收模拟的时钟信号,并经过处理后得到数字的初始时钟信号;

36.从mipi d-phy物理层的串行链路的多个第二通道分别接收模拟的数据信号,并基于所述初始时钟信号分别处理多个数据信号以输出多个数字的数据信号及其对应的字时钟信号;

37.从所述多个数字的数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差,其中,多个校正后的有效数据和所述第一字时钟信号将被提供给所述串行通信装置除mipi d-phy物理层之外的其他层,所述第一字时钟信号选自多个字时钟信号。

38.在一些实施例中,所述从所述多个数字的数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差包括:

39.将第一控制信号同步到所述第一字时钟信号的时钟域以输出第二控制信号,所述第一控制信号在所述初始时钟信号的时钟域产生;

40.对所述第二控制信号进行展宽,以得到第三控制信号;

41.接收所述多个数字的数据信号及其对应的字时钟信号,并基于所述第三控制信号对所述多个数字的数据信号的接收进行数据输入约束,并从所述多个数字的数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与所述第一字时钟信号的相位偏差。

42.在一些实施例中,所述接收所述多个数字的数据信号及其对应的字时钟信号,并基于所述第三控制信号对所述多个数字的数据信号的接收进行数据输入约束,并从所述多个数字的数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与所述第一字时钟信号的相位偏差包括:

43.先将所述多个数字的数据信号同步到各自对应的字时钟信号的时钟域,然后再同步到所述第一字时钟信号的时钟域;

44.通过所述第三控制信号提供的数据输入约束对多个同步后的数据信号分别进行采样以得到多个采样信号;

45.分别将连续两个时钟周期的采样信号进行拼接以得到多个拼接信号,从多个拼接信号分别确定各自的有效数据的起点,并据此校正每个有效数据与所述第一字时钟信号的相位偏差。

46.串行通信装置在非连续模式下,时钟通道和数据通道进行低功耗到高速模式的切换过程中,时钟信号会产生毛刺(glitch),如果多个独立数据通道对时钟信号中的毛刺识别不同则输出的数据信号和字时钟信号会存在偏斜(skew)。针对这一现象,本公开实施例提供的串行通信装置包括同步处理装置,用于去除多个不同数据通道中的数据时钟偏斜,经过处理,所有数据通道中的数据信号都对齐到一个特定时钟信号上,经过对齐后的数据信号将提供给mipi d-phy物理层之上的其他层进行处理。

附图说明

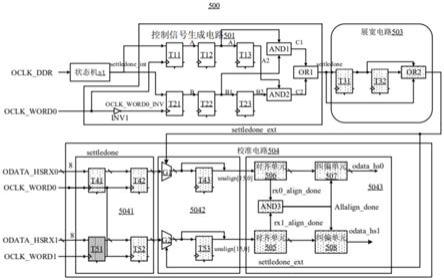

47.通过参照以下附图对本发明实施例的描述,本发明的上述以及其它目的、特征和优点将更为清楚,在附图中:

48.图1是串行通信装置100和200进行传输的示意图;

49.图2是可用于串行通信装置100和200的一个示例性的分层通信架构的结构图;

50.图3示出了一个典型的mipi d-phy物理层对一路数据信号和一路时钟信号进行处理的示意图;

51.图4示出了高速模式和低功耗模式切换的时序图;

52.图5示出本公开实施例提供的串行通信装置的同步处理装置的结构图;

53.图6示出了图5涉及的各个信号的信号时序图;

54.图7是示例性的存在数据时钟偏斜和不存在数据时钟偏斜的两组信号的时序对比图;

55.图8示出了本公开实施例提供的一种在串行通信装置中去除数据时钟偏斜的方法的流程图。

具体实施方式

56.以下基于实施例对本发明进行描述,但是本发明并不仅仅限于这些实施例。在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。为了避免混淆本发明的实质,公知的方法、过程、流程没有详细叙述。另外附图不一定是按比例绘制的。

57.附图中的流程图、框图图示了本发明实施例的系统、方法、装置的可能的体系框架、功能和操作,流程图和框图上的方框可以代表一个模块、程序段或仅仅是一段代码,所述模块、程序段和代码都是用来实现规定逻辑功能的可执行指令。也应当注意,所述实现规定逻辑功能的可执行指令可以重新组合,从而生成新的模块和程序段。因此附图的方框以及方框顺序只是用来更好的图示实施例的过程和步骤,而不应以此作为对发明本身的限制。

58.术语解释:

59.数据时钟偏斜(skew)是指数据信号和时钟信号以及各个数据信号之间的相位关系随着时序发生改变,例如,初始相位差为0,但是后续变为90或180度。这种改变造成的原因来自多种,例如时钟驱动器的多个输出之间的偏移,也包含了由于pcb走线误差造成的接收端和驱动端时钟信号之间的偏移。

60.抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者pll内部电路有关,布线对其没有影响。

61.图1是串行通信装置100和200进行传输的示意图。参考图1所示,串行通信装置100和串行通信装置200通过接口150和250进行串行化信号通信。接口150和250是能够传输电信号或光信号的物理接口,两者之间可通过物理信号线50耦接。串行通信装置100和200之间通过物理信号线发送和接收数据。在一些情况下,信号线50可以省略,串行通信装置100和200之间进行无线通信。接口150和250可以是mips接口或lvds接口。

62.图2是可用于串行通信装置100和200的一个示例性的分层通信架构的结构图。但应理解,串行通信装置100和200并不限定必须使用图上所示的分层通信架构,也可以采用诸如tcp/ip或osi等其他分层通信架构。

63.在图上,串行通信装置100包括层110至130,串行通信装置200包括层210至230,串行通信装置100和200通过物理层进行信息传输。串行通信装置100和200可作为信息接收端和/或发送端。当串行通信装置100作为信息发送端时,层130从各种应用程序接收要发送的数据,并将其传递给层120,层120对数据进行打包,通常会给数据增加包头和包尾,然后将打包数据传递给层110,层110将数字的打包数据转换为模拟的打包数据,并将模拟的打包数据转换成串行模拟信号发送给层210,此时串行通信装置200作为信息接收端,由层210接收串行模拟信号,将其转换为并行数字信号,然后传递给层220,由层220进行解析获得打包数据,然后传递给层230。反之亦然。

64.在图上,层110和210为物理层,层110和210之间传递串行模拟信号。层110和210既可以从上层接收并行的数字信号的打包数据,并将其转换为串行模拟信号传递给对方,也可以从对方接收串行模拟信号,将其转换为并行数字信号,并传递给上层。

65.层110和210可以采用各种协议,但在本公开中,主要讨论基于mipid-phy协议实现的物理层,因此可将层110和210称为mipi d-phy物理层。参考背景技术可知,mipi d-phy物理层最多可传输四路数据信号和一路时钟信号,mipi d-phy物理层对每一路数据信号和时钟信号进行处理。

66.图3示出了一个典型的mipi d-phy物理层对一路数据信号和一路时钟信号进行处理的示意图。参考图3所示,高速差分时钟信号dp_ck和dn_ck经过终端电阻r进行阻抗匹配,然后经过模拟信号接收电路32处理,放大后的模拟信号需要先经过模数转换电路33输出数字信号clkp和clkn,然后经过数控延时单元36对输出的数字信号clkp和clkn进行延时处理,给高速比较器37和串并转换电路39、串并转换电路40提供时钟信号。高速差分数据信号dp_dx和dn_dx经过终端电阻r进行阻抗匹配,然后经过模拟信号接收电路31处理,放大后的模拟信号需要先经过模数转换电路34输出数字信号,然后经过数控延时单元35延时处理,再进入高速比较器37。高速比较器37对输入的差分数据信号进行比较,输出数据信号再经过选择器38选择,选择器38的控制端接收选择控制信号sel_mipi_lvds,如果sel_mipi_lvds指示当前数据为mipi数据(对应于mipi接口),则时钟信号和数据信号经过串并转换电

路39输出数据信号hs_data和时钟信号hs_word_clk,如果sel_mipi_lvds指示当前数据为lvds数据(对应于lvds接口),则时钟信号和数据信号经过串并转换电路40输出数据信号lvds_data和时钟信号lvds_word_clk。此外,模数转换电路33输出的时钟信号还传递给分频器41,以分频得到时钟信号clk_ddr。

67.由于mipi是差分信号,即一条信号传输通道由两条信号线组成,因此通过高低电平的组合,这两条信号线应该有4种状态,但高速模式下的信号摆幅很小(仅为200mv),因此为了确保传输稳定,高速时信号状态只有两种,即互为高低压交错的两种状态(即hs-0和hs-1),低功耗模式则有四种状态(即lp0-00、lp01、lp10和lp11),因此状态则共有如下表所示的六种状态。其中,通道中的正信号线在下表中用dp-line标识,负信号线用dn-line表征。

68.表格1状态表

[0069][0070]

其中,hs low表示高速模式下的低电平,hs high表示高速模式下的高电平,lp low表示低功耗模式下的低电平,ls high表示高速模式下的高电平。

[0071]

接下来结合表格1和图4所示的高速模式和低功耗模式切换的时序图说明发送端和接收端的时钟传输通道(clock lane)切换的步骤。

[0072]

首先发送端和接收端的时钟传输通道从高速模式进入低功耗模式的步骤如下。

[0073]

首先是发送端从高速模式进入低功耗模式的步骤如下。

[0074]

1)时钟传输通道处于交错高速信号hs-0和hs-1的状态;

[0075]

2)数据传输通道先于时钟传输通道进入低功耗模式,以及最后一个数据传输通道也进入低功耗状态了;

[0076]

3)时钟传输通道依然保持高速时钟状态一段时间,时间长度为t

clk_post

,并最后以hs-0状态结束;

[0077]

4)保持hs-0状态t

clk_trail

时间;

[0078]

5)驱动高速发送电路(hs-tx)停止工作,并使能发送端的低功耗发送电路(lp-tx),并使lp-11状态保持t

hs_exit

时长,至此发送端即进入了lp模式。

[0079]

然后是接收端从高速模式进入低功耗模式的步骤如下。

[0080]

(一)、在发送端执行步骤1期间,接收端的时钟传输通道处于交错高速信号hs-0和hs-1的状态;

[0081]

(二)、在发送端执行步骤2)和3)期间,接收端的时钟传输通道保持不变;

[0082]

(三)、在发送端执行步骤4)期间,接收端的检测模块在时间t

clk_miss

时段检测到时钟信号,在发现切换时,使接收端的接收电路停止工作并等候lp-11状态;

[0083]

(四)、接收端的检测模块在从dp-line和dn-line检测到lp-11时,进入lp-11状态。

[0084]

第二,发送端和接收端的时钟传输通道从低功耗模式进入高速模式的步骤如下。

[0085]

首先是发送端从低功耗模式进入高速模式的步骤如下。

[0086]

1.发送端停止驱动状态lp-11;

[0087]

2.发送端驱动lp-01状态,并维持t

lpx

时长;

[0088]

3.发送端驱动lp-00状态,并维持t

clk_prep

时长;

[0089]

4.发送端驱动hs-0状态,并维持t

clk_zero

时长,并在这段时间内完成低功耗接收电路(lprx)到高速接收电路(hsrx)的切换。

[0090]

5.在任一条数据传输通道启动前,保持高速时钟状态t

clk_prep

时长。之后,数据传输通道经过t

lpx

,t

data_prep

,t

data_zero

之后也开始传输数据信号。

[0091]

然后是接收端从低功耗模式进入高速模式的步骤如下。

[0092]

一、在发送端执行步骤1时,接收端的检测模块接收并检测到接收到的时钟信号为lp-11;

[0093]

二、在发送端执行步骤2时,接收端的检测模块接收并检测到接收到的时钟信号为lp-11变为lp01;

[0094]

三、在发送端执行步骤3时,接收端的检测模块接收并检测到接收到的时钟信号为lp-01变为lp00,则在时长t

clk_term_en

内使能线路终端(line termination)。

[0095]

四、在发送端执行步骤4时,接收端的检测模块使能高速接收电路并等候t

clk_settle

时长,然后开始接收高速信号;

[0096]

五、在发送端执行步骤5,接收高速时钟信号。

[0097]

参考图4所示,从图4可以看出低功耗模式切换高速模式(发送端从低功耗模式进入高速模式的步骤4)的过程中,在t

clk_zero

过程中因为模拟电路内部尚未稳定,所以会产生毛刺(glitch),参考图3所示,包含毛刺的时钟信号会被接收端的模拟信号接收电路32接收到,如果在后续处理时,时钟信号中的毛刺被多条数据传输通道识别得不一样,则经过串并转换后的多个数字时钟会产生相位偏差,从而导致与多个数字时钟对应的数据信号之间存在偏差。

[0098]

为了解决上述问题,本公开实施例提供一种串行通信装置,该装置的mipi d-phy物理层对图3输出的数据和时钟信号进行偏斜校正后,再传递给如图2中的上层120或220,为了达到这一目的,在串行通信装置中增加了一个同步处理装置,其结构图如图5所示。同步处理装置500包括控制信号生成电路501和校准单元504。作为更优选的实施例,同步处理装置500还可包括设置在控制信号生成电路501和校准单元504之间的展宽电路503。

[0099]

根据mipi d-phy协议可知,在模拟电路从低功耗模式切换到高速模式之后,需要等模拟电路切换稳定后再将有效数据输入到数字部分。因此状态机(state machine)st在时钟传输通道中的模拟电路从低功耗模式切换高速模式并等时钟稳定一段时间后,拉高控制信号settledone_int,该信号用于控制同步处理装置中的多个数据信号的接收同步。

[0100]

图6示出了图5涉及的各个信号的信号时序图。由于信号settledone_int是状态机

在oclk_ddr时钟域产生,但最终是在oclk_word0时钟域下判决有效数据是否输入,所以需要将该信号同步到oclk_word0时钟域(即使settledone_int与oclk_word0边沿对齐)。时钟信号oclk_word0是四个数据通道中的第一数据通道在高速模式下经由串并转换电路输出的字时钟信号,例如可以为图3中的hs_word_clk。可以将四个数据通道中最快进入高速模式的数据通道作为第一数据通道。

[0101]

控制信号生成电路501接收时钟信号oclk_word0和settledone_int,用于将settledone_int同步到oclk_word0的时钟域并输出settledone信号。

[0102]

在一些实施例中,控制信号生成电路501包括:反相器、第一采样电路、第二采样电路和逻辑运算单元。反相器用于将oclk_word0反相,以得到oclk_word0_inv;第一采样电路,包括串联的d触发器t11至t13,用于基于oclk_word0对控制信号settledone_int进行采样,并输出采样信号a1和a2;第二采样电路,包括串联的d触发器t21至t23,用于基于oclk_word0_inv对控制信号settledone_int进行采样,并输出采样信号b1和b2;逻辑运算单元,用于将采样信号a1、a2、b1和b2进行逻辑运算,以得到控制信号settledone。

[0103]

作为更具体的实施例,如图5所示,控制信号生成电路501包括反相器inv、串联的d触发器t11至t13、串联的d触发器t21至t23、与门and1和and2以及或门or1。如图5所示,反相器inv1将oclk_word0反相得到oclk_word0_inv。d触发器t11的clk端接收时钟信号oclk_word0,d端接收数据settledone_int,q端输出数据信号a。d触发器t12的clk端接收时钟信号oclk_word0_inv,d端接收数据a,q端输出数据信号a1。d触发器t13的clk端接收时钟信号oclk_word0_inv,d端接收数据a1,q端输出数据信号a2。

[0104]

d触发器t21的clk端接收时钟信号oclk_word0_inv,d端接收数据settledone_int,q端输出数据信号b。d触发器t22的clk端接收时钟信号oclk_word0,d端接收数据b,q端输出数据信号b1。d触发器t23的clk端接收时钟信号oclk_word0,d端接收数据b1,q端输出数据信号b2。

[0105]

与门and1接收信号a1和b1,并输出信号c1。与门and2接收信号a2和b2,并输出信号c2。或门or1接收信号c1和c2并输出信号settledone。

[0106]

在本实施例中,由于为了防止信号时序出错,控制信号生成电路501进行两级同步,并在每一级中采用d触发器基于时钟信号oclk_word0以及该时钟信号的反相信号oclk_word0_inv对控制信号进行边沿采样(相当于进行上边沿和下边沿采样),然后通过与门和或门输出同步后的信号。通过两级双边沿采样,目的是以最短的时间将输出信号settledone同步到时钟域oclk_word0。

[0107]

经过同步后的settledone信号输入到展宽电路503进行展宽操作,目的是防止一帧有效数据的结尾因为settledone信号的提前拉低而丢失。展宽电路503将输入的settledone的有效时间进行延长后输出信号settledone_ext。

[0108]

在一些实施例中,如图5所示,展宽电路503包括d触发器t31和t32以及或门or2。d触发器t31的clk端接收时钟信号oclk_word0,d端接收数据settledone。d触发器t32的clk端接收时钟信号oclk_word0,d端接收触发器t31输出的数据信号。或门or2接收t31和t32输出的数据信号进行或运算。从图6可以看出,settledone_ext相对于settledone,其高电平保持时间得到了延长。

[0109]

校准单元504用于将各个数据传输通道的多个数据信号同步到同一个时钟域,然

后对各个数据信号进行对齐和校准。在图上示例性示出了对数据信号odata_hsrx0和odata_hsrx1的校准过程,但应理解,其余数据信号也大致相同。这里odata_hsrx0和oclk_word0是数据通道lane0在高速模式下经由串并转换电路输出的数据信号和字时钟信号,odata_hsrx1和oclk_word1是数据通道lane1在高速模式下经由串并转换电路输出的数据信号和字时钟信号。

[0110]

在一些实施例中,校准单元504包括时钟域同步单元5041、时序控制单元5042和偏差校正单元5043。时钟域同步单元5041用于先将多个数据信号同步到各自对应的字时钟信号的时钟域,然后再同步到oclk_word0的时钟域。时序控制单元5042用于通过settledone_ext提供的数据输入约束对多个同步后的数据信号分别进行采样以得到多个采样信号。偏差校正单元5043用于分别将连续两个时钟周期的采样信号进行拼接以得到多个拼接信号,从多个拼接信号分别确定各自的有效数据的起点,并据此校正每个有效数据与oclk_word0的相位偏差。

[0111]

作为更具体的实施例,如图上所示,d触发器t41的clk端接收时钟信号oclk_word0,d端接收数据信号odata_hsrx0。d触发器t42的clk端接收时钟信号oclk_word0,d端接收d触发器t41输出的数据信号。门控单元g1的控制端接收settledone_ext,输入端接收d触发器t42的输出数据,输出端与d触发器t43的d端耦接。d触发器t43的clk端接收oclk_word0,输出端与对齐单元506耦接。对齐单元506将获取到的连续的8比特的有效数据拼接为16比特,通过移位操作对齐到有效数据的起点(例如为0001_1101,有效数据的起点),然后纠偏单元507基于对齐后的有效数据对时钟信号oclk_word0去除数据中的偏斜。

[0112]

如图上所示,触发器t51的clk端接收时钟信号oclk_word1,d端接收数据信号odata_hsrx1。d触发器t52的clk端接收时钟信号oclk_word0,d端接收从d触发器t52输出的数据信号。门控单元g2用于根据settledone_ext控制数据传输,其控制端接收settledone_ext,输入端接收d触发器t52的输出数据,输出端与d触发器t53的d端耦接。d触发器t53的clk端接收oclk_word0,输出端与对齐单元505耦接。对齐单元505获取两个连续的有效数据拼接为16比特,通过移位操作对齐到有效数据的起点,然后纠偏单元507基于时钟信号oclk_word0纠正所述对齐后的有效数据时钟信号的相位偏移。

[0113]

为了使odata_hsrx0和odata_hsrx1的对齐后的有效数据同步到同一个时钟域(即由oclk_word0确定的时钟域),对齐单元506和505分别在各自完成对齐操作后,输出指示rx0_align_done和rx1_align_done给与门and3,and3进行与操作,输出指示allalign_done,表示两个数据通道的对齐操作已经完成。纠偏单元507和纠偏单元508根据指示allalign_done输出对齐后的有效数据odata_hs0和odata_hs1。odata_hs0和odata_hs1为在同一时钟域下(即由oclk_word0确定的时钟域)的数据,可将数据和时钟信号一并提供给上层。

[0114]

应该理解,g1和g2采用前面经过处理后的settledone_ext信号作为使能开关信号,以确保此时模拟电路已经由低速模式切换到高速模式,并且可以同时接收对应数据通道的数据信号。

[0115]

为了更好地说明图5的电路设计理念,图7是示例性的存在数据时钟偏斜和不存在数据时钟偏斜的两组信号的时序对比图。

[0116]

参考图7所示,首先,从oclk_word1同步到oclk_word0时钟域下,经过对glitch导

致的word_clk相位偏差分析,发现其周期性,下面对同步过程详细分析。

[0117]

下面以lane1为例,其它情况类似:假设图中lane0是没有毛刺的输出的正常的oclk_word0以及对应的数据,lane1是识别到一个毛刺的输出的oclk_word1以及对应的数据,可以看出两个时钟相位偏差90。odata_hsrx1是对应oclk_word1下降沿输出的数据,首先同步到本身对应的字时钟的上升沿,同步后的结果为图中阴影部分odata_hsrx_sync。最后再用oclk_word0上升沿采样每条lane上经过同步后的数据odata_hsrx_sync,采样结果为odata_hsrxx_samp。经过上面的分析可以发现,由毛刺带来的时钟和数据偏差据有周期性,即:一个毛刺产生90度相位偏差,两个毛刺产生180度相位偏差,三个毛刺产生270度相位偏差,四个毛刺不会导致相位偏差。

[0118]

基于上述电路处理过程,不需要异步fifo进行跨时钟域处理,通过数据输入约束就可以将多个数据通道的数据时钟偏斜校正。这样做的优势在于可以节省电路面积;防止数据不连续并能够减少同步过程的延迟。

[0119]

图8示出了本公开实施例提供的一种在串行通信装置中去除数据时钟偏斜的方法的流程图。如图8所示,包括步骤s01至s03。

[0120]

在步骤s01中,从mipi d-phy物理层的串行链路的第一通道接收模拟的时钟信号,并经过处理后得到数字的初始时钟信号。

[0121]

在步骤s02中,从mipi d-phy物理层的串行链路的多个第二通道分别接收模拟的数据信号,从时钟接收装置获取初始时钟信号,分别处理多个数据信号以输出多个数字的数据信号及其对应的字时钟信号。

[0122]

在步骤s03中,从接收到的多个数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差。

[0123]

在一些实施例中,步骤s03包括以下子步骤:

[0124]

步骤s0031:将第一控制信号同步到第一字时钟信号的时钟域以输出第二控制信号,其中,第一控制信号在时钟信号的时钟域产生;

[0125]

步骤s0032:对第二控制信号进行展宽,以得到第三控制信号;

[0126]

步骤s0033:从多个数据接收装置接收多个数据信号及其对应的字时钟信号,并基于第三控制信号对多个数据接收装置的数据接收进行数据输入约束,并从接收到的多个数据信号中分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差。

[0127]

其中步骤s0033的具体操作可包括:先将从多个数据接收装置接收到的多个数据信号同步到各自对应的字时钟信号的时钟域,然后再同步到第一字时钟信号的时钟域;基于第三控制信号提供的数据输入约束对多个同步后的数据信号分别进行采样以得到多个采样信号;分别将连续两个时钟周期的采样信号进行拼接以得到多个拼接信号,从多个拼接信号分别确定各自的有效数据的起点,并据此校正每个有效数据与第一字时钟信号的相位偏差。

[0128]

该方法和上述装置对应,用于在串行通信装置中去除多个不同数据通道中的数据时钟偏斜,经过处理步骤,所有数据通道中的数据信号都对齐到一个特定时钟信号上,经过对齐后的数据信号将提供给mipid-phy物理层之上的其他层进行处理。

[0129]

本实施方式涉及包含以上记载的电路装置的电子设备。另外,本实施方式涉及包

含以上记载的电路装置的移动体。另外,虽然如上述那样对本实施方式进行了详细说明,但本领域技术人员可以容易地理解,在实质上不脱离本公开的新事项和效果的情况下,可以进行多种变形。因此,所有这样的变形例都包含在本公开的范围内。例如,在说明书或者附图中,至少一次与更加广义或者同义的不同用语一同记载的用语在说明书或者附图的任意部位都可以置换为该不同用语。另外,本实施方式及变形例的全部组合也包含在本公开的范围内。另外,电路装置、电子设备、移动体的结构或动作等也不限于本实施方式中说明的内容,可实施各种变形。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1