用于确定存储器单元的预期数据使用期限的设备及方法与流程

用于确定存储器单元的预期数据使用期限的设备及方法

[0001]

相关申请案

[0002]

本专利申请案涉及共同转让的与本专利申请案同日申请的名称为“用于确定存储器单元的预期数据使用期限的设备及方法(apparatus and methods for determining an expected data age of memory cells)”的第16/161,256号美国专利申请案。

技术领域

[0003]

本发明大体上涉及存储器,且特定来说,在一或多个实施例中,本发明涉及用于确定存储器单元的预期数据使用期限的设备及方法,其可用于确定所述存储器单元的数据状态。

背景技术:

[0004]

存储器(例如存储器装置)通常提供为计算机或其它电子装置中的内部半导体集成电路装置。存在许多不同类型的存储器,其包含随机存取存储器(ram)、只读存储器(rom)、动态随机存取存储器(dram)、同步动态随机存取存储器(sdram)及快闪存储器。

[0005]

快闪存储器已发展为用于各种电子应用的非易失性存储器的普遍来源。快闪存储器通常使用允许高存储器密度、高可靠性及低功耗的单晶体管存储器单元。通过电荷存储结构(例如浮动栅极或电荷陷阱)的编程(其通常称为写入)或其它物理现象(例如相变或偏振)的存储器单元的阈值电压(vt)变化确定每一存储器单元的数据状态(例如数据值)。快闪存储器及其它非易失性存储器的常见用途包含个人计算机、个人数字助理(pda)、数码相机、数字媒体播放器、数字记录器、游戏、电器、车辆、无线装置、移动电话及可装卸存储器模块,且非易失性存储器的用途在继续扩展。

[0006]

nand快闪存储器是快闪存储器装置的常见类型,其因布置基本存储器单元配置的逻辑形式而如此命名。通常,nand快闪存储器的存储器单元阵列经布置使得阵列的行的每一存储器单元的控制栅极连接在一起以形成例如字线的存取线。阵列的列包含一起串联连接于一对选择门(例如源极选择晶体管与漏极选择晶体管)之间的存储器单元串(通常称作nand串)。每一源极选择晶体管可连接到源极,而每一漏极选择晶体管可连接到例如列位线的数据线。在一串存储器单元与源极之间及/或存储器单元串与数据线之间使用多于一个选择门的变型是众所周知的。

[0007]

在编程存储器时,存储器单元通常可编程为所谓的单电平单元(slc)。slc可使用单存储器单元来表示数据的1个数字(例如1个位)。例如,在slc中,2.5v或更高的vt可指示经编程存储器单元(例如表示逻辑0),而-0.5v或更低的vt可指示经擦除存储器单元(例如表示逻辑1)。此存储器可通过包含多电平单元(mlc)、三电平单元(tlc)、四电平单元(qlc)等等或其组合来实现较高存储容量电平,其中存储器单元具有使更多数据数字能够存储于每一存储器单元中的多个电平。例如,mlc可经配置以每存储器单元存储由4个vt范围表示的2个数据数字,tlc可经配置以每存储器单元存储由8个vt范围表示的3个数据数字,qlc可经配置以每存储器单元存储由16个vt范围表示的4个数据数字,等等。

[0008]

感测(例如读取或验证)存储器单元的数据状态通常涉及检测存储器单元是否响应于施加到其控制栅极的特定电压而激活,例如通过检测连接到存储器单元的数据线是否经历由流动通过存储器单元的电流引起的电压电平改变。依靠存储电荷电平来界定不同vt范围的存储器通常经受随时间电荷损失以导致vt范围的移位及扩展。此可导致受感测存储器单元的数据状态的不准确确定(归因于其vt随时间的改变)。

附图说明

[0009]

图1是根据实施例的与作为电子系统的部分的处理器通信的存储器的简化框图。

[0010]

图2a到2c是可用于参考图1所描述的类型的存储器中的存储器单元阵列的部分的示意图。

[0011]

图3是多个存储器单元的阈值电压分布的概念图。

[0012]

图4a到4b是根据实施例的多个存储器单元的阈值电压分布的概念图。

[0013]

图5是展示根据实施例的存储器单元群组的数据使用期限与响应于特定读取电压而激活的存储器单元数目之间的假想假定关系的曲线图。

[0014]

图6是描绘用于与各种实施例一起使用的数据线到感测装置及页缓冲器的连接的框示意图。

[0015]

图7描绘用于与实施例一起使用的操作存储器的方法的时序图。

[0016]

图8描绘根据实施例的操作存储器的方法的时序图。

[0017]

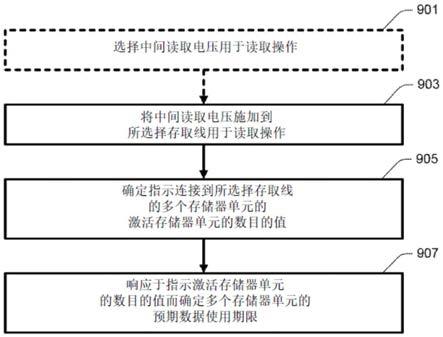

图9是根据实施例的操作存储器的方法的流程图。

[0018]

图10是根据另一实施例的操作存储器的方法的流程图。

[0019]

图11是根据另一实施例的操作存储器的方法的流程图。

具体实施方式

[0020]

在以下详细描述中,参考构成本发明的一部分的附图,且附图中通过说明来展示特定实施例。在图式中,相同元件符号描述所有若干视图中的基本上类似组件。可利用其它实施例,且可在不背离本发明的范围的情况下作出结构、逻辑及电改变。因此,以下详细描述不应被视为意在限制。

[0021]

本文中所使用的术语“半导体”可指代(例如)材料层、晶片或衬底,且包含任何基底半导体结构。“半导体”应被理解为包含蓝宝石上硅(sos)技术、绝缘体上硅(soi)技术、薄膜晶体管(tft)技术、掺杂及未掺杂半导体、由基底半导体结构支撑的硅的外延层及所属领域的技术人员众所周知的其它半导体结构。此外,当以下描述中参考半导体时,可利用先前过程步骤来形成基底半导体结构中的区域/结,且术语“半导体”可包含含有此类区域/结的下伏层。除非从上下文另外明白,否则本文中所使用的术语“导电(conductive)”及其各种相关形式(例如传导(conduct)、导电地(conductively)、传导(conduction)、导电性(conductivity)等等)指代导电(electrically conductive)。类似地,除非从上下文另外明白,否则本文中所使用的术语“连接(connecting)”及其各种相关形式(例如连接(connect)、经连接(connected)、连接(connection)等等)指代电连接(electrically connecting)。

[0022]

图1是根据实施例的与第二设备通信的第一设备(呈存储器(例如存储器装置)100

的形式)的简化框图,第二设备呈作为第三设备(呈电子系统的形式)的部分的处理器130的形式。电子系统的一些实例包含个人计算机、个人数字助理(pda)、数码相机、数字媒体播放器、数字记录器、游戏、电器、车辆、无线装置、移动电话及其类似者。处理器130(例如存储器装置100外的控制器)可为存储器控制器或其它外部主机装置。

[0023]

存储器装置100包含逻辑布置成行及列的存储器单元阵列104。逻辑行的存储器单元通常连接到相同存取线(通常称为字线),而逻辑列的存储器单元通常选择性连接到相同数据线(通常称为位线)。单个存取线可与存储器单元的多于一个逻辑行相关联,且单个数据线可与多于一个逻辑列相关联。存储器单元阵列104的至少一部分的存储器单元(图1中未展示)能够编程为至少两个目标数据状态中的一者。

[0024]

提供行解码电路108及列解码电路110来解码地址信号。接收及解码地址信号以存取存储器单元阵列104。存储器装置100还包含用于管理命令、地址及数据输入到存储器装置100及从存储器装置100输出数据及状态信息的输入/输出(i/o)控制电路112。地址寄存器114与i/o控制电路112及行解码电路108及列解码电路110通信以在解码之前锁存地址信号。命令寄存器124与i/o控制电路112及控制逻辑116通信以锁存传入命令。微调寄存器128可与控制逻辑116通信。微调寄存器128可表示易失性存储器、锁存器或其它易失性或非易失性存储位置。针对一些实施例,微调寄存器128可表示存储器单元阵列104的一部分。根据实施例,微调寄存器128可存储与确定存储器单元的预期数据使用期限及/或确定读取电压相关的信息。根据实施例,控制逻辑116可经配置以执行操作存储器的方法。

[0025]

控制器(例如存储器装置100内的控制逻辑116)响应于命令而控制存储器单元阵列104的存取且产生用于外部处理器130的状态信息,即,控制逻辑116经配置以对存储器单元阵列104执行存取操作(例如读取操作、编程操作及/或擦除操作)。控制逻辑116与行解码电路108及列解码电路110通信以响应于地址而控制行解码电路108及列解码电路110。

[0026]

控制逻辑116还与高速缓存寄存器118通信。高速缓存寄存器118根据控制逻辑116的指导来锁存传入或传出数据以在存储器单元阵列104分别忙于写入或读取其它数据时暂时存储数据。在编程操作(例如写入操作)期间,数据可从高速缓存寄存器118传到数据寄存器120以传送到存储器单元阵列104;接着,新数据可从i/o控制电路112锁存于高速缓存寄存器118中。在读取操作期间,数据可从高速缓存寄存器118传到i/o控制电路112以输出到外部处理器130;接着,新数据可从数据寄存器120传到高速缓存寄存器118。高速缓存寄存器118及/或数据寄存器120可形成存储器装置100的页缓冲器(例如可形成存储器装置100的页缓冲器的一部分)。页缓冲器可进一步包含感测装置(图1中未展示)以感测存储器单元阵列104的存储器单元的数据状态,例如通过感测连接到所述存储器单元的数据线的状态。状态寄存器122可与i/o控制电路112及控制逻辑116通信以锁存用于输出到处理器130的状态信息。

[0027]

存储器装置100在控制逻辑116处经由控制链路132从处理器130接收控制信号。控制信号可包含芯片启用ce#、命令锁存启用cle、地址锁存启用ale、写入启用we#、读取启用re#及写入保护wp#。可经由控制链路132来进一步接收额外或替代控制信号(图中未展示),这取决于存储器装置100的性质。存储器装置100可从处理器130经由多路复用输入/输出(i/o)总线134接收命令信号(其表示命令)、地址信号(其表示地址)及数据信号(其表示数据)及经由i/o总线134来输出数据到处理器130。

[0028]

例如,命令可在i/o控制电路112处经由i/o总线134的输入/输出(i/o)引脚[7:0]来接收且接着可写入到命令寄存器124中。地址可在i/o控制电路112处经由i/o总线134的输入/输出(i/o)引脚[7:0]来接收且接着写入到地址寄存器114中。数据可在i/o控制电路112处经由用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]来接收且接着可写入到高速缓存寄存器118中。随后,可将数据写入到数据寄存器120中以编程存储器单元阵列104。针对另一实施例,可省略高速缓存寄存器118,且可将数据直接写入到数据寄存器120中。还可经由用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]来输出数据。

[0029]

所属领域的技术人员应了解,可提供额外电路及信号且已简化图1的存储器装置100。应认识到,参考图1所描述的各种块组件的功能可未必分到集成电路装置的不同组件或组成部分。例如,集成电路装置的单个组件或组成部分可经调适以执行图1的多于一个块组件的功能。替代地,集成电路装置的一或多个组件或组成部分可经组合以执行图1的单个块组件的功能。

[0030]

另外,尽管根据用于接收及输出各种信号的普遍惯例来描述特定i/o引脚,但应注意,可在各种实施例中使用i/o引脚(或其它i/o节点结构)的其它组合或数目。

[0031]

图2a是可用于参考图1所描述的类型的存储器(例如作为存储器单元阵列104的一部分)中的存储器单元阵列200a(例如nand存储器阵列)的一部分的示意图。存储器阵列200a包含例如字线202

0

到202

n

的存取线及例如位线204

0

到204

m

的数据线。字线202可以多对一关系连接到全局存取线(例如全局字线)(图2a中未展示)。针对一些实施例,存储器阵列200a可形成于半导体上,所述半导体可(例如)经导电掺杂以具有导电类型,例如具有(例如)p型导电性以形成p阱或具有(例如)n型导电性以形成n阱。

[0032]

存储器阵列200a可布置成行(各自对应于字线202)及列(各自对应于位线204)。每一列可包含一串串联连接的存储器单元(例如非易失性存储器单元),例如nand串206

0

到206

m

中的一者。每一nand串206可连接到(例如选择性连接)到共同源极(src)216且可包含存储器单元208

0

到208

n

。存储器单元208可表示用于存储数据的非易失性存储器单元。每一nand串206的存储器单元208可串联连接于选择门210(例如场效应晶体管)(例如选择门210

0

到210

m

(例如,其可为源极选择晶体管,通常称为选择门源极))与选择门212(例如场效应晶体管)(例如选择门212

0

到212

m

(例如,其可为漏极选择晶体管,通常称为选择门漏极))之间。选择门210

0

到210

m

可共同连接到选择线214(例如源极选择线(sgs)),且选择门212

0

到212

m

可共同连接到选择线215(例如漏极选择线(sgd))。尽管描绘为传统场效应晶体管,但选择门210及212可利用类似于存储器单元208的结构(例如与所述结构相同)。选择门210及212可表示串联连接的多个选择门,其中每一串联选择门经配置以接收相同或独立控制信号。

[0033]

每一选择门210的源极可连接到共同源极216。每一选择门210的漏极可连接到对应nand串206的存储器单元208

0

。例如,选择门210的漏极可连接到对应nand串206

0

的存储器单元208

0

。因此,每一选择门210可经配置以将对应nand串206选择性连接到共同源极216。每一选择门210的控制栅极可连接到选择线214。

[0034]

每一选择门212的漏极可连接到对应nand串206的位线204。例如,选择门212

0

的漏极可连接到对应nand串206

0

的位线204

0

。每一选择门212的源极可连接到对应nand串206的

存储器单元208

n

。例如,选择门212

0

的源极可连接到对应nand串206

0

的存储器单元208

n

。因此,每一选择门212可经配置以将对应nand串206选择性连接到对应位线204。每一选择门212的控制栅极可连接到选择线215。

[0035]

图2a中的存储器阵列可为准二维存储器阵列且可具有大体上平面结构,例如其中共同源极216、nand串206及位线204沿基本上平行面延伸。替代地,图2a中的存储器阵列可为三维存储器阵列,例如其中nand串206可基本上垂直于含有共同源极216的平面及含有位线204的平面(其可基本上平行于含有共同源极216的平面)延伸。

[0036]

存储器单元208的典型构造包含可确定存储器单元的数据状态(例如通过阈值电压的改变)的数据存储结构234(例如浮动栅极、电荷陷阱或经配置以存储电荷的其它结构)及控制栅极236,如图2a中所展示。数据存储结构234可包含导电及电介质两种结构,而控制栅极236一般由一或多种导电材料形成。在一些情况中,存储器单元208可进一步具有所界定源极/漏极(例如源极)230及所界定源极/漏极(例如漏极)232。存储器单元208使其控制栅极236连接到(且在一些情况中形成)字线202。

[0037]

一列存储器单元208可为选择性连接到给定位线204的nand串206或多个nand串206。一行存储器单元208可为共同连接到给定字线202的存储器单元208。一行存储器单元208可(但未必)包含共同连接到给定字线202的所有存储器单元208。存储器单元行208通常可分成存储器单元208的一或多个物理页群组,且存储器单元208的物理页通常包含共同连接到给定字线202的每隔一个存储器单元208。例如,共同连接到字线202

n

且选择性连接到偶数位线204(例如位线204

0

、204

2

、204

4

等等)的存储器单元208可为存储器单元208的物理页(例如偶数存储器单元),而共同连接到字线202

n

且选择性连接到奇数位线204(例如位线204

1

、204

3

、204

5

等等)的存储器单元208可为存储器单元208的另一物理页(例如奇数存储器单元)。尽管图2a中未明确描绘位线204

3

到204

5

,但应从图明白,存储器单元阵列200a的位线204可从位线204

0

连续编号到位线204

m

。共同连接到给定字线202的存储器单元208的其它群组还可界定存储器单元208的物理页。针对特定存储器装置,共同连接到给定字线的所有存储器单元可被视为存储器单元的物理页。在单读取操作期间读取或在单个编程操作期间编程的存储器单元的物理页的部分(在一些实施例中,其可仍为整行)(例如存储器单元的上页或下页)可被视为存储器单元的逻辑页。存储器单元块可包含经配置以一起被擦除的存储器单元,例如连接到字线202

0

到202

n

的所有存储器单元(例如共享共同字线202的所有nand串206)。除非明确区分,否则本文中所参考的页存储器单元指代存储器单元的逻辑页的存储器单元。

[0038]

尽管结合nand快闪存储器来讨论图2a的实例,但本文中所描述的实施例及概念不受限于特定阵列架构或结构,而是可包含其它结构(例如sonos或经配置以存储电荷的其它数据存储结构)及其它架构(例如and阵列、nor阵列等等)。

[0039]

图2b是可用于参考图1所描述的类型的存储器(例如作为存储器单元阵列104的一部分)中的存储器单元阵列200b的一部分的另一示意图。图2b中的相同元件符号对应于相对于图2a所提供的描述。图2b提供三维nand存储器阵列结构的实例的额外细节。三维nand存储器阵列200b可并入可包含半导体柱的垂直结构,其中柱的一部分可充当nand串206的存储器单元的沟道区域。nand串206可各自通过选择晶体管212(例如,其可为漏极选择晶体管,通常称为选择门漏极)来选择性连接到位线204

0

到204

m

,且通过选择晶体管210(例如,其

可为源极选择晶体管,通常称为选择门源极)来连接到共同源极216。多个nand串206可选择性连接到相同位线204。nand串206的子集可通过加偏压于选择线215

0

到215

k

来连接到其相应位线204以选择性激活各自介于nand串206与位线204之间的特定选择晶体管212。可通过加偏压于选择线214来激活选择晶体管210。每一字线202可连接到存储器阵列200b的多行存储器单元。通过特定字线202来彼此共同连接的存储器单元行可统称层面。

[0040]

图2c是可用于参考图1所描述的类型的存储器(例如作为存储器单元阵列104的一部分)中的存储器单元阵列200c的一部分的另一示意图。图2c中的相同元件符号对应于相对于图2a所提供的描述。存储器单元阵列200c可包含串联连接的存储器单元串(例如nand串)206、存取(例如字)线202、数据(例如位)线204、选择线214(例如源极选择线)、选择线215(例如漏极选择线)及源极216,如图2a中所描绘。例如,存储器单元阵列200a的一部分可为存储器单元阵列200c的一部分。图2c描绘将nand串206群组为存储器单元块250。存储器单元块250可为可在单个擦除操作中一起被擦除的存储器单元208的群组,有时称为擦除块。每一存储器单元块250可表示共同与单个选择线215(例如选择线215

0

)相关联的nand串206。存储器单元块250

0

的源极216可为相同于存储器单元块250

l

的源极216的源极。例如,每一存储器单元块250

0

到250

l

可共同选择性连接到源极216。存储器单元块250的存取线202及选择线214及215可不直接连接到存储器单元块250

0

到250

l

的任何其它存储器单元块的相应存取线202及选择线214及215。

[0041]

数据线204

0

到204

m

可连接(例如选择性连接)到缓冲器部分240,缓冲器部分240可为存储器的页缓冲器的一部分。缓冲器部分240可对应于存储器平面(例如存储器单元块250

0

到250

l

的组)。缓冲器部分240可包含用于感测相应数据线204上所指示的数据值的感测装置(图中未展示)及用于存储从其对应存储器平面感测的数据值的对应寄存器(图中未展示)。

[0042]

图3是多个存储器单元的阈值电压范围的概念图。图3说明16电平存储器单元(通常称为qlc存储器单元)的群体的阈值电压范围及其分布的实例。例如,此存储器单元可编程到落于16个不同阈值电压范围330

0

到330

15

中的一者内的阈值电压(vt),所述阈值电压范围各自用于表示对应于4个位的位模式的数据状态。阈值电压范围330

0

通常具有大于剩余阈值电压范围330

1

到330

15

的宽度,因为存储器单元一般全部处于对应于阈值电压范围330

0

的数据状态中,接着,所述存储器单元的子集随后经编程以具有阈值电压范围330

1

到330

15

中的一者内的阈值电压。因为编程操作一般比擦除操作更逐渐受控,所以这些阈值电压范围330

1

到330

15

可倾向于具有更紧密分布。

[0043]

阈值电压范围330

0

、330

1

、330

2

、330

3

、330

4

、330

5

、330

6

、330

7

、330

8

、330

9

、330

10

、330

11

、330

12

、330

13

、330

14

及330

15

可各自表示相应数据状态,例如分别为l0、l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l13、l14及l15。作为一个实例,如果存储器单元的阈值电压是在16个阈值电压范围中的第一者330

0

内,那么此情况中的存储器单元可存储具有逻辑“1111”的数据值的数据状态l0且通常称为存储器单元的擦除状态。如果阈值电压是在16个阈值电压范围中的第二者330

1

内,那么此情况中的存储器单元可存储具有逻辑“0111”的数据值的数据状态l1。如果阈值电压是在16个阈值电压范围中的第三者330

2

内,那么此情况中的存储器单元可存储具有逻辑“0011”的数据值的数据状态l2,等等。表1提供数据状态与其对应逻辑数据值之间的可能对应性。数据状态与逻辑值的其它指派是众所周知的。如本文中所使

用,保持最低数据状态(例如擦除状态或l0数据状态)的存储器单元将被视为编程到最低数据状态。表1的信息可含于(例如)微调寄存器128内。

[0044]

表1

[0045][0046][0047]

随着存储器单元的大小减小,其相关联的数据存储结构一般会变小。另外,随着更多数据状态电平存储到存储器单元,区分数据状态会变得更难。

[0048]

存储器单元的阈值电压可归因于例如快速充电损失(qcl)的现象而移位。qcl是栅极电介质接口附近的电子向外释放到存储器单元的沟道区域,且可在编程脉冲之后实时引起vt移位。当存储器单元通过验证操作时,编程阈值电压可归因于栅极电介质中的陷获电荷而显得较高。当在已完成编程操作之后读取存储器单元时,存储器单元可归因于栅极电介质中的电荷漏出到沟道区域而具有比编程验证操作期间所获得的vt低的vt。

[0049]

存储器单元的阈值电压可归因于其编程数据的使用期限(例如编程数据与读取数据之间的时段,本文中称为数据使用期限)内积累的电荷损失而进一步移位。此电荷损失可随着数据存储结构变小而变得更明显。此可准确确定数据状态变得更难,因为存储器单元的阈值电压可足够移位以使其处于比其原始目标数据状态低两个或更多个电平的目标数据状态的阈值电压范围内。各种实施例提供可促进缓解这些问题的设备及方法。

[0050]

由数据使用期限导致的电荷损失可能是可预测的,且一般可展现指数衰减函数。因此,可确定具有已知数据使用期限的存储器单元的预期vt范围。各种实施例寻求确定存储器单元的预期数据使用期限,其可因此提供关于应用于确定所述存储器单元的所欲数据状态时的读取电压的指导。

[0051]

图4a到4b是根据实施例的多个存储器单元的阈值电压分布的概念图。图4a的阈值电压范围430

0

到430

15

可对应于第一数据使用期限内的图3的阈值电压范围330

0

到330

15

,而图4b的阈值电压范围430

0

到430

15

可对应于高于第一数据使用期限的第二数据使用期限内的图3的阈值电压范围330

0

到330

15

。

[0052]

可在确定图4a的各种分布的存储器单元的数据状态时使用读取电压432

0

到432

14

。

例如,当以递增顺序施加读取电压432时,可确定响应于读取电压432

0

而先激活的存储器单元具有对应于阈值电压范围430

0

的数据状态,可确定响应于读取电压432

1

而先激活的存储器单元具有对应于阈值电压范围430

1

的数据状态,可确定响应于读取电压432

2

而先激活的存储器单元具有对应于阈值电压范围430

2

的数据状态,等等。未响应于读取电压432

0

到432

14

中的任何者而激活的存储器单元可被视为具有对应于阈值电压范围430

15

的数据状态。读取操作的最高读取电压与最低读取电压之间的电压范围可表示读取窗434。紧随编程存储器单元之后,读取窗434(例如初始读取窗)可为约6v且(例如)在从-1v到5v的范围内。

[0053]

可在确定图4b的各种分布的存储器单元的数据状态时使用读取电压432

′

0

到432

′

14

。例如,当以递增顺序施加读取电压432'时,可确定响应于读取电压432'

0

而先激活的存储器单元具有对应于阈值电压范围430

0

的数据状态,可确定响应于读取电压432'

1

而先激活的存储器单元具有对应于阈值电压范围430

1

的数据状态,可确定响应于读取电压432'

2

而先激活的存储器单元具有对应于阈值电压范围430

2

的数据状态,等等。未响应于读取电压432'

0

到432'

14

中的任何者而激活的存储器单元可被视为具有对应于阈值电压范围430

15

的数据状态。在图4b的实例中,各种数据状态的阈值电压分布描绘为重叠(归因于通常因电荷损失而发生的扩展)。尽管原本经编程以具有特定数据状态(例如对应于阈值电压范围430

2

的数据状态)的一些存储器单元会被错误视为具有下一较低或下一较高数据状态(例如分别对应于阈值电压范围430

1

及430

3

的数据状态),但可使用错误校正来校正这些错误,如相关技术中所众所周知。

[0054]

由于阈值电压范围430的移位,图4b的读取窗434'可小于图4a的读取窗434。例如,在5个时间十进制之后,读取窗434'可为约5v且(例如)在从-1v到4v的范围内。因此,图4b的读取电压组432

′

0

到432

′

14

一般将需要不同于图4a的读取电压组432

0

到432

14

以更准确确定存储器单元的所欲数据状态。时间十进制经界定使得x时间十进制等于10

x

秒,例如,0时间十进制等于1秒,1时间十进制等于10秒,2时间十进制等于100秒,等等。

[0055]

可基于存储器单元的结构及材料的知识来凭经验确定或直接通过实验来确定依据数据使用期限而变化的所要读取电压(例如线的斜率、多项式的常数或其它特性)。例如,可将各种数据状态(例如伪随机分布)编程到存储器单元群组,且可确定不同数据使用期限内的所得阈值电压。可由这些存储器单元的个别响应拟合复合函数。可针对整个存储器阵列来确定函数,或可基于存储器阵列的某个子部分(例如通过存储器单元块)来确定个别函数。

[0056]

我们提出:响应于给定读取电压而激活的编程存储器单元的存储器单元数目可用于指示编程存储器单元的预期数据使用期限。一般将通常有意使用接近随机分布的数据值分布来编程一页存储器单元。因而,可假定存在编程到每一可能目标数据状态的相等数目个存储器单元。如果将中间读取电压(即,在编程时具有读取窗的最高电压电平与最低电压电平之间的电压电平的读取电压)施加到连接到存储器单元群组(例如一页存储器单元)的存取线,那么可确定响应于所述中间读取电压而激活的存储器单元数目。考虑施加到具有图4a的数据使用期限的存储器单元群组的中间读取电压436的实例。响应于中间读取电压436而激活的存储器单元数目可预期为存储器单元群组(即,用于16个目标数据状态中的每一者的图4a的分布的存储器单元)的13/16或约81%。然而,如果将所述相同中间读取电压436施加到具有图4b的数据使用期限的所述存储器单元群组,那么响应于所述中间读取电

压436而激活的存储器单元数目可预期为超过存储器单元群组的14/16或超过存储器单元群组的约88%。尽管在此实例中讨论为存储器单元群组的分率或百分比,但可使用激活存储器单元的数目中的任何其它表示,例如整数值。因此,针对特定电压电平的中间读取电压所激活的存储器单元的此数目可用于确定存储器单元群组的预期数据使用期限。应注意,尽管中间读取电压436描绘为除任何读取电压432之外的电压电平,但中间读取电压436可替代地具有等于读取电压432的电压电平的电压电平。另外,中间读取电压436可具有读取窗434(例如初始读取窗)之前1/2中的电压电平。中间读取电压436可具有读取窗434(例如初始读取窗)之前1/4中的电压电平。针对一些实施例,中间读取电压436可具有初始读取窗加初始读取窗的宽度的0.70倍到0.95倍的最低电压电平的范围内的电压电平。例如,当初始读取窗在从-1v到5v的范围内时,中间读取电压436可具有-1v+0.70*(5v-(-1v))到-1v+0.95*(5v-(-1v))或3.2v到4.7v的范围内的电压电平。

[0057]

图5是展示根据实施例的存储器单元群组的数据使用期限与响应于特定读取电压而激活的存储器单元数目之间的假想关系的曲线图。可基于存储器单元的结构及材料的知识来凭经验确定或直接通过实验来确定数据使用期限与响应于特定中间读取电压而激活的存储器单元数目之间的关系(例如线的斜率、多项式的常数或其它特性)。例如,各种数据状态(例如伪随机分布)可(例如)在工厂测试期间或在使用期间周期性或间歇性编程到存储器单元群组,且可确定不同数据使用期限内的响应于特定中间读取电压而激活的存储器单元数目。一般通过模拟含有8kb数据的存储器单元群组的读取且假定3.75v的中间读取电压、5v的通过电压、20mv的qlc西格玛(σ)及0.75mv

±

20mv/时间十进制的电荷损失效应来开发图5的实例。从经验或直接原始数据,可针对整个存储器阵列来确定函数,或可基于存储器阵列的某个子部分(例如通过存储器单元页或块)来确定个别函数。替代地,可针对整个存储器阵列或针对存储器阵列的个别子部分(例如通过存储器单元页或块)来自原始数据开发一或多个表。

[0058]

表2是可用于从响应于特定中间读取电压而激活的存储器单元数目确定预期数据使用期限(例如图5的实例中所描绘)的表(例如查找表)的实例。表2的信息可含于(例如)微调寄存器128中。

[0059]

表2

[0060][0061]

表3是可用于从响应于特定中间读取电压而激活的存储器单元数量(例如整数值)

确定预期数据使用期限(例如图5的实例中所描绘)的表的另一实例。表3的信息可含于(例如)微调寄存器128中。

[0062]

表3

[0063][0064]

表4是可用于响应于确定存储器单元群组的预期数据使用期限而确定所要读取电压的表结构的实例。表4的信息可含于(例如)微调寄存器128中。

[0065]

表4

[0066][0067]

参考图4a的实例来考虑表4。rd

0-0

可对应于用于0时间十进制的预期数据使用期限内的读取电压432

0

,rd

0-1

可对应于用于1时间十进制的预期数据使用期限内的读取电压432

0

,rd

0-2

可对应于用于2时间十进制的预期数据使用期限内的读取电压432

0

,等等。剩余读取电压432

1-432

14

可具类似对应性。针对一些实施例,读取电压432

0

的值可在每一时间十进制内保持恒定。一般可预期读取电压430

1

到432

14

的值随时间十进制增大而减小。尽管表2到4的实例仅描绘时间十进制的整数值,但还可利用例如图5中所描绘的中间值。

[0068]

表5是可用于响应于响应于施加中间读取电压而激活的存储器单元数目而确定所要读取电压且不先确定存储器单元群组的预期数据使用期限的表结构的实例。表5的信息可含于(例如)微调寄存器128内。

[0069]

表5

[0070][0071]

在表5中,rd

0-1

可对应于用于指示激活存储器单元的数目的值具有其第一值(例如87.5%)时的读取电压432

0

,rd

0-2

可对应于用于指示激活存储器单元的数目的值具有其第二值(例如88.8%)时的读取电压432

0

,rd

0-3

可对应于用于指示激活存储器单元的数目的值具有其第三值(例如91.5%)时的读取电压432

0

,等等。剩余读取电压432

1-432

14

可具类似对应性。针对一些实施例,读取电压432

0

的值可针对指示激活存储器单元的数目中的每一值保持恒定。一般可预期读取电压430

1

到432

14

的值随时间十进制增大而减小。

[0072]

在使用查找表时,实施例可寻求在不存在准确匹配时插入值之间。替代地,实施例可选择最接近确定值(例如指示激活存储器单元的数目的确定值或确定预期数据使用期限)的表的值。

[0073]

图6是描绘用于与各种实施例一起使用的数据线到页缓冲器及感测装置的连接的框示意图。在图6中,nand串206通过选择门212来选择性连接到数据线204且通过选择门210来连接到源极216。nand串206可具有与参考图2a所描述的结构相同的结构,其具有n+1个存储器单元208

0-208

n

。在读取存储器单元208

0-208

n

中的一者的数据状态时,可激活选择门210及212,可将读取电压施加到连接到针对读取操作所选择的存储器单元(例如目标存储器单元)的存取线(例如所选择存取线),且可将通过电压施加到连接到nand串206的剩余存储器单元(例如每一剩余存储器单元)的存取线(例如未所选择存取线)。例如,如果针对读取操作选择存储器单元208

1

,那么其可在其控制栅极处接收读取电压,其中所述读取电压经配置以在其数据状态对应于低于或等于读取电压的阈值电压时激活存储器单元208

1

及在其数据状态对应于高于读取电压的阈值电压时撤销激活存储器单元208

1

。每一剩余存储器单元208(例如存储器单元208

0

及208

2

到208

n

)可在其控制栅极处接收通过电压,其中所述通过电压经配置以不管其数据状态如何均激活每一剩余存储器单元208。

[0074]

数据线204的状态可指示目标存储器单元208

1

是否处于激活或撤销激活状态中,因为可分别启用或抑制数据线204与源极216之间的电流。接着,可由连接到(例如选择性连接到)数据线204的感测装置640感测此性质,例如通过(例如)使用差分放大器或其类似者来测量电流或所得电压电平或比较电流或所得电压电平与某一阈值。感测装置640的输出可用于设置页缓冲器240的一或多个寄存器。例如,第一寄存器644可为单数字(例如单位)寄存器,其具有指示(例如)响应于感测装置640的感测指示数据线204与源极216之间的电流受抑制而撤销激活目标存储器单元208

1

的第一值(例如第一逻辑电平)。寄存器644可进

一步具有指示(例如)响应于感测装置640的感测指示数据线204与源极216之间的电流被启用而激活目标存储器单元208

1

的第二值(例如不同于第一逻辑电平的第二逻辑电平)。页缓冲器240可进一步包含第二寄存器646,其可为多数字(例如多位)寄存器。响应于感测装置640的感测指示数据线204与源极216之间的电流被启用,页缓冲器240可经配置(例如,响应于将第一寄存器644的值切换到其第二值)以将电压电平的表示648锁存到寄存器646中,例如施加到所选择存取线202

1

的电压电平的表示。以此方式,寄存器646可含有目标存储器单元208

1

的阈值电压的表示,例如改变数据线204的状态的电压电平的表示。时常使用计数器及数/模转换器(dac)(图中未展示)来产生读取操作期间所施加的电压电平,其中计数器的计数可指示从dac输出的电压电平。在此系统中,计数将因此表示所施加的电压电平。

[0075]

使用图6的实例,可将中间读取电压施加到所选择存取线202

1

。数据线204可在(例如)通过将控制信号blclamp(其具有足以激活晶体管650的电压电平)施加到控制信号节点652来激活晶体管(例如n型场效应晶体管或nfet)650之后连接到感测装置640。如果寄存器644响应于由感测装置640感测数据线204的状态而具有其第二逻辑电平,那么存储器单元208

1

可被计数为被激活。可使存储器单元群组的每一存储器单元(将对其执行预期数据使用期限的确定)重复图6的结构,使得具有其第二逻辑电平的寄存器644的数目可指示所述存储器单元群组的激活存储器单元的数目。替代地,可确定撤销激活存储器单元的数目以通过从存储器单元的总数减去撤销激活存储器单元的数目来指示激活存储器单元的数目。

[0076]

图7描绘根据实施例的操作存储器的方法的时序图。例如,图7的时序图可表示存储器的读取操作。迹线760可表示施加到连接到针对读取操作所选择的存储器单元(例如目标存储器单元)的存取线的电压电平。以下讨论将至少参考图2a且将假设针对读取操作所选择的存储器单元是nand串206

0

的存储器单元208

x

,使得迹线760可表示施加到存取线202

x

的电压电平。存取线202

x

可称为所选择存取线(因为其含有目标存储器单元),而剩余存取线202可称为未所选择存取线。nand串206

0

可称为串联连接的存储器单元的所选择串,因为其含有目标存储器单元。迹线762可表示施加到未所选择存取线202(例如存取线202

0

到202

x-1

及202

x+1

到202

n

)中的一或多者的电压电平。迹线764可表示施加到选择线214的电压电平及施加到选择线215的电压电平。

[0077]

在时间t0,预充电相位可开始。读取操作的预充电相位可使未所选择存取线202达到足以激活其相应连接存储器单元(不管其数据状态如何)的电压电平,例如通过电压。如图7的实例中所展示,含有目标存储器单元(例如一或多个目标存储器单元)的存储器单元块的所有存取线202的电压电平首先升高电压电平768。电压电平768可足以激活连接到存取线202的每一存储器单元,不管其数据状态如何。作为一个实例,电压电平768可为约8v。使所有存取线202以此方式一起升高可促进达到任何存取线202的稳态的速度提高,任何存取线202的所要电压电平是电压电平768。可使选择线214及选择线215升高到足以激活其相应选择门的电压电平744。

[0078]

在或约在时间t1,可使所选择存取线202

x

放电到电压电平772。电压电平772可表示希望区分目标存储器单元的可能数据状态的读取电压。例如,如果在将电压电平772施加到存取线202

x

且因此施加到目标存储器单元的控制栅极时激活目标存储器单元,那么目标存储器单元可被视为具有对应于低于或等于电压电平772的阈值电压范围的数据状态。如果在将电压电平772施加到存取线202

x

时撤销激活目标存储器单元,那么目标存储器单元

可被视为具有对应于高于电压电平772的阈值电压范围的数据状态。可在施加电压电平772时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平772可对应于读取电压430

0

。尽管电压电平772经描绘为高于电压电平766,但一些实施例的电压电平772可为负电压电平。

[0079]

当在时间t2将电压电平772施加到所选择存取线202

x

时,将电压电平768施加到未所选择存取线202

0

到202

x-1

及202

x+1

到202

n

。电压电平768足以激活连接到这些未所选择存取线的存储器单元,不管其数据状态如何。另外,当在时间t2将电压电平772施加到所选择存取线202

x

时,将电压电平770施加到选择线214及选择线215。电压电平770可足以激活连接到这些选择线的选择门。以此方式,可在激活目标存储器单元时建立通过nand串206的电流,从而因此允许感测其数据状态。作为一个实例,电压电平774可为约5v。

[0080]

在时间t3,可使施加到所选择存取线202

x

的电压电平增大到电压电平774,同时维持其它迹线762及764的电压电平。电压电平774可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平774时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平774可对应于读取电压430

1

。

[0081]

在时间t4,可使施加到所选择存取线202

x

的电压电平增大到电压电平776,同时维持其它迹线762及764的电压电平。电压电平776可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平776时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平776可对应于读取电压430

2

。

[0082]

在时间t5,可使施加到所选择存取线202

x

的电压电平增大到电压电平778,同时维持其它迹线762及764的电压电平。电压电平778可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平778时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平778可对应于读取电压430

3

。

[0083]

在时间t6,可使施加到所选择存取线202

x

的电压电平增大到电压电平780,同时维持其它迹线762及764的电压电平。电压电平780可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平780时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平780可对应于读取电压430

4

。

[0084]

在时间t7,可使施加到所选择存取线202

x

的电压电平增大到电压电平782,同时维持其它迹线762及764的电压电平。电压电平782可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平782时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平782可对应于读取电压430

5

。

[0085]

在时间t8,可使施加到所选择存取线202

x

的电压电平增大到电压电平784,同时维持其它迹线762及764的电压电平。电压电平784可表示希望区分目标存储器单元的不同可能数据状态的不同读取电压。可在施加电压电平784时执行感测操作,如所属领域中所众所周知。作为一个实例,电压电平784可对应于读取电压430

6

。

[0086]

尽管图7中仅描绘7个读取电压,但可使用其它数目个读取电压。一般可使用y个读取电压来区分y+1个可能数据状态中的每一者。在时间t9,可使所有线放电到电压电平766,电压电平766可为(例如)接地或0v的参考电位。针对读取操作的每一读取电压,时间t2到t9之间的时段可对应于感测一或多个目标存储器单元的数据状态时的读取操作的感测相位。

[0087]

为确定读取操作期间所利用的读取电压,可在读取操作之前或读取操作期间确定

针对读取操作所选择的存储器单元的预期数据使用期限以感测数据状态。图8描绘根据解决预期数据使用期限的此确定的实施例的操作存储器的方法的时序图。

[0088]

在时间t0,预充电相位可开始,如参考图7所描述。在或约在时间t1,可使所选择存取线202

x

放电到电压电平890。电压电平890可表示中间读取电压,例如中间读取电压436。例如,如果在将电压电平890施加到存取线202

x

且因此施加到目标存储器单元的控制栅极时激活目标存储器单元,那么可将其计数到响应于中间读取电压而激活的存储器单元数目中。如果在将电压电平890施加到存取线202

x

时撤销激活目标存储器单元,那么可不将其计数到响应于中间读取电压而激活的存储器单元数目中。可在施加电压电平890时执行感测操作,如所属领域中所众所周知。

[0089]

当在时间t1a将电压电平890施加到所选择存取线202

x

时,可将电压电平768施加到未所选择存取线202

0

到202

x-1

及202

x+1

到202

n

,如参考图7所描述。另外,当在时间t2将电压电平890施加到所选择存取线202

x

时,可将电压电平770施加到选择线214及选择线215,如参考图7所描述。如所属领域中所众所周知,可在施加电压电平890时执行感测操作以确定是否响应于电压电平890而激活目标存储器单元208

x

。如果激活目标存储器单元208

x

,那么寄存器644可锁存其第二逻辑电平,及如果撤销激活目标存储器单元208

x

,那么寄存器644可保持其第一逻辑电平。

[0090]

可计数响应于施加电压电平890而激活的存储器单元数目,例如可执行具有其第二逻辑电平(例如逻辑高电平)的寄存器644的总和。接着,可使用存储器单元的此检测数目(表达为数量、分率或百分比)来确定存储器单元群组的预期数据使用期限,如先前所描述。接着,可响应于确定预期数据使用期限而确定用于感测存储器单元的数据状态的一组读取电压。过程可结束于时间t1b,其中使迹线760、762及764放电到电压电平766,且随后可执行所述存储器单元的读取操作,例如参考图7所描述。

[0091]

替代地,过程可在时间t1b直接继续读取操作,其中使所选择存取线202

x

放电到电压电平772

′

,例如对应于确定预期数据使用期限内的读取电压430

0

。除后续电压电平774

′

、776

′

、778

′

等等可表示确定数据使用期限内的其相应读取电压432之外,可如参考图7所描述那样进行从时间t2及其之后的处理。可(例如)在使所选择存取线202

x

放电之前复位寄存器644以使寄存器准备用于响应于所施加的读取电压而确定目标存储器单元208

x

的数据状态。

[0092]

图9是根据实施例的操作存储器的方法的流程图。例如,图9的方法可为读取操作的一部分,或可在读取操作之前(例如在读取操作之前实时)执行。在901中,可选择中间读取电压。中间读取电压可具有存储器单元群组的初始读取窗内的电压电平。针对一些实施例,可预定中间读取电压,且中间读取电压的表示可含于(例如)微调寄存器128内。

[0093]

在903中,可将中间读取电压施加到针对读取操作所选择的存取线。当将中间读取电压施加到所选择存取线时,可激活未所选择存取线及选择门。在905中,可(例如)通过感测激活或撤销激活多个存储器单元的存储器单元来确定指示连接到所选择存取线的多个存储器单元的激活存储器单元的数目的值。在907中,可响应于指示激活存储器单元的数目的值而确定多个存储器单元的预期数据使用期限,指示激活存储器单元的数目的值由数量、分率、百分比或其它表示。

[0094]

图10是根据另一实施例的操作存储器的方法的流程图。例如,图10的方法可为读

取操作的一部分。在1011中,可将中间读取电压施加到针对读取操作所选择的存取线。当将中间读取电压施加到所选择存取线时,可激活未所选择存取线及选择门。可选择或预定中间读取电压,如参考图9所讨论。

[0095]

在1013中,可(例如)通过感测激活或撤销激活多个存储器单元的存储器单元来确定指示连接到所选择存取线的多个存储器单元的激活存储器单元的数目的值。在1015中,可响应于指示激活存储器单元的数目的值而确定读取操作的多个读取电压。例如,可响应于指示激活存储器单元的数目的确定值而确定多个存储器单元的预期数据使用期限(指示激活存储器单元的数目的值是否由数量、分率、百分比或其它表示),且可响应于多个存储器单元的预期数据使用期限而确定多个读取电压。

[0096]

图11是根据另一实施例的操作存储器的方法的流程图。例如,图11的方法可为读取操作的一部分。在1121中,可选择中间读取电压。中间读取电压可具有存储器单元群组的初始读取窗内的电压电平。针对一些实施例,可预定中间读取电压,且中间读取电压的表示可含于(例如)微调寄存器128内。

[0097]

在1123中,可将中间读取电压施加到针对读取操作所选择的存取线。当将中间读取电压施加到所选择存取线时,可激活未所选择存取线及选择门。在1125中,可(例如)通过感测激活或撤销激活多个存储器单元的存储器单元来确定指示连接到所选择存取线的多个存储器单元的激活存储器单元的数目的值。在1127中,可响应于指示激活存储器单元的数目的值而确定多个存储器单元的预期数据使用期限,指示激活存储器单元的数目的值由数量、分率、百分比或其它表示。

[0098]

在1129中,可响应于多个存储器单元的预期数据使用期限而确定读取操作的多个读取电压。在1131中,可(例如)从多个读取电压的最低读取电压到多个读取电压的最高读取电压将多个读取电压依序施加到所选择存取线。当将多个读取电压施加到所选择存取线时,可激活未所选择存取线及选择门。在1133中,可响应于将多个读取电压施加到所选择存取线而确定多个存储器单元的存储器单元(例如每一存储器单元)的数据状态。针对一些实施例,多个存储器单元可包含连接到所选择存取线的每一存储器单元。针对其它实施例,多个存储器单元可包含连接到所选择存取线的存储器单元的子集(例如真子集),例如连接到所选择存取线的每隔一个存储器单元(例如偶数存储器单元或奇数存储器单元)。

[0099]

结论

[0100]

尽管本文中已说明及描述特定实施例,但所属领域的一般技术人员应了解,经计算以实现相同目的的任何布置可取代所展示的特定实施例。所属领域的一般技术人员应明白实施例的许多调适。因此,本申请案希望涵盖实施例的任何调适或变动。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1