内存运算电路及芯片结构的制作方法

[0001]

本申请涉及存储技术领域,具体涉及一种内存运算电路及芯片结构。

背景技术:

[0002]

图1是现有技术中的内存运算电路的结构示意图,其包括静态随机存取存储器(static random-access memory,sram)100以及一个异或电路200。静态随机存取存储器包括主控制逻辑部分control,其用于控制静态随机存取存储器的读写状态以及预译码;字线(word line)译码xdec;存储阵列array;以及输入输出电路io。其电路工作原理是,将do[x]数据读出,读出的数据和需要比较的数据(compare data)做比较,比较相同则输出0,不同则输出1。do[x]只是静态随机存取存储器中的一个输出举例,实际的工作中可以每一个输出都配上一个需要比较的数据去做比较。

[0003]

采用上述技术方案需要将静态随机存取存储器的值先读出来,然后再通过异或逻辑去做比较。但是,异或逻辑电路的延迟较大。

技术实现要素:

[0004]

本申请实施例的目的在于提供一种内存运算电路及芯片结构,实现在将数据电平在读出之前即可进行异或运算,而无需在读出后进行异或运算,可以降低延迟。

[0005]

本申请实施例提供了一种内存运算电路,包括:

[0006]

存储单元,其具有互补的第一存储点以及第二存储点;

[0007]

第一位线及第二位线,所述第一位线用于读出第一存储点的数据电压,所述第二位线用于读出第二存储点的数据电平;

[0008]

下拉单元,其与第一位线以及第二位线分别连接,其控制端用于接入第一控制信号;以用于在其控制端接入高电平时将第一位线读出的高电平下拉为低电平,将第二位线读出的高电平下拉为低电平;

[0009]

上拉单元,其分别与第一位线以及第二位线连接,其控制端用于接入第二控制信号;以在下拉单元将第一位线下拉为低电平时将所述第二位线上拉为高电平,以及用于在下拉单元将第二位线下拉为低电平时将第一位线上拉为高电平。

[0010]

本申请实施例通过采用上拉单元以及下拉单元实现在将数据电平读出之前即可进行异或运算,而无需在读出后进行异或运算,可以降低延迟,并且可以缩小设计电路所需的版图面积。

[0011]

可选地,在本申请实施例所述的内存运算电路中,所述下拉单元包括第一下拉模块以及第二下拉模块;

[0012]

所述第一下拉模块与所述第一位线连接,其控制端接入第一控制信号;

[0013]

所述第二下拉模块与所述第二位线连接,其控制端接入第一控制信号。

[0014]

本申请实施例通过分别采用第一下拉模块以及第二下拉模块来对该第一位线以及第二位线的高电平进行分别拉低,可以提拉低操作的准确性,避免相互干扰。

[0015]

可选地,在本申请实施例所述的内存运算电路中,所述第一下拉模块包括第一nmos管以及第二nmos管;

[0016]

所述第一nmos管的栅极以及漏极均与所述第一位线连接,所述第一nmos管的源极与所述第二nmos管的漏极连接,所述第二nmos管的源极接地,所述第二nmos管的栅极接入所述第一控制信号;

[0017]

所述第二下拉模块包括第三nmos管以及第四nmos管;

[0018]

所述第三nmos管的栅极以及漏极均与所述第二位线连接,所述第四nmos管的源极与所述第三nmos管的漏极连接,所述第四nmos管的源极接地,所述第四nmos管的栅极接入所述第一控制信号。

[0019]

可选地,在本申请实施例所述的内存运算电路中,所述第一下拉模块还包括第一开关,所述第二nmos管的源极通过所述第一开关接地,所述第一开关接入第三控制信号,所述第一开关用于在所述第二nmos管导通的一个读取周期内导通预设时长;

[0020]

所述第二下拉模块还包括第二开关,所述第四nmos管的源极通过所述第二开关接地,所述第二开关接入第三控制信号,所述第二开关用于在所述第四nmos管导通的一个读取周期内导通预设时长。

[0021]

本申请实施例通过采用在第一下拉模块中引入第一开关,在第二下拉模块中引入第二开关,从而使得该第一位线被上拉单元拉升时,该第一下拉模块不会对该第一位线进行下拉,从而使得该第二位线被上拉单元拉升时,该第二下拉模块不会对该第一位线进行下拉,从而可以提高其第一位线或第二位线输出的高电平的逻辑值的准确性。

[0022]

可选地,在本申请实施例所述的内存运算电路中,所述第一开关以及所述第二开关均为nmos管。

[0023]

可选地,在本申请实施例所述的内存运算电路中,所述上拉单元包括第一pmos管、第二pmos管以及第三开关;

[0024]

所述第三开关的控制端接入所述第四控制信号;所述第三开关的输入端接入预设上拉电压,所述第三开关的输出端分别与所述第一pmos管的源极以及所述第二pmos管的源极连接,所述第一pmos管的漏极与所述第一位线连接,所述第一pmos管的栅极与所述第二位线连接,所述第二pmos管的漏极与所述第二位线连接,所述第二pmos管的栅极与所述第一位线连接。

[0025]

可选地,在本申请实施例所述的内存运算电路中,所述第三开关为pmos管。

[0026]

可选地,在本申请实施例所述的内存运算电路中,所述第四控制信号为所述第三控制信号的反相信号。

[0027]

可选地,在本申请实施例所述的内存运算电路中,还包括一电压差值放大单元;

[0028]

所述电压差值单元分别与所述第一位线以及所述第二位线连接,以用于将所述第一位线以及第二位线中电压较高拉高,电压较低的拉低。

[0029]

本申请实施例通过采用该电压差值放大单元来将该第一位线bl以及第二位线blb中电压较高是拉高,电压较低的拉低,从而提高该第一位线bl以及第二位线blb输出的数据电平的逻辑值的准确性。

[0030]

可选地,在本申请实施例所述的内存运算电路中,所述电压差值放大单元包括:第三pmos管、第四pmos管、第五pmos管、第一反相器、第二反相器、第八pmos管以及第九pmos

管;

[0031]

所述第三pmos管、第四pmos管以及第五pmos管的栅极连接并接入第五控制信号,所述第四pmos管以及第五pmos管的源极连接并接入供电电压,所述第三pmos管的源极与所述第四pmos管的漏极连接并与所述第一反相器的输入端连接于a点,所述第三pmos管的漏极与所述第五pmos管的漏极连接并与所述第二反相器的输入端连接于b点;所述第八pmos管的源极与所述第一位线连接,所述第八pmos管的漏极与a点连接,所述第九pmos管的漏极与所述第二位线连接,所述第九pmos管的源极与b点连接,a点与所述第二反相器的输入端连接,b点与所述第一反相器的输出端连接,所述第八pmos管的栅极与所述第九pmos管的栅极连接并接入第六控制信号。

[0032]

可选地,在本申请实施例所述的内存运算电路中,还包括第五nmos管,所述第五nmos管的漏极与所述第一反相器以及第二反相器的负端连接,所述第五nmos管的源极接地,所述第五nmos管的栅极接入第五控制信号的反相信号。

[0033]

可选地,在本申请实施例所述的内存运算电路中,还包括字线;所述存储单元包括锁存器、第六nmos管以及第七nmos管;

[0034]

所述锁存器包括所述第一存储点以及所述第二存储点;

[0035]

所述字线分别与所述第六nmos管的栅极以及所述第七nmos管的栅极连接,所述第六nmos管的第一端与所述第一位线连接,所述第六nmos管的第二端与所述第一存储点连接;所述第七nmos管的第一端与所述第二位线连接,所述第七nmos管的第二端与所述第二存储点连接。

[0036]

可选地,在本申请实施例所述的内存运算电路中,还包括第一位线开关以及第二位线开关;

[0037]

所述第一位线包括第一上半段以及第一下半段,所述第二位线包括第二上半段以及第二下半段;

[0038]

所述存储单元与所述第一上半段以及所述第二上半段连接,所述第一下半段分别与所述上拉单元以及所述下拉单元连接,所述第二下半段分别与所述上拉单元以及所述下拉单元连接;

[0039]

所述第一位线开关的第一端与所述第一上半段连接,所述第一位线开关的第二端与所述第一下半段连接,所述第二位线开关的第一端与所述第二上半段连接,所述第二位线开关的第二端与所述第二下半段连接,所述第一位线开关以及所述第二位线开关的控制端分别接入位线控制信号。

[0040]

可选地,在本申请实施例所述的内存运算电路中,所述第一位线开关以及第二位线开关均为pmos管。

[0041]

可选地,在本申请实施例所述的内存运算电路中,还包括输出单元,所述输出单元分别与所述第一位线以及第二位线连接,所述输出单元用于输出所述第一位线的电压对应的数值。

[0042]

第二方面,本申请实施例还提供了一种芯片结构,包括上述任一项所述的内存运算电路。

[0043]

由上可知,本申请实施例提供的内存运算电路及芯片结构通过在该第一控制信号为高电平时采用该下拉单元将第一位线bl读出的高电平下拉为低电平,将第二位线blb读

出的高电平下拉为低电平,以及在下拉单元将第一位线bl下拉为低电平时采用上拉单元将第二位线blb上拉为高电平,在下拉单元将第二位线blb下拉为低电平时采用上拉单元将第一位线上拉为高电平,从而实现第一控制信号与该第一位线的读取的第一存储点的数据电平的异或运算,在第一控制信号与该第一位线读取的数据电平相同时,输出低电平也即是0,在该第一控制信号与该第一位线读取的数据电平不相同时,输出高电平,也即是1,从而实现在将数据电平读出之前即可进行异或运算,而无需在读出后进行异或运算,可以降低延迟,缩小设计电路所需的版图面积。

附图说明

[0044]

为了更清楚地说明本申请实施例的技术方案,下面将对本申请实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本申请的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

[0045]

图1是现有技术中的内存运算电路的第一种结构示意图。

[0046]

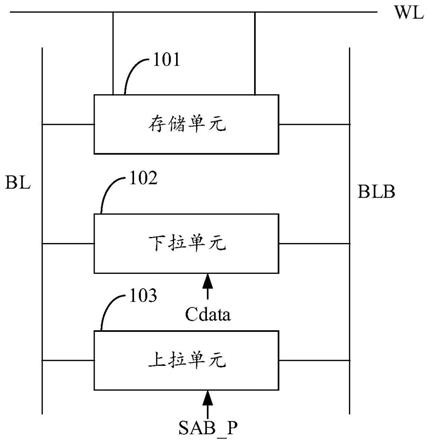

图2是本申请一些施例中的内存运算电路的第一种结构示意图。

[0047]

图3是本申请一些施例中的内存运算电路的第二种结构示意图。

[0048]

图4是本申请一些施例中的内存运算电路的第三种结构示意图。

[0049]

图5是本申请一些施例中的内存运算电路的第四种结构示意图。

[0050]

图6是本申请一些施例中的内存运算电路的第五种结构示意图。

具体实施方式

[0051]

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。

[0052]

在本申请的描述中,需要说明的是,术语“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该申请产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。此外,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0053]

还需要说明的是,除非另有明确的规定和限定,术语“设置”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本申请中的具体含义。

[0054]

请同时参照图2,图2是本申请一些实施例中的一种内存运算电路的结构示意图。该内存运算电路,包括:字线wl、第一位线bl、第二位线blb、存储单元101、下拉单元102以及上拉单元103。该存储单元101分别与该字线wl、第一位线bl以及第二位线blb连接,该下拉单元102分别与该第一位线bl以及该第二位线blb连接,该上拉单元103分别与该第一位线bl以及该第二位线blb连接。

[0055]

其中,该存储单元101具有互补的第一存储点以及第二存储点,以分别存储互补的数据电平。该存储单元101在该字线wl的控制下,通过该第一位线bl读出该第一存储点的数

据电平,通过该第二位线blb读出该第二存储点的数据电平。

[0056]

其中,该下拉单元102的控制端用于接入第一控制信号cdata;以用于在其控制端接入高电平时将第一位线bl读出的高电平下拉为低电平,以及用于将第二位线blb读出的高电平下拉为低电平。

[0057]

其中,该上拉单元103的控制端用于接入第二控制信号。该上拉单元103用于在该第二控制信号的控制下,以在下拉单元102将第一位线bl下拉为低电平时将所述第二位线blb上拉为高电平,以及用于在下拉单元102将第二位线blb下拉为低电平时将第一位线bl上拉为高电平。

[0058]

本申请实施例与图1所示的现有技术相比,通过在该第一控制信号为高电平时采用该下拉单元将第一位线bl读出的高电平下拉为低电平,将第二位线blb读出的高电平下拉为低电平,以及在下拉单元将第一位线bl下拉为低电平时采用上拉单元将第二位线blb上拉为高电平,在下拉单元将第二位线blb下拉为低电平时采用上拉单元将第一位线上拉为高电平,从而实现第一控制信号与该第一位线的读取的第一存储点的数据电平的异或运算,在第一控制信号与该第一位线读取的数据电平相同时,输出低电平也即是0,在该第一控制信号与该第一位线读取的数据电平不相同时,输出高电平,也即是1,从而实现在将数据电平读出之前即可进行异或运算,而无需在读出后进行异或运算,可以降低延迟,缩小设计电路所需的版图面积。

[0059]

请同时参照图3,图3是本申请一些实施例中的内存运算电路的电路结构示意图。其中,该存储单元101包括锁存器1011、第六nmos管n6以及第七nmos管n7。该锁存器1011包括第一存储点q以及所述第二存储点qb;字线wl分别与第六nmos管n6的栅极以及所述第七nmos管n7的栅极连接,所述第六nmos管n6的第一端与所述第一位线bl连接,所述第六nmos管n6的第二端与所述第一存储点q连接;所述第七nmos管n7的第一端与所述第二位线blb连接,所述第七nmos管n7的第二端与所述第二存储点qb连接。其中,该第一端为源极,则该第二端为漏极,该第一端为漏极则该第一端为源极。当该字线wl的电压为高电平时,该第六nmos管n6以及该第七nmos管n7打开,使得该第一位线bl读取该第一存储点q的数据电平,该第二位线blb读取该第二存储点qb的数据电平。

[0060]

其中,该锁存器1011为现有技术中常见的锁存器,其由两个反相器连接形成,该锁存器1011包括pmos管p01、pmos管p02、nmos管n01以及nmos管n02。pmos管p01的源极与该pmos管p02的源极连接并接入该公共电压vdd,该pmos管p01的漏极与该nmos管n01的漏极连接,该nmos管n01的源极接地。该pmos管p01与该nmos管n01的栅极连接于该第一存储点q。该pmos管p02的漏极与该nmos管n02的漏极连接,该nmos管n02的源极接地,该pmos管p02的栅极与该nmos管n02的栅极连接于该第二存储点qb,该第一存储点q与该pmos管p02的漏极以及该nmos管n02的漏极连接,该第二存储点qb与该pmos管p01的漏极以及该nmos管n01的漏极连接。

[0061]

其中,该下拉单元102包括第一下拉模块1021以及第二下拉模块1022。该第一下拉模块1021与该第一位线bl连接,该第二下拉模块1022与该第二位线blb连接。该第一下拉模块1021的控制端接入该第一控制信号cdata,该第二下拉模块1022的控制端接入该第一控制信号cdata。该第一下拉模块1021用于其控制端接入高电平时将第一位线bl读出的高电平下拉为低电平。该第一下拉模块1021用于在其控制端接入高电平时将第二位线blb读出

的高电平下拉为低电平。本申请实施例通过分别采用第一下拉模块以及第二下拉模块来对该第一位线以及第二位线的高电平进行分别拉低,可以提拉低操作的准确性,避免相互干扰。

[0062]

可以理解地,在一些实施例中,该第一下拉模块1021可以包括第一nmos管n1以及第二nmos管n2,该第一nmos管n1的栅极与该第一位线bl连接,该第一nmos管n1的漏极与该第一位线bl连接,该第一nmos管n1的源极与该第二nmos管n2的漏极连接,该第二nmos管n2的源极接地。该第二下拉模块1022可以包括第三nmos管n3以及第四nmos管n4,该第三nmos管n3的栅极与该第二位线blb连接,该第三nmos管n3的漏极与该第二位线blb连接,该第三nmos管n3的源极与该第四nmos管n4的漏极连接,该第四nmos管n4的源极接地。该第二nmos管n2以及该第四nmos管n4的栅极分别接入第一控制信号cdata。

[0063]

可以理解地,在一些实施例中,该第一下拉模块1021还可以包括第一开关t1,该第二nmos管n2的源极通过该第一开关t1接地,该第一开关的控制端接入第三控制信号sa_p。该第一开关t1用于在第二nmos管导通的一个读取周期内导通预设时长;其中,该预设时长小于该一个读取周期。其中,该第一开关t1可以为nmos管,也可以为pmos管,当然,在图3所示实施例中,该第一开关t1为pmos管。

[0064]

对应地,该第二下拉模块1022还包括第二开关t2,该第四nmos管n4的源极通过所述第二开关t2接地,所述第二开关t2接入第三控制信号sa_p,所述第二开关t2用于在所述第四nmos管n4导通的一个读取周期内导通预设时长。其中,该预设时长小于该一个读取周期。其中,该第二开关t2可以为nmos管,也可以为pmos管,当然,在图3所示实施例中,该第二开关t2为pmos管。

[0065]

本申请实施例通过采用在第一下拉模块1021中引入第一开关,在第二下拉模块1022中引入第二开关,从而使得该第一位线被上拉单元拉升时,该第一下拉模块不会对该第一位线进行下拉,从而使得该第二位线被上拉单元拉升时,该第二下拉模块不会对该第一位线进行下拉,从而可以提高其第一位线或第二位线输出的高电平的逻辑值的准确性。

[0066]

其中,该上拉单元103包括第三开关t3、第一pmos管p1以及第二pmos管p2。该第三开关t3的输入端接入该供电电压vdd,该第三开关的输出端与该第一pmos管p1的源极以及该第二pmos管p2的源极连接,该第一pmos管p1的漏极与该第一位线bl连接,该第二pmos管p2的漏极与该第二位线blb连接,该第一pmos管p1的栅极与该第二位线连接,该第二pmos管p2的栅极与该第一位线bl连接。该第一开关的控制端接入第四控制信号sab_p。其中,该第三开关t3可以为nmos管,也可以为pmos管,在图3所示实施例中,其为pmos管,对应地,该第四控制信号sab_p为该第三控制信号sa_p的反相信号。

[0067]

在一些实施例中,该内存运算电路还可以包括一输出单元104,该输出单元104分别与该第一位线bl以及第二位线blb,该输出单元104可以采用数字逻辑电路对该第一位线bl及第二位线blb输出的电压运算后输出对应的数值,0或者1。

[0068]

下面对该内存运算电路的具体工作原理进行详细描述。

[0069]

当该字线wl为低电平时,该第一位线bl以及该第二位线blb均不从该存储单元101读取数据电平。

[0070]

s1、当该字线wl为高电平时,该字线wl将该存储单元101的第六nmos管n6以及该第七nmos管n7打开,该第一位线bl通过该第六nmos管n6从该锁存器1011的第一存储点q读取

数据电平,该第二位线blb通过该第七nmos管n7从该锁存器1011的第二存储点qb读出数据电平。例如,该第一存储点q为高电平,该第二存储点qb为低电平,该第一位线bl被第一存储点q拉升为高电平,该第二位线blb被第二存储点qb拉低为较低电平。

[0071]

如果在读取该存储单元101的数据电平的读取周期内,该第一控制信号cdate保持为高电平,当该第一开关t1的第三控制信号sa_p为高电平时,该第一下拉模块1021的第一nmos管n1、第二nmos管n2以及第一开关t1均导通,因此,该第一位线bl的dl点的高电平被该第一下拉模块1021下拉为低电平。对应地,由于该第二位线blb为低电平时,该第二开关t2打开程度较小几乎关断,因此,该第二下拉模块1022的下拉作用较小,当该dl点被逐渐拉低为低电平时,该第二pmos管p2逐渐打开,对应地,该第三开关t3在第四控制信号sab_p的控制下,保持打开,因此,该dlb点的电压由低电平被该拉升单元103拉高为高电平。因此,可以得出,当该第一控制信号cdata保持为高电平的一个读取周期内,该第一位线输出的电压为低电平(逻辑值为0),与该第一存储点q的存储的数据电压(逻辑值为1)相反。

[0072]

如果在读取该存储单元101的数据电平的读取周期内,该第一控制信号cdate保持为低电平,第一下拉模块1021以及第二下拉模块1022均关断,因此,由于该第一位线bl被第一存储点q拉升为高电平,该第二位线blb被第二存储点qb拉低为较低电平。因此,该第一位线bl输出的电压为高电平(逻辑值为1)。

[0073]

s2、当该字线wl为高电平时,该字线wl将该存储单元101的第六nmos管n6以及该第七nmos管n7打开,该第一位线bl通过该第六nmos管n6从该锁存器1011的第一存储点q读取数据电平,该第二位线blb通过该第七nmos管n7从该锁存器1011的第二存储点qb读出数据电平。例如,该第一存储点q为低电平,该第二存储点qb为高电平,该第一位线bl被第一存储点q拉低为较低电平,该第二位线blb被第二存储点qb拉升为高电平。当然,为了保证该第二位线blb的dlb点的电压被拉升得足够高,因此,该第三开关t3以及该第一pmos管p1的拉升能力强于该第二下拉模块1022的各个mos管的下拉能力,也即是,该第三开关t3以及该第一pmos管p1的尺寸需要大于该第二下拉模块1022的各个mos管的尺寸。

[0074]

如果在读取该存储单元101的数据电平的读取周期内,该第一控制信号cdate保持为高电平,当该第三控制信号sa_p为高电平时,该第二下拉模块2021的第三nmos管n3、第四nmos管n4以及第二开关t2均导通,因此,该第二位线blb的dlb点的高电平被该第二下拉模块1022下拉为较低电平。对应地,第一位线为低电平时,该第一nmos管的打开程度较小,几乎关断,因此,该第二下拉模块1022的下拉作用较小。当该第二位线blb的dlb点被逐渐拉低为低电平时,该第一pmos管p1逐渐打开,对应地,该第三开关t3在第四控制信号sab_p的控制下,保持打开,因此,该第一位线bl的dl点的电压由低电平被该拉升单元103拉高为高电平。因此,可以得出,当该第一控制信号cdate保持为高电平的一个读取周期内,该第一位线bl输出的电压为高电平(逻辑值为1),与该第一存储点q的存储的数据电压(逻辑值为1)相反。当然,为了保证该第一位线blb的dlb点的电压被拉升得足够高,因此,该第三开关t3以及该第二pmos管p2的拉升能力强于该第一下拉模块1021的各个mos管的下拉能力,也即是,该第三开关t3以及该第二pmos管p2的尺寸需要大于该第二下拉模块1022的各个mos管的尺寸。

[0075]

如果在读取该存储单元101的数据电平的读取周期内,该第一控制信号cdate保持为低电平,第一下拉模块1021以及第二下拉模块1022均关断,因此,由于该第一位线bl被第

一存储点q拉低为低电平,该第二位线blb被第二存储点qb拉高为高电平。因此,该第一位线bl输出的电压为低电平(逻辑值为0)。

[0076]

因此,由以上两个步骤可以得到以下真值表:

[0077]

cdataq输出011000101110

[0078]

从而可以得出,当该第一控制信号与该第一存储点的逻辑值相同时,该内存运算电路输出的逻辑值为0,当该第二控制信号与该第一存储点的逻辑值相同时,该内存运算电路输出的逻辑值为1。

[0079]

可以理解地,在一些实施例中,内存运算电路还包括第一位线开关q1以及第二位线开关q2;第一位线bl包括第一上半段以及第一下半段,所述第二位线blb包括第二上半段以及第二下半段。存储单元101与所述第一上半段以及所述第二上半段连接,所述第一下半段分别与所述上拉单元103以及所述下拉单元102连接,所述第二下半段分别与所述上拉单元103以及所述下拉单元102连接;所述第一位线开关的第一端与所述第一上半段连接,所述第一位线开关的第二端与所述第一下半段连接,所述第二位线开关的第一端与所述第二上半段连接,所述第二位线开关的第二端与所述第二下半段连接,所述第一位线开关以及所述第二位线开关的控制端分别接入位线控制信号ymux。其中,该第一位线开关q1以及第二位线开关q2均可以为nmos管或者pmos关。位线控制信号ymux在字线wl关断后(或者说使能结束后),位线控制信号ymux也一起关断,由于位线控制信号ymux控制的是第一位线开关q1以及第二位线开关q2为pmos,所以字线wl是1pulse,位线控制信号ymux是0pulse。这样后续第一位线bl和第二位线blb的值不会受到上拉单元和下拉单元的值的影响。

[0080]

请参照图4,图4是本申请一些实施例中的一种内存运算电路的结构示意图。该内存运算电路,包括:字线wl、第一位线bl、第二位线blb、存储单元201、下拉单元202、上拉单元203、电压差值放大单元204以及输出单元205。该存储单元201分别与该字线wl、第一位线bl以及第二位线blb连接,该下拉单元202分别与该第一位线bl以及该第二位线blb连接,该上拉单元203分别与该第一位线bl以及该第二位线blb连接。该电压差值放大单元204分别与该第一位线bl以及该第二位线blb连接。输出单元205分别与该第一位线bl以及该第二位线blb连接。

[0081]

请同时参照图5,图5是本申请一些实施例中的内存运算电路的具体电路结构图。

[0082]

其中,该存储单元201、下拉单元202、上拉单元203以及输出单元205与上述实施例中的对应结构的结构以及功能相同,因此无需重复描述。

[0083]

其中,该电压差值放大单元204用于将所述第一位线bl以及第二位线blb中电压较高拉高,电压较低的拉低。该电压差值放大单元204包括第三pmos管p3、第四pmos管p4、第五pmos管p5、第一反相器2041、第二反相器2042、第八pmos管p8以及第九pmos管p9。

[0084]

其中,该第三pmos管p3、第四pmos管p4以及第五pmos管p5的栅极连接并接入第五控制信号rcg,第四pmos管p5以及第五pmos管p6的源极连接并接入供电电压vdd,第三pmos管p3的源极与所述第四pmos管p4的漏极连接并与所述第一反相器f1的输入端连接于a点,

所述第三pmos管p3的漏极与所述第五pmos管p5的漏极连接并与所述第二反相器2042的输入端连接于b点;所述第八pmos管p9的源极与所述第一位线bl连接,所述第八pmos管p8的漏极与a点连接,所述第九pmos管p9的漏极与所述第二位线blb连接,所述第九pmos管p9的源极与b点连接,a点与所述第二反相器2042的输入端连接,b点与所述第一反相器2041的输出端连接,所述第八pmos管p8的栅极与所述第九pmos管p9的栅极连接并接入第六控制信号。

[0085]

可以理解地,在一些实施例中,该电压差值放大单元204还包括第五nmos管n5,所述第五nmos管n5的漏极与所述第一反相器2041以及第二反相器2042的负端连接,所述第五nmos管n5的源极接地,所述第五nmos管n5的栅极接入第六控制信号的反相信号saen。可以理解地,该第五控制信号可以由第六控制信号经过该反相器f1反相得到。

[0086]

其中,该第一反相器2041包括pmos管p03以及nmos管n03,该第二反相器2042包括pmos管p04以及nmos管n04。pmos管p03的源极与该pmos管p04的源极连接并接入该公共电压vdd,该pmos管p03的漏极与该nmos管n03的漏极连接,该nmos管n03的源极接地。该pmos管p03与该nmos管n03的栅极连接于该第一存储点q。该pmos管p04的漏极与该nmos管n04的漏极连接,该nmos管n04的源极接地,该pmos管p04的栅极与该nmos管n04的栅极连接于该b点,该a点与该pmos管p04的漏极以及该nmos管n04的漏极连接,该b点与该pmos管p03的漏极以及该nmos管n03的漏极连接。

[0087]

可以理解地,在一些实施例中,内存运算电路还包括第一位线开关q1以及第二位线开关q2;第一位线bl包括第一上半段以及第一下半段,所述第二位线blb包括第二上半段以及第二下半段。存储单元201与所述第一上半段以及所述第二上半段连接,所述第一下半段分别与所述上拉单元203以及所述下拉单元202连接,所述第二下半段分别与所述上拉单元203以及所述下拉单元202连接;所述第一位线开关的第一端与所述第一上半段连接,所述第一位线开关的第二端与所述第一下半段连接,所述第二位线开关的第一端与所述第二上半段连接,所述第二位线开关的第二端与所述第二下半段连接,所述第一位线开关以及所述第二位线开关的控制端分别接入位线控制信号ymux。其中,该第一位线开关q1以及第二位线开关q2均可以为nmos管或者pmos关。

[0088]

本申请实施例通过采用该电压差值放大单元204来将该第一位线bl以及第二位线blb中电压较高拉高,电压较低的拉低,从而提高该第一位线bl以及第二位线blb输出的数据电平的逻辑值的准确性。

[0089]

请参照图6所示,图6是本申请一些实施例中的一种内存运算电路的结构示意图。该内存运算电路,包括:多条字线wl、一条位线bl、一条第二位线blb、多个存储单元301、下拉单元302、上拉单元303、电压差值放大单元304以及输出单元305。

[0090]

该多个存储单元301分别与该多条字线wl一一对应地连接,每一存储单元301分别与该第一位线bl以及第二位线blb连接,该下拉单元302分别与该第一位线bl以及该第二位线blb连接,该上拉单元303分别与该第一位线bl以及该第二位线blb连接。该电压差值放大单元304分别与该第一位线bl以及该第二位线blb连接。输出单元305分别与该第一位线bl以及该第二位线blb连接。

[0091]

该多个存储单元301、下拉单元302、上拉单元303、电压差值放大单元304以及输出单元305与上述任意实施例中的对应结构分别相同,因此不再重复描述。该多个存储单元301的第一存储点的数据电平以及第二存储点的数据电平在该多条字线wl的控制下依次被

该第一位线bl以及第二位线blb读出。

[0092]

当然,如果需要对该多个存储单元301存储的数据电平与第一控制信号进行异或运算,则保持该第一控制信号一直处于高电平状态。

[0093]

本申请实施例还提供了一种芯片结构,该芯片结构包括上述任意实施例中的内存运算电路。

[0094]

以上所述仅为本申请的实施例而已,并不用于限制本申请的保护范围,对于本领域的技术人员来说,本申请可以有各种更改和变化。凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1