非易失性存储器及其相关写入验证方法与流程

[0001]

本发明是有关于一种非易失性存储器及其相关控制方法,且特别是有关于一种非易失性存储器及其相关写入验证方法。

背景技术:

[0002]

众所周知,非易失性存储器在电源停止供应后仍可持续地记录数据,因此非易失性存储器已经广泛地运用在各式电子装置中。一般来说,非易失性存储器可分为一次编程非易失性存储器(one-time programmable non-volatile memory,简称otp非易失性存储器)与多次编程非易失性存储器(multi-time programmable non-volatile memory,简称mtp非易失性存储器)。

[0003]

请参照图1a,其所绘示为现有otp非易失性存储器的示意图。该otp非易失性存储器公开于美国专利us9,627,088。一次编程非易失性存储器300包括:控制电路310、存储单元阵列320、预充电器(precharge driver)330、列选择器(column selector)340、感测放大器(sense amplifier)360与重置器(reset driver)370。

[0004]

存储单元阵列320中包括多个otp存储单元,其中第n行otp存储单元cn1~cn4对应的连接至位线bl1~bl4。

[0005]

控制电路310中包括:电压产生器312、字线驱动器(word line driver)313、列驱动器(column driver)314、时钟产生器315与时序控制器(timing controller)316。电压产生器312可产生供应电压v1与v2至存储单元阵列320。字线驱动器313连接至存储单元阵列320中多条字线,字线驱动器313可驱动其中一条位线使其成为选定位线。列驱动器314可产生列解码信号y1~y4,用以决定位线bl1~bl4其中之一为选定位线。时钟产生器315产生时钟信号clk。时序控制器316接收时钟信号clk,并产生预充电信号ppcg、重置电信号prst与致能信号en。

[0006]

预充电器330中包括4个开关晶体管ma1~ma4,开关晶体管ma1~ma4的控制端接收预充电信号ppcg,开关晶体管ma1~ma4的第一端连接至一预充电电压(precharge voltage)vpcg;开关晶体管ma1~ma4的第二端连接至对应的位线bl1~bl4。当预充电信号ppcg动作时,所有的位线bl1~bl4皆被预充电至预充电电压vpcg。

[0007]

列选择器340中包括4个选择晶体管m1~m4,选择晶体管m1~m4的控制端接收对应的列解码信号y1~y4,选择晶体管m1~m4的第一端连接至对应的位线bl1~bl4;选择晶体管m1~m4的第二端连接至数据线dl。基本上,列驱动器314每次仅会动作列解码信号y1~y4其中之一,以决定选定位线。

[0008]

重置器370中包括一开关晶体管mb,开关晶体管mb的控制端接收重置电信号prst,开关晶体管mb的第一端连接至数据线dl;开关晶体管mb的第二端连接至重置电压vrst(例如接地电压)。当重置电信号prst动作时,数据线dl皆被放电(discharge)至重置电压vrst。

[0009]

感测放大器360中包括一比较器362连接至该数据线dl并接收一比较电压vcmp,并于该致能信号en动作时,根据该数据线dl的一电压准位与该比较电压vcmp来产生一输出信

号dout。

[0010]

基本上,在otp非易失性存储器300中,控制电路310利用字线驱动器313动作其中一条字线,使其成为选定字线(selected word line)。另外,利用列驱动器314的列解码信号y1~y4,用以决定位线bl1~bl4其中之一为选定位线(selected bit line)。而选定字线与选定位线即可决定选定存储单元。而控制电路310在编程动作(program operation)时,可提供特定的供应电压v1与v2用以编程选定存储单元,并使得选定存储单元呈现第一储存状态或者第二储存状态。另外,控制电路310在读取动作(read operation)时,可提供特定的供应电压v1与v2来读取选定存储单元,并确认选定存储单元的储存状态。

[0011]

举例来说,于读取动作时,字线wln与位线bl1动作,则第n行的otp存储单元cn1即为选定存储单元(selected memory cell)。因此,选定存储单元cn1即产生存储单元电流(cell current)经由位线bl1、数据线dl至感测放大器360,用以判断选定存储单元cn1的储存状态。

[0012]

另外,在读取动作时,时序控制器316会动作预充电信号ppcg,并使得所有位线bl1~bl4预充电至预充电电压vpcg。接着,根据字线驱动器313与列驱动器314来决定选定字线与选定位线,并决定选定存储单元且使得选定存储单元对应的位线连接至数据线dl。接着,动作重置电信号prst,使得数据线dl及选定存储单元对应的位线被放电(discharge)至重置电压vrst。之后,于致能信号en动作时,感测放大器360即可判断比较电压vcmp与数据线dl上的电压准位,并据以产生输出信号dout。而输出信号dout即可代表选定存储单元的储存状态。详细说明如下。

[0013]

请参照图1b,其所绘示为otp非易失性存储器于读取动作时的相关信号示意图。其中,时间点t1至时点t6为时钟周期i且字线wln被驱动。

[0014]

首先,于时间点t1至时间点t2,预充电信号ppcg动作,数据线dl被预充电至预充电电压vpcg。接着,于时间点t2至时间点t3,重置电信号prst动作,数据线dl被放电至重置电压vrst。

[0015]

于时间点t3至时间点t4,数据线dl接收选定存储单元的存储单元电流,使得数据线dl上的电压准位由重置电压vrst开始往上变化。基本上,数据线dl上电压准位变化的速度是由选定存储单元的存储单元电流决定。当选定存储单元的存储单元电流较大,数据线dl上电压上升的速度较快;反之,当选定存储单元的存储单元电流较小,数据线dl上电压上升的速度较慢。

[0016]

于时间点t4时,致能信号en动作,并使得致能感测放大器360运作,用以判断比较电压vcmp与数据线dl上的电压准位之间的关系。并且,于时间点t5时,由于比较电压vcmp小于数据线dl上的电压准位,感测放大器360产生第一准位(例如高准位)的输出信号,用以代表选定存储单元为低阻抗的第一储存状态。反之,如果比较电压vcmp大于数据线dl上的电压准位,感测放大器360产生第二准位(例如低准位)的输出信号,用以代表选定存储单元为高阻抗的第二储存状态。

[0017]

相同地,后续时间点t6至时点t11为时钟周期ii,字线wln-1被驱动。感测放大器360可判断另一选定存储单元的储存状态。其运作原理类似,此处不再赘述。

[0018]

相同方式也可以运用于由差分存储单元(differential memory cell)所组成的otp非易失性存储器。请参照图2,其所绘示为现有另一otp非易失性存储器的示意图。

[0019]

otp非易失性存储器500包括:控制电路510、存储单元阵列520、预充电器530、列选择器540、感测放大器560与重置器570。其中,存储单元阵列520中包括多个otp存储单元cn1、cn2,对应的连接至二个位线对bl1、bl1'、bl2、bl2'。

[0020]

预充电器530中包括4个开关晶体管ma1、ma1'、ma2、ma2',开关晶体管ma1、ma1'、ma2、ma2'的控制端接收预充电信号ppcg,开关晶体管ma1、ma1'、ma2、ma2'的第一端连接至一预充电电压vpcg;开关晶体管ma1、ma1'、ma2、ma2'的第二端连接至对应的位线bl1、bl1'、bl2、bl2'。当预充电信号ppcg动作时,所有的位线bl1、bl1'、bl2、bl2'皆被预充电至预充电电压vpcg。

[0021]

列选择器540中包括4个选择晶体管m1、m1'、m2、m2',选择晶体管m1、m1'的控制端接收列解码信号y1,选择晶体管m2、m2'的控制端接收列解码信号y2,选择晶体管m1、m1'、m2、m2'的第一端连接至对应的位线bl1、bl1'、bl2、bl2';选择晶体管m1、m2的第二端连接至数据线dl,选择晶体管m1'、m2'的第二端连接至参考线ref。基本上,列驱动器514每次仅会动作列解码信号y1与y2其中之一,以决定选定位线对。

[0022]

重置器570中包括开关晶体管mb、mb',开关晶体管mb、mb'的控制端接收重置电信号prst,开关晶体管mb的第一端连接至数据线dl,开关晶体管mb的第二端连接至重置电压vrst(例如接地电压);开关晶体管mb'的第一端连接至参考线ref,开关晶体管mb的第二端连接至重置电压vrst。当重置电信号prst动作时,数据线dl与参考线ref皆被放电至重置电压vrst。

[0023]

感测放大器560中包括一比较器562连接至数据线dl与参考线ref,并于该致能信号en动作时,根据该数据线dl的一电压准位与该参考线ref上的该比较电压vcmp来产生一输出信号dout。

[0024]

相同地,根据被驱动的字线与位线对,即可由存储单元阵列中决定一选定存储单元,并编程选定存储单元或者读取选定存储单元。举例来说,当字线wln与位线对bl1与bl1'动作时,otp存储单元cn1即为选定存储单元。此时,子存储单元an1会产生存储单元电流至位线bl1,子存储单元an1'会产生存储单元电流至位线bl1'。

[0025]

因此,在读取动作时,时序控制器516会动作预充电信号ppcg,并使得所有位线bl1、bl1'、bl2、bl2'预充电至预充电电压vpcg。接着,根据字线驱动器513与列驱动器514来决定选定字线与选定位线,并决定选定存储单元且使得选定存储单元对应的位线连接至数据线dl。接着,动作重置电信号prst,使得数据线dl、参考线ref以及选定存储单元对应的位线对被放电(discharge)至重置电压vrst。之后,于致能信号en动作时,感测放大器560即可判断参考线ref上的比较电压vcmp与数据线dl上的电压准位,并据以产生输出信号dout。其详细运作原理不再赘述。

[0026]

由以上的说明可知,现有非易失性存储器在读取动作时,皆是利用选定存储单元产生存储单元电流,并根据存储单元电流的大小来决定选定存储单元的储存状态。当然,现有的读取方式也可以运用在mtp非易失性存储器。

[0027]

另外,图1a中的预充电器330配置于列选择器340与存储单元阵列320之间,于读取动作时可对位线bl1~bl4进行预充电。实际上,预充电器330也可以配置于列选择器340与感测放大器340之间,于读取动作时对数据线dl进行预充电也可以达到相同的读取结果。

[0028]

再者,图1a中的非易失性存储器300中,于读取动作仅能读取一个位(bit)的数据。

适当的扩充预充电器330、列选择器340、感测放大器360、重置器370,可以同时读取非易失性存储器300中的多个位。说明如下。

[0029]

请参照图3,其所绘示为另一非易失性存储器示意图。非易失性存储器600中包括控制电路610、存储单元阵列620、列选择电路640、与感测电路680。

[0030]

存储单元阵列620中包括n

×

m个存储单元。例如m=32,亦即一个行有32个存储单元。再者,第n行的存储单元c1~c32连接至字线wln并连接至对应的位线b1~b32。同理,其他行的32个存储单元也连接对应的字线与位线。其中,存储单元阵列620中的存储单元可为otp存储单元或者mtp存储单元。

[0031]

控制电路610可产生供应电压v1与v2至存储单元阵列620、产生列解码信号y1~y4至列选择电路640、产生预充电信号ppcg至预充电电路630、产生重置电信号prst与致能信号en至感测放大电路660。另外,控制电路610可驱动多条字线其中之一。其中,控制电路610的结构与运作行为类似于图1a的控制电路310,此处不再赘述。

[0032]

再者,32条位线b1~b32被区分为多个部分,例如8个部分,每个部分的位线连接至列选择电路640中对应的列选择器641~648。再者,每个列选择器641~648连接至对应的一部分位线,并且根据列解码信号y1~y4将选定位线连接至数据线。如图3所示,第一部分位线b1~b4连接至列选择器641,且列选择器641根据列解码信号y1~y4将第一部分位线b1~b4中的选定位线连接至数据线dl1。相同地,其他部分位线b5~b32也有类似的连接关系,此处不再赘述。

[0033]

举例来说,当列解码信号y1动作时,列选择器641将选定位线b1连接至数据线dl1、列选择器642将选定位线b5连接至数据线dl2、列选择器643将选定位线b9连接至数据线dl3、列选择器644将选定位线b13连接至数据线dl4、列选择器645将选定位线b17连接至数据线dl5、列选择器646将选定位线b21连接至数据线dl6、列选择器647将选定位线b25连接至数据线dl7、列选择器648将选定位线b29连接至数据线dl8。

[0034]

感测电路680连接至数据线dl1~dl8,并接收预充电信号ppcg、重置信号prst、致能信号en。感测电路680包括8个感测元件(sensing device)681~688。再者,感测电路680中更包括预充电器631~638、重置器671~678与感测放大器661~668配置于每一个感测元件681~688内。以感测元件681为例,预充电器631、重置器671与感测放大器661皆连接至数据线dl1,且感测放大器661可产生输出信号dout1。

[0035]

于读取动作时,预充电器631~638皆根据预充电信号ppcg,将对应的数据线dl1~dl8充电至预充电电压vpcg。重置器671~678皆根据重置信号prst,将对应的数据线dl1~dl8放电至重置电压vrst。感测放大器661~668根据致能信号en来产生输出信号dout1~dout8。其详细运作方式不再赘述。

[0036]

明显地,当致能信号en动作时,8个感测元件681~688共可产生一个字节(byte)的输出信号dout1~dout8,用以代表对应选定存储单元的储存状态。举例来说,于读取动作时,字线wln与列解码信号y1动作时,感测电路660产生的输出信号dout1~dout8分别代表存储单元c1、c5、c9、c13、c17、c21、c25、c29的储存状态。同理,控制电路610动作其他的列解码信号y2~y4动作时,感测电路660即可判断存储单元阵列620中第n行上其他存储单元的储存状态。

[0037]

相同地,图2的非易失性存储器500中,适当的扩充预充电器530、列选择器540、感

测放大器560、重置器570,也可以达成同时读取非易失性存储器500中的多个位。

[0038]

现有的非易失性存储器于编程动作后,仅能于读取动作时输出选定存储单元中的储存状态,无法确认储存于选定存储单元中的写入数据是否正确。

技术实现要素:

[0039]

本发明是有关于一种非易失性存储器及其写入验证方法,于现有非易失性存储器中增加验证电路并搭配感测放大器,用以大幅提高储存于非易失性存储器中写入数据的正确性。

[0040]

本发明是有关于一种非易失性存储器,包括:一存储单元阵列;一列选择电路,连接于该存储单元阵列与多条数据线;一控制电路,连接至该存储单元阵列与该列选择电路,其中该控制电路可决定该存储单元阵列中的多个选定存储单元,并经由该列选择电路将该些选定存储单元连接至该些数据线;一感测电路,连接至该些数据线,其中于进行一读取动作时,该控制电路提供一预充电信号与一致能信号至该感测电路,使得该感测电路产生多个输出信号用以代表该些选定存储单元的储存状态;以及一验证电路,接收多个写入数据与该些输出信号,并产生多个验证信号;其中,于一验证周期时,当该些写入数据与该些输出信号不相符合时,该控制电路依序进行一编程动作与一读取动作,使得该感测电路再次产生该些输出信号至该验证电路,并改变该些验证信号;其中,当该些写入数据与该些输出信号相符合时,该控制电路结束该验证周期。

[0041]

本发明是有关于一种非易失性存储器的写入验证方法,该非易失性存储器包括一存储单元阵列、一列选择电路、一感测电路、一验证电路,该列选择电路连接于该存储单元阵列与多条数据线,该感测电路包括多个感测元件连接至该些数据线,并产生多个输出信号,该验证电路包括多个验证元件接收该些输出信号,并产生多个验证信号,该写入验证方法包括下列步骤:(a)于一验证周期开始时,将多个写入数据输入对应的该些验证元件;(b)进行一读取动作,该感测电路根据一预充电信号与一致能信号产生多个输出信号用以代表该存储单元阵列中多个选定存储单元的储存状态;以及(c)该验证电路判断该些写入数据与该些输出信号,并产生多个验证信号,其中当该些写入数据与该些输出信号相符合时,结束该验证周期,当该些写入数据与该些输出信号不相符合时,对该些选定存储单元进行一编程动作,并回到步骤(b)。

[0042]

为了对本发明的上述及其他方面有更佳的了解,下文特举较佳实施例,并配合附图,作详细说明如下。

附图说明

[0043]

图1a为现有otp非易失性存储器的示意图。

[0044]

图1b为otp非易失性存储器于读取动作时的相关信号示意图。

[0045]

图2为现有另一otp非易失性存储器的示意图。

[0046]

图3为另一非易失性存储器示意图。

[0047]

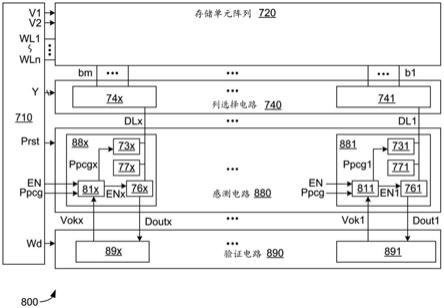

图4a为本发明第一实施例非易失性存储器示意图。

[0048]

图4b为第一实施例非易失性存储器于验证周期的运作流程图。

[0049]

图5a为本发明第二实施例非易失性存储器示意图。

[0050]

图5b为第二实施例非易失性存储器于验证周期的运作流程图。

[0051]

图6a至图6c为逻辑电路的一个范例以及相关信号示意图。

[0052]

图7a至图7h为第二实施例中的感测电路与验证电路在验证周期的运作示意图。

[0053]

符号说明

[0054]

300,500,600,700,800:非易失性存储器

[0055]

310,510,610,710:控制电路

[0056]

312,512:电压产生器

[0057]

313,513:字线驱动器

[0058]

314,514:列驱动器

[0059]

315,515:时钟产生器

[0060]

316,516:时序控制器

[0061]

320,520,620,720:存储单元阵列

[0062]

330,530,631~638,731~73x:预充电器

[0063]

340,540,641~648,741~74x:列选择器

[0064]

360,560,661~668,761~76x:感测放大器

[0065]

362,562:比较器

[0066]

370,570,671~678,771~77x:重置器

[0067]

640,740:列选择电路

[0068]

680,780,880:感测电路

[0069]

681~688,781~78x,881~88x:感测元件

[0070]

790,890:验证电路

[0071]

791~79x,891~89x:验证元件

[0072]

811~81x:逻辑电路

[0073]

901:或门

[0074]

902:非门

[0075]

903:与门

具体实施方式

[0076]

为了改善储存于存储单元中写入数据的正确性,本发明提出一种非易失性存储器,其具备验证电路(verification circuit)。可于验证周期(verification cycle)中,判断储存至选定存储单元中的储存状态是否正确,直到确认选定存储单元中的储存状态与写入数据相符合为止。

[0077]

请参照图4a,其所绘示为本发明第一实施例非易失性存储器示意图。非易失性存储器700中包括控制电路710、存储单元阵列720、列选择电路740、感测电路780与验证电路790。

[0078]

存储单元阵列720中包括n

×

m个存储单元。存储单元阵列720连接至n条字线wl1~wln以及m条位线b1~bm。亦即,每一条字线连接至存储单元阵列720中一行的m个存储单元,且每一行的m个存储单元连接至对应的m条位线b1~bm。举例来说,存储单元阵列720包括64

×

32个存储单元(亦即,n=64,m=32),连接至64条字线以及32条位线。其中,存储单元阵列

720中的存储单元可为otp存储单元或者mtp存储单元。

[0079]

控制电路710可驱动n条字线wl1~wln其中之一。控制电路710可在编程运作与读取运作时,产生特定的供应电压v1与v2至存储单元阵列720。另外,控制电路710更产生列解码信号y至列选择电路740、产生预充电信号ppcg、重置信号prst与致能信号en至感测电路780、产生写入数据wd至验证电路770。

[0080]

再者,m条位线b1~bm被区分为x个部分,对应地连接至列选择电路740中的列选择器741~74x。再者,列选择器741~74x根据列解码信号y将选定位线连接至数据线dl1~dlx。举例来说,m条位线b1~bm被区分为x个部分,每一部分有y条位线。其中,上述的x、y、m、n皆为正整数,且y=m/x。

[0081]

以实际的数字为例来说明,假设存储单元阵列720有32条位线b1~b32,被区分为8个部分,每个部分有4条位线。因此,m=32、x=8、y=4。亦即,位线b1~b4连接至列选择器741、位线b5~b8连接至列选择器742、位线b9~b12连接至列选择器743、位线b13~b16连接至列选择器744、位线b17~b20连接至列选择器745、位线b21~b24连接至列选择器746、位线b25~b28连接至列选择器747、位线b29~b32连接至列选择器748。再者,8个列选择器741~748会根据列解码信号y,将选定位线连接至对应的数据线dl1~dl8。

[0082]

感测电路780连接至数据线dl1~dlx,并接收预充电信号ppcg、重置信号prst、致能信号en。感测电路780包括x个感测元件781~78x。再者,感测电路780中更包括预充电器731~73x、重置器771~77x与感测放大器761~76x配置于每一个感测元件781~78x内。以感测元件781为例,预充电器731、重置器771与感测放大器761皆连接至数据线dl1,且感测放大器761可产生输出信号dout1。

[0083]

于读取动作时,预充电器731~73x皆根据预充电信号ppcg,将对应的数据线dl1~dlx充电至预充电电压vpcg。重置器771~77x皆根据重置信号prst,将对应的数据线dl1~dlx放电至重置电压vrst。感测放大器761~76x根据致能信号en来产生输出信号dout1~doutx。

[0084]

验证电路790接收写入数据wd。验证电路790中包括x个验证元件(verification device)791~79x,连接至对应的感测元件781~78x用以接收对应的输出信号dout1~doutx,并且产生验证信号vok1~vokx。再者,控制电路710更接收验证信号vok1~vokx用以判断选定存储单元中储存数据的正确性。以下以x=8为例来说明验证电路790的运作原理。

[0085]

控制电路710于编程动作时,将一字节的写入数据wd储存至存储单元阵列720中的8个选定存储单元。之后,控制电路710可启动验证周期以判断写入数据是否正确地储存至选定存储单元。

[0086]

请参照图4b,其所绘示为第一实施例非易失性存储器于验证周期的运作流程图。于开始验证周期时,控制电路710会将一字节(8个位)的写入数据wd输入验证电路790中(步骤s701),使得8个验证元件791~798暂存对应的1个位。之后,控制电路710产生预充电信号ppcg、重置信号prst与致能信号en,并控制感测电路780进行读取动作(步骤s702),使得感测元件781~788产生一字节的输出信号dout1~dout8至对应的验证元件791~798。

[0087]

接着,验证电路790判断所有输出信号dout1~dout8是否与所有写入数据wd相符合(步骤s703)。当所有输出信号dout1~dout8与所有写入数据wd相符时,控制电路710结束验证周期,并确认选定存储单元中储存数据的正确性。

[0088]

反之,当输出信号dout1~dout8与写入数据wd之间有任何一个位不相符合时,控制电路710再次进行编程动作(s704),将相同的一字节写入数据wd再此储存至存储单元阵列720中的8个选定存储单元。之后,控制电路710再次进行步骤s702与步骤s703,直到确认选定存储单元中储存数据的正确性为止。

[0089]

基本上,验证电路790比较所有输出信号dout1~dout8与所有写入数据wd后,产生验证信号vok1~vok8。举例来说,验证元件791暂存一位的写入数据,并接收输出信号dout1。当输出信号dout1与暂存的内容相同时,验证元件791产生第一准位的验证信号vok1。反之,当输出信号dout1与暂存的内容不相同时,验证元件791产生第二准位的验证信号vok1。换言之,当所有的验证信号vok1~vok8皆为第一准位时,则控制电路710可确认选定存储单元中储存数据的正确性,并结束验证周期。反之,如果有至少一个验证信号vok1~vok8为第二准位时,则控制电路710可确认选定存储单元中的储存数据不正确,并再次进行编程动作(步骤s704)。

[0090]

当然,控制电路710可以进一步设定编程动作的次数,例如于验证周期中,进行编程动作一特定次数(例如8次)后,控制电路710仍无法确认选定存储单元中数据的正确性,则控制电路710确认验证失败。

[0091]

当验证周期结束之后,控制电路710即可在存储单元阵列720决定另外的8个选定存储单元进行编程动作,并再次启动另一验证周期。如此,即可提高非易失性存储器700中储存数据的正确性。

[0092]

在第一实施例非易失性存储器700中,感测电路780中的每一个感测元件781~78x进行一次读取动作大约会产生0.04μa的电流。以x=8为例,假设控制电路710于验证周期中进行7次读取动作,则感测电路780大约会产生2.24(7

×8×

0.04)μa的电流。

[0093]

再者,修改第一实施例的非易失性存储器700可使得非易失性存储器在验证周期中的耗能更低。

[0094]

请参照图5a,其所绘示为本发明第二实施例非易失性存储器示意图。相较于第一实施例,其差异在于感测电路880与验证电路890,其余电路相同于第一实施例,此处不再赘述。

[0095]

感测电路880连接至数据线dl1~dlx,并接收预充电信号ppcg、重置信号prst、致能信号en。感测电路880包括x个感测元件881~88x。再者,感测电路880中更包括逻辑电路811~81x、预充电器731~73x、重置器771~77x与感测放大器761~76x配置于每一个感测元件881~88x内。

[0096]

以感测元件881为例,感测元件881包括逻辑电路811、预充电器731、重置器771与感测放大器761。逻辑电路811接收预充电信号ppcg、致能信号en、验证信号vok1,并产生本地致能信号(local enable signal)en1至感测放大器761,产生本地预充电信号(local precharge signal)ppcg1至预充电器731。另外,预充电器731、重置器771与感测放大器761皆连接至数据线dl1,且感测放大器761可产生输出信号dout1。

[0097]

根据本发明的第二实施例,于读取动作时,预充电器731~73x皆根据对应的本地预充电信号ppcg1~ppcgx,将对应的数据线dl1~dlx充电至预充电电压vpcg。重置器771~77x皆根据重置信号prst,将对应的数据线dl1~dlx放电至重置电压vrst。感测放大器761~76x根据对应的本地致能信号en1~enx来产生输出信号dout1~doutx。

[0098]

另外,验证电路890接收写入数据wd。验证电路890中包括x个验证元件(verification device)891~89x,连接至对应的感测元件761~76x用以接收对应的输出信号dout1~doutx,并且产生验证信号vok1~vokx。再者,验证信号vok1~vokx回传至对应感测元件881~88x内的逻辑电路811~81x,并且验证信号vok1~vokx也传递至控制电路710用以判断选定存储单元中储存数据的正确性。举例来说,验证元件891~89x中包括锁存器(latch),当输出信号dout1与暂存的内容相同时,验证元件891将验证信号vok1锁存在第一准位的。反之,当输出信号dout1与暂存的内容不相同时,验证元件891将验证信号vok1锁存在第二准位的。以下以x=8为例来说明验证电路890的运作原理。

[0099]

控制电路710于编程动作时,将一字节的写入数据wd储存至存储单元阵列720中的8个选定存储单元。之后,控制电路710可启动验证周期以判断控制电路710是否正确地将写入数据储存至选定存储单元。

[0100]

请参照图5b,其所绘示为第二实施例非易失性存储器于验证周期的运作流程图。于开始验证周期时,控制电路710会将一字节(8个位)的写入数据wd输入验证电路890中(步骤s701),使得8个验证元件891~898暂存对应的一个位(bit)。之后,控制电路710产生预充电信号ppcg、重置信号prst与致能信号en,并控制感测电路880进行读取动作(步骤s702),以产生一字节的输出信号dout1~dout8至对应的验证元件891~89x。

[0101]

接着,验证电路890判断所有输出信号dout1~dout8是否与所有写入数据wd相符合(步骤s703)。当所有输出信号dout1~dout8与所有写入数据wd相符时,控制电路710结束验证周期,并确认选定存储单元中储存数据的正确性。

[0102]

反之,当所有输出信号dout1~dout8与所有写入数据wd不相符时,停止运作输出信号与写入数据相符合的感测元件(步骤s801),仅剩下输出信号与写入数据不相符合的感测元件继续运作。

[0103]

接着,控制电路710再次进行编程动作(s704),将相同的一字节写入数据wd再此储存至存储单元阵列720中的8个选定存储单元。之后,控制电路710再次进行步骤s702与步骤s703,直到确认选定存储单元中储存数据的正确性为止。

[0104]

根据本发明的第二实施例,感测元件881~88x中的逻辑电路881~88x可达成上述步骤s801的功能。以验证元件891为例来作说明,当验证元件891的验证信号vok1被拴锁在第一准位时,代表输出信号dout1与暂存的内容相同。当验证元件891的验证信号vok1被拴锁在第二准位时,代表输出信号dout1与暂存的内容不相同。因此,感测元件881中的逻辑电路811即根据验证信号vok1的准位来决定是否将致能信号en转换为本地致能信号en1,以及将预充电信号ppcg转换为本地预充电信号ppcg1。

[0105]

换言之,假设输出信号dout1与暂存的内容相同时,验证元件891产生第一准位的验证信号vok1至逻辑电路881。此时,就算致能信号en与预充电信号ppcg动作时,逻辑电路881也不会动作本地致能信号en1与本地预充电信号ppcg1,使得感测元件881停止运作。

[0106]

反之,假设输出信号dout1与暂存的内容不相同时,验证元件891产生第二准位的验证信号vok1至逻辑电路881。当致能信号en与预充电信号ppcg动作时,逻辑电路881也会动作本地致能信号en1与本地预充电信号ppcg1,使得感测元件881继续运作。

[0107]

请参照图6a至图6c,其所绘示为逻辑电路的一个范例以及相关信号示意图。假设验证信号vok1的第一准位为高准位(hi),第二准位为低准位(lo)。另外,致能信号en动作时

为高准位,不动作时为低准位。预充电信号动作时为低准位,不动作时为高准位。

[0108]

如图6a所示,逻辑电路881包括一或门901、一非门902与一与门903。或门901的第一输入端接收预充电信号ppcg,或门901的第二端接收验证信号vok1,或门901的输出端产生本地预充电信号ppcg1。非门902的输入端接收验证信号vok1,非门902的输出端产生反相的验证信号vok1。与门903的第一输入端接收反相的验证信号vok1,与门903的第二输入端接收致能信号en,与门903的输出端产生本地致能信号en1。

[0109]

如图6b所示,当验证信号vok1维持在第一准位(hi)时,代表输出信号dout1与暂存的内容相同。当控制电路710进行读取动作而动作预充电信号ppcg与致能信号en时,逻辑电路881将不会动作本地预充电信号ppcg1以及本地致能信号en1,使得感测元件881停止运作。

[0110]

如图6c所示,当验证信号vok1维持在第二准位(lo)时,代表输出信号dout1与暂存的内容不相同。当控制电路710进行读取动作而动作预充电信号ppcg与致能信号en时,逻辑电路881也会对应地动作本地预充电信号ppcg1以及本地致能信号en1,使得感测元件881继续运作。

[0111]

再者,图6a的逻辑电路881仅是一个范例而已,并非用来限定本发明,当致能信号en、预充电信号ppcg与确认信号vok1~vokx的动作准位与上述不同时,可以修改逻辑电路881并达成本发明的目的。

[0112]

以下提供一实际的范例来解释第二实施例非易失性存储器800在验证周期的运作。请参照图7a至图7h,其所绘示为第二实施例中的感测电路880与验证电路890在验证周期的运作示意图。

[0113]

如图7a所示,于验证周期之前的初始(initial)状态,验证元件891~898的验证信号vok1~vok8先被清除为第二准位(lo)。

[0114]

如图7b所示,于验证周期开始后的第一次读取(1st read)动作后,仅有验证信号vok1变更为第一准位(hi),其他验证信号vok2~vok8皆维持在第二准位(lo)。亦即,仅有输出信号dout1与验证元件891暂存的内容相同,因此感测元件881即停止运作,其他感测元件882~888继续运作。

[0115]

如图7c所示,再次进行编程动作与第二次读取(2nd read)动作后,仅有验证信号vok1维持在第一准位(hi),其他验证信号vok2~vok8仍皆维持在第二准位(lo)。亦即,仅有输出信号dout1与验证元件891暂存的内容相同,因此感测元件881停止运作,其他感测元件882~888继续运作。

[0116]

如图7d所示,再次进行编程动作与第三次读取(3rd read)动作后,验证信号vok4变更为第一准位(hi),验证信号vok1维持在第一准位(hi),其他验证信号vok2~vok3与vok5~vok8维持在第二准位(lo)。因此,感测元件881、884停止运作,其他感测元件882~883与885~888继续运作。

[0117]

如图7e所示,再次进行编程动作与第四次读取(4th read)动作后,验证信号vok5变更为第一准位(hi),验证信号vok1与vok4维持在第一准位(hi),其他验证信号vok2~vok3与vok6~vok8维持在第二准位(lo)。因此,感测元件881、884、885停止运作,其他感测元件882~883与886~888继续运作。

[0118]

如图7f所示,再次进行编程动作与第五次读取(5th read)动作后,验证信号vok6

与vok7变更为第一准位(hi),验证信号vok1、vok4、vok5维持在第一准位(hi),其他验证信号vok2~vok3与vok8维持在第二准位(lo)。因此,感测元件881、884~887停止运作,其他感测元件882~883与888继续运作。

[0119]

如图7g所示,再次进行编程动作与进行第六次读取(6th read)动作后,验证信号vok8变更为第一准位(hi),验证信号vok1、vok4~vok7维持在第一准位(hi),其他验证信号vok2~vok3维持在第二准位(lo)。因此,感测元件881、884~888停止运作,其他感测元件882~883继续运作。

[0120]

如图7h所示,再次进行编程动作与进行第七次读取(7th read)动作后,验证信号vok2~vok3变更为第一准位(hi),验证信号vok1、vok4~vok8维持在第一准位(hi)。亦即,所有的验证信号vok~vok8都为第一准位(hi),因此所有感测元件881~888停止运作,且控制电路710确认非易失性存储器800中储存数据的正确性并完成验证动作。

[0121]

第二实施例的非易失性存储器800在验证周期中进行7次读取动作中共有38(8+7+7+6+5+3+2)个验证元件运作,而感测电路880大约会产生1.52(38

×

0.04)μa的电流。相较于第一实施例产生2.24μa的电流,第二实施例的非易失性存储器800可以下降大约0.72(2.24-1.52)μa的电流,仅有第一实施例的68%。

[0122]

再者,本发明于验证周期中感应电路与验证电路的验证方法也同样适用于由差分存储单元所组成的非易失性存储器,详细运作不再赘述。

[0123]

由以上的说明可知,本发明提出一种非易失性存储器及其写入验证方法,可以改善储存于存储单元中写入数据的正确性。本发明的非易失性存储器中包括验证电路,可于验证周期验证选定存储单元中的储存状态是否正确,直到确认选定存储单元中的储存状态与写入数据相符合为止。

[0124]

综上所述,虽然本发明已以较佳实施例公开如上,然而其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,应当可作各种的更动与润饰。因此,本发明的保护范围应当视权利要求书所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1