半导体组件及其制造方法与流程

[0001]

本发明涉及一种集成电路及其制造方法,尤其涉及一种半导体组件及其制造方法。

背景技术:

[0002]

随着科技的进步,各类电子产品皆朝向高速、高效能、且轻薄短小的趋势发展。如何能有效地利用芯片面积,提升良率是目前非常重要的课题。

[0003]

晶圆在切割时因切割锯片的应力可能会产生裂痕,因此,在芯片周围通常会形成密封环,以避免裂痕延伸到芯片区而损坏到内部电路,进而造成良率的损失。然而,密封环或密封环与芯片区之间的区域可能会占用过多的芯片面积。

技术实现要素:

[0004]

本发明实施例提供一种半导体组件的制造方法,可以避免晶圆在切割时因切割锯片的应力产生的裂痕问题,利用布局改变使蚀刻工艺不会损及下层,并且可以减少密封环所占用的芯片面积。

[0005]

本发明实施例提出一种半导体组件的制造方法,包括以下步骤。在衬底上形成彼此分离的第一密封环与第二密封环。在所述衬底上形成保护层,覆盖所述第一密封环与所述第二密封环,其中所述第一密封环与所述第二密封环之间的所述保护层具有凹面。移除位于所述凹面处的所述保护层以及所述第一密封环上的部分所述保护层,于所述第一密封环的侧壁形成间隙壁,并在所述保护层中形成开口,所述开口的宽度大于所述第一密封环的宽度,且所述开口裸露出所述第一密封环的顶面以及所述间隙壁。

[0006]

依照本发明实施例所述,所述凹面与所述衬底的表面之间的导体层的层数小于所述第一密封环的导体层的层数。

[0007]

依照本发明实施例所述,所述凹面位于所述衬底中的隔离结构上方。

[0008]

依照本发明实施例所述,移除位于所述凹面处的所述保护层以及所述第一密封环上的部分所述保护层,并于所述第一密封环的侧壁形成所述间隙壁,并在所述保护层中形成所述开口的步骤包括:在所述保护层上形成掩模层,所述掩模层具有另一开口,裸露出位于所述第一密封环上方的所述保护层以及部分所述凹面;以所述掩模层为掩模,进行各向异性蚀刻工艺,以于所述第一密封环的侧壁形成所述间隙壁,并在所述保护层中形成所述开口;以及移除所述掩模层。

[0009]

本发明实施例提出一种半导体组件,包括第一密封环、第二密封环、间隙壁与保护层。第一密封环与第二密封环彼此分离地设置在衬底上。间隙壁设置于所述第一密封环的第一侧壁。保护层设置在所述衬底上,覆盖所述第一密封环的第二侧壁与所述第二密封环。所述保护层具有开口,裸露出所述第一密封环的顶面与所述间隙壁。

[0010]

依照本发明实施例所述,所述第一密封环与所述第二密封环分别具有多层导体层,其中所述间隙壁位于所述第一密封环的最顶层导体层的部分侧壁。

[0011]

依照本发明实施例所述,所述间隙壁包括与所述保护层相同的材料。

[0012]

依照本发明实施例所述,所述第一密封环的所述最顶层导体层的宽度小于所述第二密封环的所述最顶层导体层的宽度。

[0013]

依照本发明实施例所述,所述第一密封环的所述最顶层导体层的下一层导体层的宽度小于或等于与其上下相邻的两层导体层的宽度。

[0014]

依照本发明实施例所述,所述开口的底面的高度等于或低于所述第一密封环的最顶层导体层的底面的高度。

[0015]

依照本发明实施例所述,所述开口的所述底面裸露出位于所述衬底上的介电层。

[0016]

依照本发明实施例所述,所述开口与所述衬底之间的导体层的层数小于所述第一密封环的导体层的层数。

[0017]

依照本发明实施例所述,所述第一密封环包括多数个第一介层窗,所述第二密封环包括多数个第二介层窗,且所述第一介层窗的数量小于所述第二介层窗的数量。

[0018]

依照本发明实施例所述,所述第一密封环未绕线,所述第二密封环用来绕线。

[0019]

基于上述,第一密封环的宽度小,并且第一密封环与第二密封环之间的间距小,因此可以减少密封环占用的芯片面积。开口(即顶介层窗开口(top via,tv))的宽度大,有助于提升后续于开口中形成的膜层的阶梯覆盖性。

[0020]

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

[0021]

图1a至图1f是依照本发明的实施例的一种半导体组件的制造流程的剖面示意图;

[0022]

图2是芯片的上视图;

[0023]

图3是图2中区域a的局部放大图。

具体实施方式

[0024]

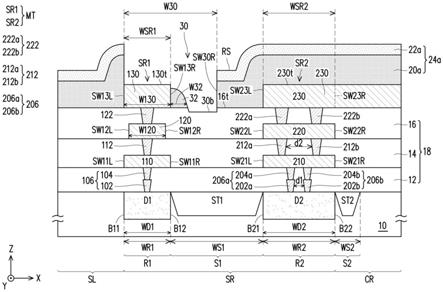

请参照图1a,提供衬底10。衬底10可为半导体衬底10。衬底10可包括芯片区cr、密封环区sr与切割区sl。芯片区cr可用于形成电子组件。切割区sl环绕于芯片区cr周围。在后续进行单体化步骤时,可沿切割区sl进行切割。密封环区sr位于芯片区cr与切割区sl之间。密封环区sr中可以形成密封环,在后续进行单体化步骤时,可以阻挡切割晶圆所产生的裂纹扩及芯片区cr,而损坏芯片区cr之中的电子组件。

[0025]

芯片区cr以及密封环区sr中形成多个隔离结构st1、st2。隔离结构例如是浅沟渠隔离结构。

[0026]

第一隔离结构st1的宽度ws1大于第二隔离结构st2的宽度ws2。在密封环区sr中的第一隔离结构st1将密封环区sr分隔出第一区r1与第二区r2。第一区r1比第二区r2更接近切割区sl。第二区r2比第一区r1更接近芯片区cr。第二区r2介于第一隔离结构st1与第二隔离结构st2之间。在一些实施例中,第一区r1的宽度wr1小于第二区r2的宽度wr2,且第二区r2的宽度wr2小于第一隔离结构st1的宽度ws1。第一区r1的宽度wr1例如是第二区r2的宽度wr2的1/2至2/3,第一隔离结构st1的宽度ws1例如是第二区r2的宽度wr2的1.5倍至2.5倍。举例来说,密封环区sr的宽度例如是4.5μm,其中第一隔离结构st1的宽度ws1例如是2μm、第

一区r1的宽度wr1例如是1μm,第二区r2的宽度wr2例如是1.5μm。

[0027]

请参照图1a,在第一区r1中形成第一掺杂区d1,并在第二区r2中形成第二掺杂区d2。第一掺杂区d1和第二掺杂区d2可以具有相同的导电型与相同的掺杂浓度。第一掺杂区d1和第二掺杂区d2可与衬底10具有相同的导电型,但第一掺杂区d1和第二掺杂区d2的掺杂浓度大于衬底10的掺杂浓度。第一掺杂区d1与第二掺杂区d2可以利用同一个离子注入工艺形成。

[0028]

请参照图1d,在衬底10上形成介电结构18以及金属化结构mt。介电结构18位于衬底10的芯片区cr、密封环区sr与切割区sl上。介电结构18包括内层介电层(ild)12与金属层间介电层(imd)14、16。在本实施例中,层间介电层16是顶层层间介电层,层间介电层14位于顶层层间介电层16与内层介电层12之间,并与其二者物理性接触,内层介电层12位于金属层间介电层与衬底10之间。然而,在其他的实施例中,顶层层间介电层16与层间介电层14之间可以插入一层以上的层间介电层。内层介电层12与金属层间介电层14、16可以分别是单层或是多层。内层介电层12与金属层间介电层的材料可以相同或是不同。内层介电层12与金属层间介电层的材料包括氧化硅、氮化硅、氮氧化硅以及低介电常数材料。低介电常数材料的介电常数(k值)可以低于3.0,甚至低于约2.5,因此低介电常数材料也可称为极低介电常数(elk)材料。内层介电层12与金属层间介电层14、16可以是以化学机械研磨法或是回蚀刻法平坦化的平坦层。

[0029]

金属化结构mt形成于介电结构18之中,且有一部分的金属化结构mt形成于介电结构18之上。金属化结构mt包括金属内连(未示出)、第一密封环sr1(或称为外环)与第二密封环sr2(或称为内环)。金属内连位于芯片区cr。第一密封环sr1与第二密封环sr2分别位于密封环区sr的第一区r1与第二区r2之中。第一密封环sr1与第二密封环sr2分别与第一掺杂区d1以及第二掺杂区d2电性连接,进而接地,使切割过程中产生的静电不会过度集中在第一密封环sr1与第二密封环sr2上,以避免产生静电放电(esd)现象而损坏芯片。

[0030]

金属化结构mt的金属内连、第一密封环sr1与第二密封环sr2可以分别包括多层导体层(导线)110、120、130、210、220、230与多个导体插塞102、104、112、122、202a、202b、204a、204b、212a、212b、222a、222b。导体层与导体插塞的材料可以包括金属、金属合金、金属氮化物,例如是钨、铝、铜、钽、钛、氮化钽、氮化钛等导电材料。

[0031]

在图1a至图1f中,第一层导体层110与导体层120或第一层导体层210与导体层220彼此上下相邻。然而,本发明不以此为限。在其他的实施例中,在第一层导体层110与导体层120之间,或是第一层导体层210与导体层220之间可以插入一层以上的导体层以及一个或多个导体插塞。

[0032]

导体层110、120、210、220设置在介电层12、14中,导体层130、230设置在介电层16上,与衬底10的表面(例如是xy平面)大致平行。多个导体插塞102、104、112、122、202a、202b、204a、204b、212a、212b、222a、222b设置在介电层12、14、16中,纵向(例如是z方向)连接衬底10与第一层导体层110、210,或连接导体层110、120、130、210、220、230中上下相邻的两层导体层。第一密封环sr1与第二密封环sr2的各个导体层110、120、130以及各个导体插塞102、104、112、122呈环状,以环绕芯片区cr的边缘。同样地,第二密封环sr2的各个导体层210、220、230以及各个导体插塞202a、202b、204a、204b、212a、212b、222a、222b呈环状,以环绕芯片区cr的边缘,如图2所示。

[0033]

请参照图1d,第一密封环sr1与芯片区cr的组件以及金属内连电性绝缘。并且,第一密封环sr1通过介电结构18以及第一隔离结构st1与第二密封环sr2物理性以及电性分隔。第二密封环sr2可以与芯片区cr的组件以及金属内连电性连接或电性绝缘。换言之,第一密封环sr1没有绕线(routing),而第二密封环sr2可以允许绕线。

[0034]

金属内连、第一密封环sr1与第二密封环sr2的多个导体层的层数可以相同或是相异。举例来说,金属内连、第一密封环sr1与第二密封环sr2分别具有n层导体层,其中n是介于3~8的整数。换言之,第一密封环sr1与第二密封环sr2的第n层导体层是顶层导体层130、230,其设置在顶层层间介电层16上。第一密封环sr1与第二密封环sr2的第n-1层导体层是导体层120、220,其设置在顶层层间介电层16之中。在以下的内容中所提及的第n-2层导体层未绘示在图1a至图1f中。若是n大于或等于4,则的第n-2层导体层可以是指设置在导体层120与第一层导体层110之间的导体层。若是n等于3,则的第n-2层导体层可以是指第一导体层110。

[0035]

第一密封环sr1的宽度wsr1小于第二密封环sr2的宽度wsr2。此处,所述的第一密封环sr1的宽度wsr1可是指第n-2层导体层至第一层导体层110的平均宽度,所述的第二密封环sr2的宽度wsr2可以是指第n-2层导体层至第一层导体层210的平均宽度。在本实施例中,第一密封环sr1的导体层110、120、130的宽度w110、w120、w130分别小于在同一高度的第二密封环sr2的导体层210、220、230的宽度w210、w220、w230。举例来说,第一密封环sr1的第n-2层导体层至第一层导体层110的宽度w110是第二密封环sr2的第n-2层导体层至第一层导体层210的宽度w210的1/2至2/3。

[0036]

在第一密封环sr1中,顶层导体层(第n层导体层)130的宽度w130大于或等于第一密封环sr1中所有导体层(第一层导体层至第n-2层导体层)110、120的宽度w110、w120。顶层导体层110下方的第n-1层导体层120的宽度w120小于或等于第n层导体层130的宽度w130,且小于或等于第n-2层导体层或第一层导体层110的宽度w110。第n-2层导体层至第一层导体层110可以具有相同宽度。举例来说,第n-1层导体层120的宽度w120是第n层导体层130的宽度w130的50%至70%。第n-1层导体层120的宽度w120是第一层导体层110的宽度w110的70%至80%。顶层导体层(第n层导体层)130设置在第一区r1的顶层层间介电层16上。顶层导体层(第n层导体层)130的接近切割区sl的第一侧壁sw13l可以大致切齐第一区r1的第一边界b11。第n层导体层130得接近第二区r2的侧壁sw13r可以切齐第一区r1的第二边界b12。或者,顶层导体层(第n层导体层)130接近第二区r2的侧壁sw13r可以超出第一区r1的第二边界b12,而沿第二区r2的方向延伸,以覆盖位在部分的第一隔离结构st1上方的顶层层间介电层16。第n-1层导体层120至第一层导体层110设置在第一区r1的顶层层间介电层层16与间介电层14中。第n-1层导体层120的宽度w120小于第一区r1的宽度。换言之,第n-1层导体层120的顶面被顶层导体层130完全遮蔽,第n-1层导体层120的侧壁sw12l与sw12r被位于第一区r1范围内的顶层层间介电层16覆盖。第n-2层导体层至第一层导体层110的宽度w110大致等于第一区r1的宽度wr1。第n-2层导体层至第一层导体层110之各层导体层的两侧壁sw11l、sw11r可以分别大致切齐第一区r1的第一边界b11与第二边界b12。

[0037]

在第二密封环sr2中,在第二区r2相同位置上的第n层导体层230至第一层导体层130可以具有相同宽度。顶层导体层(第n层导体层)230设置在第二区r2的顶层层间介电层16上。顶层导体层(第n层导体层)230的接近第一隔离结构st1的第一侧壁sw23l可以大致切

齐第二区r2的第一边界b21。顶层导体层(第n层导体层)230的接近第二隔离结构st2的侧壁sw23r可以大致切齐第二区r2的第二边界b22。在一些情况下,顶层导体层(第n层导体层)230可以用来绕线,顶层导体层230的侧壁sw23r会超出第二区r2的第二边界b22,并沿芯片区cr的方向延伸,以覆盖位在部分的第二隔离结构st2上方的介电层16,或甚至还延伸至芯片区cr。第n-1层导体层220至第一层导体层210设置在第二区r2的顶层层间介电层16与层间介电层14中。第n-1层导体层220至第一层导体层210的宽度w210大致等于第二区r2的宽度wr2。第n-1层导体层220至第一层导体层110之各层导体层的两侧壁sw22l、sw22r、sw21l、sw21r可以大致切齐第二区r2的第一边界b21与第二边界b22。

[0038]

请参照图1d,第一密封环sr1包括导体插塞102、104、112、122,第二密封环sr2包括导体插塞202a、202b、204a、204b、212a、212b、222a、222b。导体插塞102、104、202a、202b、204a、204b为接触窗(contact),位于内层介电层12之中。接触窗102、104彼此堆叠组成第一接触窗堆叠结构106,以电性连接衬底10的第一掺杂区d1与第一密封环sr1的第一层导体层110。接触窗202a、204a彼此堆叠组成第二接触窗堆叠结构206a,接触窗202b、204b彼此堆叠组成第二接触窗堆叠结构206b,以物理性连接衬底10的第二掺杂区d2与第二密封环sr2的第一层导体层210。

[0039]

导体插塞112、122、212a、212b、222a、222b又称为第一介层窗(via),位于层间介电层14、16之中,可以电性连接第一密封环sr1的导体层110、120、130中上下相邻两层导体层。导体插塞212a、212b、222a、222b又称为第二介层窗,位于层间介电层14、16之中,可以电性连接第二密封环sr2的导体层210、220、230中上下相邻两层导体层。

[0040]

金属内连、第一密封环sr1与第二密封环sr2的导体插塞的数量可以依据实际的需要来设计。第一密封环sr1的导体插塞,可以在后续进行切割时释放应力。第二密封环sr2可以接地,其导体插塞的数量多可以具有较佳的导通效率。因此,在一实施例中,第一密封环sr1的导体插塞的数量小于位于同一水平高度的第二密封环sr2的导体插塞的数量。换言之,在衬底10至第一层导体层110之间,设置于第一区r1之中的第一密封环sr1的第一接触窗堆叠结构106的数量(例如1)小于设置于第二区r2之中的第二密封环sr2的第二接触窗堆叠结构206的数量(例如2或更多)。在第一层导体层110至第n层导体层130之间,设置于第一区r1之中的第一密封环sr1的第一介层窗112或122的数量(例如1)小于设置于第二区r2之中位于同一水平高度的第二密封环sr2的第二介层窗212或222的数量(例如2,或更多)。

[0041]

在第一密封环sr1与第二密封环sr2中,位于衬底10至顶层导体层130、230之间的导体插塞102、104、112、122、202、204、206、212、222可以具有不同的宽度。在一实施例中,第一密封环sr1与第二密封环sr2的导体插塞102、104、112、122、202、204、206、212、222的宽度从衬底10起沿顶层导体层130、230(即,由下而上)的方向逐渐增加。亦即,导体插塞102、202a、202b的宽度最小,导体插塞212、222a、222b的宽度最大。第一密封环sr1的导体插塞(例如112),与第二密封环sr2在同一高度的导体插塞(例如212)可以具有相同的宽度,或不同的宽度。

[0042]

在第一密封环sr1中,自衬底10至顶层导体层130之间的导体插塞102、104、112、122的排列可以大致对准第一区r1的中心线,因此其彼此对齐,或者可以部分重叠。在第二密封环sr2中,位于衬底10至第一层导体层210之间的两个插塞堆叠结构206a、206b之间的距离d1小于位于第一层导体层210与第二层导体层220之间的两个第二介层窗212a、212b之

间的距离d2,而使其彼此相错,且没有重叠,或仅有极少部分重叠。在此,距离d1是指导体插塞202a在半高处的侧壁与导体插塞202b在半高处的侧壁之间的距离。距离d2是指第二介层窗212a在半高处的侧壁与第二介层窗212b在半高处的侧壁之间的距离。位于导体层210与导体层220之间的两个第二介层窗212a、212b,可分别与位于导体层220与导体层230之间的两个介层窗222a、222b部分重叠。

[0043]

请参照图1d、图2与图3,依据实际的需要,密封环区可以分别具有单一宽度或具有多个宽度。密封环区sr环绕芯片区cr的边缘,其包括直线段lp与转角段cp。直线段lp与芯片的边大致平行。转角段cp连接两个不同方向的直线段lp。密封环区sr的直线段lp与转角段cp可以具有相同的宽度或具有不同的宽度。

[0044]

密封环区sr的第一区r1或第二区r2可以分别具有单一宽度或具有多个宽度。举例来说,第一区r1在其转角段cp的宽度wr1c大于直线段lp的宽度wr1l,第二区r2在其转角段cp的宽度wr2c大于直线段lp的宽度wr2l。第一区r1在其转角段cp的宽度wr1c例如是直线段lp的宽度wr1l的1.2倍至1.6倍,第二区r2在其转角段cp的宽度wr2c例如是直线段lp的宽度wr2l的1.2倍至1.6倍。

[0045]

在第一密封环sr1中,同一层的导体层可以具有单一宽度或具有多个宽度。同样地,在第二密封环sr2中,同一层的导体层可以具有单一宽度或具有多个宽度。举例来说,环绕在芯片区cr周围的同一导体层130或230在其转角段cp的宽度可以大于直线段lp的宽度。

[0046]

在第一密封环sr1中,同一导体插塞可以具有单一宽度或具有多个宽度。同样地,在第二密封环sr2中,同一导体插塞可以具有单一宽度或具有多个宽度。举例来说,环绕在芯片区cr周围的同一水平高度的导体插塞122、222a或222b在其转角段cp的宽度可以大于直线段lp的宽度。

[0047]

请参照图1d以及图2,转角段cp与芯片的四个转角之间的区域为虚设区dr。在虚设区dr与第一隔离区s1之中,可以具有多个介电层12、14、16以及位于介电层12之中的半导体层(多晶硅)。由于第一隔离区s1主要为应力释放边界,因此可以无导体层。虚设区dr区无任何导体层或仅有极少导体层,可以避免后续开tv时下层金属层露出来而造成污染。因此,第一隔离区s1与虚设区dr不具有对应金属化结构mt的导体层与导体插塞。或者,仅具有少数对应金属化结构mt的导体层与导体插塞,但介电结构18上不具有顶层导体层。换言之,第一隔离结构st1上的导体层的层数会等于或小于n,且在与第一密封环sr1与第二密封环sr2的顶层导体层130、230相同的水平高度不具有顶层导体层。至此,第一隔离区s1的最顶面(即,介电层16的顶面16t)低于第一区r1与第二区r2的最顶面(即,顶层导体层130的顶面130t以及顶层导体层230的顶面30t)。

[0048]

金属内连、第一密封环sr1与第二密封环sr2可以同时形成或是不同时形成。导体层与导体插塞可以通过沉积、光刻、蚀刻等方法分别形成。在其他实施例中,也可以经由双重金属镶嵌工艺来形成。以下请参照图1a至图1d,说明金属内连、第一密封环sr1与第二密封环sr2的工艺。

[0049]

请参照图1a,在芯片区cr内的衬底10中和/或衬底10上可形成多个电子组件(省略绘示)。电子组件可包括主动组件与被动组件。主动组件例如是晶体管、二极管等。被动组件例如是电阻、电容、电感等。此外,在切割区sl的衬底10中和/或衬底10上可形成对应电子组件的多个测试键或对准标记等。之后,在衬底10上形成介电材料层,并以化学机械研磨工艺

将介电材料层平坦化,以形成介电层12a。

[0050]

然后,进行光刻与蚀刻工艺,在介电层12a中形成接触窗开口。接触窗开口分别例如是呈环状的沟渠。接着,于介电层12a上与接触窗开口之中填入导体材料层。导体材料层的形成方法可以是化学气相沉积法或是物理气相沉积法。接着,对导体材料层进行平坦化工艺,例如是化学机械研磨工艺,以移除介电层12a上的导体材料层,于接触窗开口之中分别形成导体插塞102与202a、202b。

[0051]

之后,以类似的工艺形成介电层12b与导体插塞104与204a、204b。接着,在衬底10上形成导体材料层m1。导体材料层m1的形成方法可以是化学气相沉积法或是物理气相沉积法。

[0052]

之后,请参照图1b,对导体材料层m1进行光刻与蚀刻工艺,以形成导体层110、210。接着,在衬底10上形成介电层14。之后,在介电层14中形成导体插塞112、212a、212b。其后,在衬底10上形成导体材料层m2。

[0053]

接着,请参照图1c,对导体材料层m2进行光刻与蚀刻工艺,以形成导体层120、220。之后,在衬底10上形成介电层16。在介电层16中形成导体插塞122、222a、222b。在衬底10上形成导体材料层m3。

[0054]

之后,请参照图1d,其后,对导体材料层m3进行光刻与蚀刻工艺,以形成导体层130、230。

[0055]

请参照图1e,在衬底10上形成保护层24。保护层24可以是单层或是堆叠结构。在一实施例中,保护层24包括第一保护层20与第二保护层22。第一保护层20覆盖介电结构18的顶面以及顶层导体层130、230的顶面与侧壁。第二保护层22覆盖第一保护层20。第一保护层20包括如二氧化硅、旋涂玻璃(sog)等介电材料。第二保护层22包括如聚亚酰胺、氮化硅等具防水气性质的绝缘材料。第一保护层20的厚度例如是0.8μm至1.5μm,第二保护层的厚度例如是0.3μm至0.8μm。

[0056]

由于第一隔离区s1上的介电层16的顶面16t低于第一区r1的顶层导体层130的顶面130t与第二区r2的顶层导体层230的顶面230t,保护层24会顺应衬底10表面的高低起伏形成,且未经平坦化,因此,在第一隔离区s1上方的保护层24具有凹面rs。

[0057]

之后,请参照图1e,在保护层24上形成掩模层26。掩模层26例如是图案化的光刻胶层。掩模层26具有开口28,裸露出位于第一密封环sr1上方的保护层24以及位于第一隔离区s1上方的保护层24的部分凹面rs。

[0058]

其后,请参照图1e与图1f,以掩模层26为掩模,进行例如是各向异性蚀刻工艺,以在保护层24中形成开口(又称为顶介层开口,tv)30,并在第一密封环sr1的顶层导体层130的侧壁sw13r形成间隙壁32,并且留下保护层24a。之后,将掩模层26移除。在其他的实施例中,保护层24包括感光性材料,可以对保护层24进行曝光显影工艺,以形成开口30。

[0059]

保护层24a的开口30的宽度w30大于第一密封环sr1的宽度wsr1,且大于顶层导体层130的宽度w130。开口30的宽度w30例如是2μm。开口30裸露出第一密封环sr1的顶层导体层130的顶面130t以及间隙壁32。开口30的底面30b位于第一隔离结构st1上方。至此,开口30的底面30b为第一区r1、第二区r2以及第一隔离区s1中表面高度最低之处。在一实施例中,开口30的底面30b较接近第一密封环sr1,且较远离第二密封环sr2。开口30的底面30b裸露出第一隔离结构st1上方的介电结构18的顶层介电层16。开口30的底面30b的高度可以等

于或是低于第一密封环sr1的顶层导体层130的底面130b。举例来说,开口30的底面30b比第一密封环sr1的顶层导体层130的底面130b低约10nm至10nm。

[0060]

在开口30的底面30b的一侧(向第二密封环sr2的方向上),第一隔离结构st1上的介电层16的顶面16t以及第二密封环sr2的顶层导体层230的侧壁sw23l与顶面230t被留下来的保护层24a覆盖,且所留下来的保护层24a(第一保护层20a与第二保护层22a)呈上升阶梯状。在开口30的底面30b的另一侧(向第一密封环sr1的方向上),间隙壁32覆盖在第一密封环sr1的顶层导体层130的侧壁sw13r。所留下来的保护层24a可以使得第一密封环sr1的顶层导体层130的顶面130t全部被裸露出来,或仅有部分的顶面130t被裸露出来。所留下来的保护层24a覆盖第一密封环sr1的顶层导体层130的侧壁sw13l以及切割区sl的介电结构18。

[0061]

间隙壁32可以将第一密封环sr1的顶层导体层130的侧壁sw13r完全覆盖。或者,间隙壁32可以未将第一密封环sr1的顶层导体层130的侧壁sw13r完全覆盖。换言之,间隙壁32的顶面的高度可以等于或是低于第一密封环sr1的顶层导体层130的顶面130t的高度,而无阶梯落差或形成阶梯状。间隙壁32的底面的宽度w32例如是0.2μm至0.4μm。

[0062]

由于导体层120的宽度w120小于顶层导体层130的宽度,因此,在形成开口30的蚀刻过程中,可以避免过度蚀刻,而蚀刻损坏导体层120。再者,间隙壁32也可以提供一个侧向距离,使开口30的底面30b远离导体层120,避免在形成开口30的蚀刻过程中因为过度蚀刻,而蚀刻损坏导体层120。

[0063]

被开口30裸露出来的第一密封环sr1的顶层导体层130可以做为后续切割工艺的切口。由于开口30的宽度w30大于第一密封环sr1的顶层导体层130的宽度w130,并且开口30的侧壁sw30r旁的保护层24a具有阶梯状,因此,有助于测试或封装等相关工艺的进行。举例来说,后续的封装工艺的ubm层可以很容易地填入于本发明的开口30中,而具有较佳的阶梯覆盖性。

[0064]

在本发明的实施例中,第一密封环(外环)未用来绕线,第二密封环(内环)可以用来绕线,因此,可以减少第一密封环的宽度,并且减少第一密封环与第二密封环之间的间距,进而减少密封环占用的芯片面积。再者,第一密封环尺寸较小,上下相邻的两层导体层之间可以仅有一个导体插塞,第二密封环(内环)的尺寸较大,上下相邻的两层导体层之间可以具有两个或多个导体插塞。此外,芯片的四个转角段的虚设区中不形成金属化结构,可以在后续进行芯片切个的工艺中减少裂纹的产生,并将降低工艺中,底层金属露出的风险。顶开口(tv)的宽度大于外环的顶层导体层的宽度,有助于提升后续于开口中形成之膜层的阶梯覆盖性。

[0065]

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1