图像感测装置的制作方法

[0001]

本专利文件中公开的技术和实现方式涉及一种图像感测装置。

背景技术:

[0002]

图像感测装置是用于将光学图像转换成电信号的半导体装置。近年来,随着计算机行业和通信行业的不断发展,各种领域中对高质量和高性能图像传感器的需求迅速增加,这些领域例如为数码相机、便携式摄像机、个人通信系统(pcs)、游戏机、监控摄像机、医疗微型摄像机、机器人等。

技术实现要素:

[0003]

本公开的技术的各种实施方式涉及一种图像感测装置,除其它特征和益处之外,其能够改进8共享像素结构,从而增加源极跟随器的增益和一个或更多个像素信号的转移速率。

[0004]

根据本公开的技术的实施方式,图像感测装置可以包括:像素阵列,其包括按列和行布置的单位像素块。所述单位像素块中的每一个包括:第一子像素块,其包括第一浮置扩散(fd)区和围绕所述第一浮置扩散(fd)区的单位像素;第二子像素块,其包括电联接到所述第一浮置扩散(fd)区的第二浮置扩散(fd)区和围绕所述第二浮置扩散(fd)区的单位像素;以及第一像素晶体管阵列和第二像素晶体管阵列,其设置在所述第一子像素块的在所述第一方向上的相对两侧。所述第二子像素块在第一方向上与所述第一子像素块间隔预定距离。所述第一像素晶体管阵列包括其中第一源极跟随器晶体管和第一选择晶体管串联联接的第一驱动晶体管组。所述第二像素晶体管阵列包括其中第二源极跟随器晶体管和第二选择晶体管串联联接的第二驱动晶体管组。所述第一驱动晶体管组和所述第二驱动晶体管组并联联接。

[0005]

根据本公开的技术的另一实施方式,图像感测装置可以包括:像素阵列,其包括按列和行布置的单位像素块。所述单位像素块中的每一个包括:第一子像素块,其包括第一浮置扩散(fd)区和共享所述第一浮置扩散(fd)区的单位像素;第二子像素块,其包括电联接到所述第一浮置扩散(fd)区的第二浮置扩散(fd)区和共享所述第二浮置扩散(fd)区的单位像素;以及第一源极跟随器晶体管和第二源极跟随器晶体管,其位于所述第一子像素块的在所述第一方向上的相对两侧。所述第二子像素块在第一方向上与所述第一子像素块间隔预定距离。所述第一源极跟随器晶体管和所述第二源极跟随器晶体管沿第一对角线方向布置。

[0006]

根据本公开的技术的又一实施方式,图像感测装置可以包括:像素阵列,其包括按列和行布置的单位像素块。所述单位像素块中的每一个包括:第一子像素块,其被配置为包括第一浮置扩散(fd)区和共享所述第一浮置扩散(fd)区的单位像素;第二子像素块,其被配置为包括电联接到所述第一浮置扩散(fd)区的第二浮置扩散(fd)区和共享所述第二浮置扩散(fd)区的单位像素;以及第一像素晶体管阵列和第二像素晶体管阵列,其设置在所

述第一子像素块的在所述第一方向上的相对两侧。所述第二子像素块在第一方向上与所述第一子像素块间隔预定距离。所述第一像素晶体管阵列包括第一驱动晶体管组,所述第一驱动晶体管组包括第一源极跟随器晶体管和第一选择晶体管。所述第二像素晶体管阵列包括第二驱动晶体管组,所述第二驱动晶体管组包括第二源极跟随器晶体管和第二选择晶体管。所述第一驱动晶体管组和所述第二驱动晶体管组定位成相对于所述第一子像素块彼此对称。

[0007]

应当理解,本公开的技术的上述一般描述和以下详细描述都是说明性和解释性的,并且旨在提供对所要求保护的公开内容的进一步解释。

附图说明

[0008]

当结合附图考虑时,参照以下详细描述,本公开的技术的上述和其它特征以及有益方面将变得显而易见。

[0009]

图1是示出基于本公开的技术的一些实现方式的图像传感器的框图的示例。

[0010]

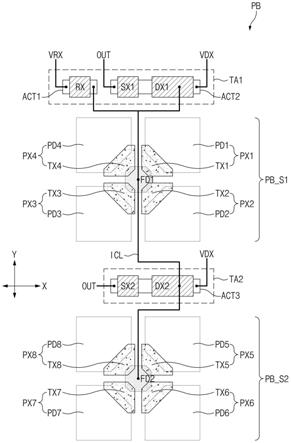

图2是示出基于本公开的技术的一些实现方式的具有8共享像素结构的单位像素块的布局图的示例。

[0011]

图3是示出图2所示的单位像素块的等效电路图的示例。

[0012]

图4是示出基于本公开的技术的一些实现方式的具有8共享像素结构的单位像素块的布局图的另一示例。

[0013]

图5是示出基于本公开的技术的一些实现方式而布置的各自包括8共享像素结构的四个单位像素块的示意图的示例。

[0014]

图6是示出基于本公开的技术的一些实现方式而布置的各自包括8共享像素结构的四个单位像素块的示意图的另一示例。

具体实施方式

[0015]

现在将详细参照某些实施方式,其示例在附图中示出。只要可能,在所有附图中使用相同的附图标记来表示相同或相似的部分。在以下描述中,将省略对并入本文中的相关已知配置或功能的详细描述以避免使主题模糊。

[0016]

图1是示出基于本公开的技术的一些实现方式的图像传感器100的框图的示例。

[0017]

参照图1,图像传感器可以包括像素阵列100、相关双采样器(cds)电路200、模数转换器(adc)电路300、缓冲器400、行驱动器500、定时发生器600、控制寄存器700和斜坡信号发生器800。

[0018]

像素阵列100可以包括按照包括列和行的矩阵形状布置的多个单位像素块(pb)。每个单位像素块(pb)可以包括多个单位像素,并且一些单位像素可被配置成彼此共享浮置扩散(fd)区和像素晶体管。例如,单位像素块(pb)可形成为8共享像素结构,其中8个单位像素中的一些彼此共享浮置扩散(fd)区、复位晶体管、源极跟随器晶体管和选择晶体管。8个单位像素中的四个单位像素可以被配置成共享浮置扩散(fd)区,并且剩余的四个单位像素可以共享另一浮置扩散(fd)区。每个单位像素包括光电转换元件,以用于通过从外部接收的入射光信号的转换来产生光电荷。感光元件可以包括例如光电二极管、光栅、光电晶体管、光电导体或能够产生光电荷的一些其它感光结构。每个单位像素包括传输(tx)晶体管,

以用于将从光电转换元件产生的光电荷传输到浮置扩散(fd)区。例如,每个像素块(pb)可以按如下方式配置:两对源极跟随器晶体管和选择晶体管彼此并联联接,以驱动单个输出节点,这将在本专利文件的后文中做进一步说明。每个单位像素块(pb)可以通过列线向cds电路200输出指示每个单位像素的电子图像信号的像素信号。在一些实现方式中,单位像素块(pb)的输出节点可以联接到列线。单位像素块(pb)可以联接到行线和列线。

[0019]

相关双采样器(cds)电路200可以保持并采样从像素阵列100的单位像素块(pb)接收的像素信号。例如,相关双采样器(cds)电路200可以响应于从定时发生器600接收的时钟信号来执行对接收到的电子图像信号的参考电压电平和电压电平的采样。并且可以将与接收到的电子图像信号的参考电压电平和电压电平之间的差相对应的模拟信号发送到模数转换器(adc)电路300。

[0020]

模数转换器(adc)电路300可以将从斜坡信号发生器800接收的斜坡信号与从相关双采样器(cds)电路200接收的采样信号进行比较,从而可以输出指示斜坡信号和采样信号之间的比较结果的比较信号。模数转换器(adc)电路300可以响应于从定时发生器600接收的时钟信号对比较信号的电平转换时间进行计数,并且可以向缓冲器400输出指示电平转换时间的计数值。

[0021]

缓冲器400可以存储从模数转换器(adc)电路300接收的每个数字信号,可以感测和放大每个数字信号,并且可以输出每个经放大的数字信号。因此,缓冲器400可以包括存储器(未示出)和感测放大器(未示出)。存储器可以存储计数值,并且计数值可以与多个单位像素(px)的输出信号相关联。感测放大器可以感测并且放大从存储器接收的每个计数值。

[0022]

行驱动器500可以响应于定时发生器600的输出信号而驱动像素阵列100的像素块。例如,行驱动器500可以产生能够选择多条行线中的至少一条的控制信号。控制信号可以包括用于控制选择晶体管的选择信号和用于控制稍后将描述的多个转移栅极的传输(tx)信号。

[0023]

定时发生器600可以产生定时信号以控制行驱动器500、相关双采样器(cds)电路200、模数转换器(adc)电路300和斜坡信号发生器800。

[0024]

控制寄存器700可以产生控制信号以控制斜坡信号发生器800、定时发生器600和缓冲器400。

[0025]

斜坡信号发生器800可以响应于从定时发生器600接收的控制信号而产生斜坡信号,以控制从缓冲器400接收的图像信号。

[0026]

图2是示出基于本公开的技术的一些实现方式的具有8共享像素结构的单位像素块的布局图的示例。图3是示出图2所示的单位像素块的等效电路图的示例。

[0027]

参照图2和图3,每个单位像素块pb可以包括8个单位像素px1至px8、两个浮置扩散(fd)区fd1和fd2、两个源极跟随器晶体管dx1和dx2、两个选择晶体管sx1和sx2,以及单个复位晶体管rx。

[0028]

单位像素px1至px8中的每一个可以包括用于响应于入射光而产生光电荷的单个光电转换元件(例如,pd1至pd8中的一个),以及用于将从光电转换元件pd1至pd8中的每一个产生的光电荷传输到浮置扩散(fd)区fd1和fd2的单个传输晶体管(例如,tx1至tx8中的一个)。

[0029]

光电转换元件pd1至pd8中的每一个可以包括有机或无机光电二极管。例如,光电转换元件pd1至pd8可以形成在基板的下部区域(或下部),并且可以包括堆叠结构,其中具有互补导电性的杂质区域(例如,p型杂质区域和n型杂质区域)垂直堆叠。

[0030]

浮置扩散(fd)区fd1和fd2中的每一个可形成在基板的上部区域中,并且可以临时存储通过传输晶体管tx1至tx8接收的光电荷。浮置扩散(fd)区fd1和fd2可以通过互连线(icl)彼此联接。在一些实现方式中,两个浮置扩散(fd)区fd1和fd2彼此共用地联接,使得两个浮置扩散(fd)区fd1和fd2可以由8个单位像素px1至px8共享。此外,浮置扩散(fd)区fd1和fd2可以通过金属线(ml)联接到源极跟随器晶体管dx1和dx2的栅极以及复位晶体管rx的源极区域/漏极区域。

[0031]

传输(tx)晶体管tx1至tx8可以联接在光电转换元件pd1至pd8与浮置扩散(fd)区fd1和fd2之间。在一些实现方式中,传输(tx)晶体管tx1至tx8中的每一个的一端可以联接到光电转换元件pd1至pd8,并且传输(tx)晶体管tx1至tx8中的每一个的另一端可以联接到浮置扩散(fd)区fd1和fd2。传输(tx)晶体管tx1至tx8可以响应于施加到转移栅极的传输(tx)信号而将由光电转换元件pd1至pd8产生的光电荷传输到浮置扩散(fd)区fd1和fd2。

[0032]

被包括在单位像素块(pb)中的8个单位像素px1至px8可以以如下方式设计:8个单位像素px1至px8中的四个单位像素共享单个浮置扩散(fd)区,并且剩余的四个单位像素共享另一单个浮置扩散(fd)区。例如,四个单位像素px1至px4可以布置成围绕浮置扩散(fd)区fd1并且共享浮置扩散(fd)区fd1。剩余的四个单位像素px5至px8可以布置成围绕浮置扩散(fd)区fd2并且共享浮置扩散(fd)区fd2。

[0033]

单位像素块(pb)可以包括第一子像素块pb_s1和第二子像素块pb_s2。第一子像素块pb_s1可以包括共享浮置扩散(fd)区fd1的四个单位像素px1至px4和浮置扩散(fd)区fd1,并且第二子像素块pb_s2可以包括共享浮置扩散(fd)区fd2的四个单位像素px5至px8和浮置扩散(fd)区fd2。

[0034]

在单位像素块pb中,第一子像素块pb_s1和第二子像素块pb_s2可以在y轴方向上彼此隔开预定距离。在一些实现方式中,第一子像素块pb_s1在结构和尺寸上可以与第二子像素块pb_s2相同。

[0035]

像素晶体管阵列ta1可以形成在第一子像素块pb_s1的一侧,并且像素晶体管阵列ta2可以形成在第一子像素块pb_s1的相对侧。像素晶体管阵列ta1、第一子像素块pb_s1和像素晶体管阵列ta2可以沿y轴方向布置。例如,像素晶体管阵列ta2可以设置在子像素块pb_s1和pb_s2之间。

[0036]

像素晶体管阵列ta1可以包括布置在垂直于y轴方向的x轴方向上的复位晶体管rx1、选择晶体管sx1和源极跟随器晶体管dx1。在一些实现方式中,晶体管rx1、sx1和dx1可以按照复位晶体管rx1

→

选择晶体管sx1

→

源极跟随器晶体管dx1的顺序沿从左侧到右侧的方向布置。

[0037]

像素晶体管阵列ta2可以包括沿x轴方向布置的选择晶体管sx2和源极跟随器晶体管dx2。在一些实现方式中,晶体管sx2和dx2可以按照选择晶体管sx2

→

源极跟随器晶体管dx2的顺序沿从左侧到右侧的方向布置。

[0038]

在像素晶体管阵列ta1中,复位晶体管rx可以形成在有源区act1中。复位晶体管rx可以联接在复位电压节点vrx与连接到浮置扩散(fd)区fd1和fd2的另一节点之间。例如,在

有源区act1中,位于复位栅极一侧的源极区/漏极区可以联接到复位电压节点vrx,并且位于复位栅极另一侧的源极区/漏极区可以联接到浮置扩散(fd)区fd1和fd2。

[0039]

在像素晶体管阵列ta1中,选择晶体管sx1和源极跟随器晶体管dx1可以串联联接在驱动电压节点vdx和输出节点out之间。例如,选择晶体管sx1和源极跟随器晶体管dx1可以共享设置在单个有源区act2中并且在选择晶体管sx1的栅极和源极跟随器晶体管dx1的栅极之间的源极区/漏极区。选择晶体管sx1和源极跟随器晶体管dx1可以形成在形成为沿x轴方向延伸的单个有源区act2中。在选择晶体管sx1中,定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到输出节点out。在源极跟随器晶体管dx1中,定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到驱动电压节点vdx。

[0040]

在像素晶体管阵列ta2中,源极跟随器晶体管dx2和选择晶体管sx2可以串联联接在驱动电压节点vdx和输出节点out之间。例如,选择晶体管sx2和源极跟随器晶体管dx2可以共享设置在形成为沿x轴方向延伸的单个有源区act3中的选择晶体管sx2的栅极和源极跟随器晶体管dx2的栅极之间的源极区/漏极区。在选择晶体管sx2中,定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到输出节点out。在源极跟随器晶体管dx2中,定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到驱动电压节点vdx。

[0041]

在一些实现方式中,选择晶体管sx2和源极跟随器晶体管dx2的布置可以关于子像素块pb_s1而与选择晶体管sx1和源极跟随器晶体管dx1的布置对称。在一些实现方式中,像素晶体管阵列ta2中的选择晶体管sx2和源极跟随器晶体管dx2的形状和尺寸可以与像素晶体管阵列ta1中的选择晶体管sx1和源极跟随器晶体管dx2的形状和尺寸相同。例如,源极跟随器晶体管dx1和dx2可以具有相同的尺寸(例如,相同的沟道宽度),并且选择晶体管sx1和sx2可以具有相同的尺寸(例如,相同的沟道宽度)。

[0042]

源极跟随器晶体管dx1和dx2的栅极可以通过金属线联接到浮置扩散(fd)区fd1和fd2。

[0043]

如上所述,单位像素块pb可以以如下方式设计:将源极跟随器晶体管dx1和选择晶体管sx1的串联连接并联联接到源极跟随器晶体管dx2和选择晶体管sx2的串联连接。每个串联连接(即,源极跟随器晶体管dx1和选择晶体管sx1的串联连接和源极跟随器晶体管dx2和选择晶体管sx2的串联连接)设置在驱动电压节点vdx和输出节点out之间。彼此并联联接的源极跟随器晶体管dx1和dx2可以用作具有较大的沟道宽度的单个输出源极跟随器晶体管,并且彼此并联联接的选择晶体管sx1和sx2可以用作具有较大的沟道宽度的单个输出选择晶体管。在这种情况下,由于两个源极跟随器晶体管dx1和dx2一起工作,所以输出源极跟随器晶体管的沟道宽度可以增加。类似地,由于两个选择晶体管sx1和sx2一起工作,所以输出选择晶体管的沟道宽度可以增加。

[0044]

因此,单位像素块(pb)可以使用并联联接的两个源极跟随器晶体管dx1和dx2以及并联联接的两个选择晶体管sx1和sx2来驱动单个输出节点out,使得单位像素块pb可以将像素信号输出到被联接到输出节点out的单条列线。

[0045]

如上所述,由于被包含在单位像素块pb中的源极跟随器晶体管和选择晶体管的沟道宽度相对增大,所以可以改善源极跟随器增益。此外,由于减少了每个选择晶体管的电阻,所以可以增加像素信号的转移速率。

[0046]

尽管为了便于描述,图2示出了像素晶体管阵列ta1和ta2设置在子像素块pb_s1的

两侧,但是其它实现方式也是可能的。在一些其它实现方式中,像素晶体管阵列ta1和ta2可以布置在子像素块pb_s2的两侧。例如,像素晶体管阵列ta1也可以形成在子像素块pb_s2下方。

[0047]

图4示出了基于本公开的技术的一些实现方式的具有8共享像素结构的单位像素块的布局图的另一示例。

[0048]

图4所示的单位像素块pb在像素晶体管阵列ta1和ta2的位置方面不同于图2所示的单位像素块pb。

[0049]

例如,在图4所示的单位像素块pb中,像素晶体管阵列ta2可以形成在第一子像素块pb_s1的一侧,并且像素晶体管阵列ta1可以形成在第一子像素块pb_s1的相对侧。像素晶体管阵列ta2、第一子像素块pb_s1和像素晶体管阵列ta1可以沿y轴方向顺序布置。例如,像素晶体管阵列ta1可以设置在子像素块pb_s1和pb_s2之间。

[0050]

除了像素晶体管阵列ta1和ta2的位置之外,图4所示的单位像素块pb的组成元件可以与图2所示的单位像素块pb的组成元件相同。为了简明起见,这里将省略其详细描述。

[0051]

图5是示出基于本公开的技术的一些实现方式而布置的各自包括8共享像素结构的四个单位像素块的示意图的示例。

[0052]

参照图5,像素阵列100可以包括沿x轴方向布置的四个单位像素块pb1至pb4。像素阵列100可以包括沿x轴和y轴方向布置的多个四单位像素块。为了便于描述,图5所示的四个单位像素块pb1至pb4在下文中将被称为单位像素块组。

[0053]

单位像素块pb1至pb4可以包括8个单位像素、两个浮置扩散(fd)区fd1和fd2、两个源极跟随器晶体管dx11至dx42、两个选择晶体管sx11至sx42和单个复位晶体管(rx1至rx4)。每个单位像素可以包括单个光电转换元件pd1至pd8和单个传输(tx)晶体管tx1至tx8。

[0054]

在单位像素块pb1至pb4中的每一个中,浮置扩散(fd)区fd1和fd2可以由围绕浮置扩散(fd)区fd1和fd2的四个单位像素共享,并且浮置扩散(fd)区fd1和fd2可以彼此联接。在一些实现方式中,单位像素块pb1至pb4中的每一个可以包括两个子像素块(例如,图2中所描绘的pb_s1和pb_s2),两个子像素块中的每一个包括四个单位像素和由四个单位像素共享的单个浮置扩散(fd)区。浮置扩散(fd)区fd1和fd2可以通过金属线联接到源极跟随器晶体管dx11至dx42的栅极和复位晶体管rx1至rx4的源极区/漏极区。

[0055]

在每个单位像素块pb1至pb4中,子像素块pb_s1和pb_s2可以在y轴方向上彼此隔开预定距离。

[0056]

在单位像素块pb1至pb4中的每一个中,两个源极跟随器晶体管、两个选择晶体管和单个复位晶体管可以设置在子像素块pb_s1的在y轴方向上的侧方中的一侧。例如,像素晶体管阵列可以分别形成在子像素块pb_s1的在y轴方向上的两侧。因此,单位像素块pb1至pb4中的每一个可以包括分别设置在子像素块pb_s1两侧的两个像素晶体管阵列ta1和ta2。

[0057]

每个单位像素块pb1至pb4中的像素晶体管阵列ta1可以包括沿x轴方向布置的复位晶体管、选择晶体管和源极跟随器晶体管。例如,复位晶体管rx1、选择晶体管sx11和源极跟随器晶体管dx11可以在子像素块pb_s1的一侧(例如顶侧)沿x轴方向布置。

[0058]

每个单位像素块pb1至pb4中的像素晶体管阵列ta2可以包括沿x轴方向布置的选择晶体管和源极跟随器晶体管。例如,选择晶体管sx12和源极跟随器晶体管dx12可以在子

像素块pb_s1的另一侧(例如底侧)沿x轴方向布置。

[0059]

在以下描述中,包括复位晶体管rx1至rx4的像素晶体管阵列将被称为第一像素晶体管阵列,而不包括复位晶体管rx1至rx4的像素晶体管阵列将被称为第二像素晶体管阵列。

[0060]

在第一像素晶体管阵列中,复位晶体管rx1至rx4可以联接在复位电压节点vrx与连接到浮置扩散(fd)区fd1和fd2的另一节点之间。例如,复位晶体管rx1至rx4中的每一个可以与选择晶体管sx11至sx42和源极跟随器晶体管dx11至dx42分开地形成在单个有源区中。在对应的有源区中,位于复位栅极一侧的源极区/漏极区可以联接到复位电压节点vrx,并且位于复位栅极另一侧的源极区/漏极区可以联接到对应单元块pb1至pb4的浮置扩散(fd)区fd1和fd2。

[0061]

在第一像素晶体管阵列和第二像素晶体管阵列中,选择晶体管sx11至sx42和源极跟随器晶体管dx11至dx42可以串联联接在驱动电压节点vdx和输出节点out1至out4之间。例如,每个选择晶体管和每个源极跟随器晶体管可以共享设置在单个有源区中并且在选择晶体管的栅极和源极跟随器晶体管的栅极之间的源极区/漏极区。选择晶体管和源极跟随器晶体管形成在被形成为沿x轴方向延伸的单个有源区中。选择晶体管sx11至sx42的定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到输出节点out1到out4。源极跟随器晶体管dx11至dx42的定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到驱动电压节点vdx。

[0062]

单位像素块pb1至pb4中的每一个包括两个驱动晶体管组,并且每一驱动晶体管组包括彼此串联联接的一个源极跟随器晶体管和一个选择晶体管。两个驱动晶体管组可以彼此并联联接在驱动电压节点vdx和输出节点out1至out4之间。

[0063]

在一些实施方式中,在单位像素块pb1至pb4中的每一个中,两个驱动晶体管组的结构和尺寸可以彼此相同,并且可以设置在子像素块pb_s1或pb_s2的两侧。在图5的示例中,两个驱动晶体管组设置在子像素块pb_s1的两侧,以相对于子像素块pb_s1对称。

[0064]

在单位像素块pb1至pb4中的每一个中,第一像素晶体管阵列的长度可以大于子像素块pb_s1和pb_s2中的每一个的长度。例如,第一像素晶体管阵列可以在x轴方向上突出超过子像素块pb_s1和pb_s2中的每一个。因此,可以沿x方向测量第一像素晶体管阵列的长度。例如,被包括在第一像素晶体管阵列中的复位晶体管可以定位成从子像素块pb_s1和pb_s2中的每一个的边缘突出。在单位像素块pb1至pb4中的每一个中,第二像素晶体管阵列的长度可以小于子像素块pb_s1和pb_s2中的每一个的长度。

[0065]

在下文中,将参照附图描述被包括在单位像素块组中的单位像素块pb1至pb4之间的结构差异。

[0066]

参照图5,在单位像素块pb1中,第一像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上侧,并且第二像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的另一侧,例如下侧。因此,第二像素晶体管阵列可以设置在子像素块pb_s1和pb_s2之间,以与第一像素晶体管阵列相对。

[0067]

类似地,在定位成与单位像素块pb1相邻的单位像素块pb2中,第一像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上侧,并且第二像素晶体管阵列可以设置在子像素块pb_s1的另一侧,例如下侧。因此,第二像素晶体管阵列可以设置在子

像素块pb_s1和pb_s2之间,以与第一像素晶体管阵列相对。

[0068]

第一单位像素块pb1的第一像素晶体管阵列和单位像素块pb2的第一像素晶体管阵列可以相对于单位像素块pb1和pb2之间的边界线彼此对称地布置。因此,单位像素块pb1的第一像素晶体管阵列包括尺寸与单位像素块pb2的第一像素晶体管阵列中所包括的晶体管的尺寸相同的晶体管。然而,单位像素块pb1的第一像素晶体管阵列的组成元件的布置顺序不同于单位像素块pb2的第一像素晶体管阵列的组成元件的布置顺序。例如,沿着从左向右的x方向,复位晶体管rx1、选择晶体管sx11和源极跟随器晶体管dx11依次布置在单位像素块pb1中。与在单位像素块pb1中不同,沿着从左向右的x方向,源极跟随器晶体管dx21、选择晶体管sx21和复位晶体管rx2依次布置在单位像素块pb2中。单位像素块pb1和pb2的第一像素晶体管阵列的上述布置结构可以被称为倒装形状(flip-shaped)布置结构。在此情况下,单位像素块pb1的第一像素晶体管阵列的源极跟随器晶体管dx11可以定位成与单位像素块pb2的第一像素晶体管阵列的源极跟随器晶体管dx21相邻,并且源极跟随器晶体管dx11和dx21可以共享同一驱动电压节点vdx。

[0069]

同样地,单位像素块pb1的第二像素晶体管阵列和单位像素块pb2的第二像素晶体管阵列可以形成为倒装形状结构,并且相对于单位像素块pb1和pb2之间的边界线彼此对称地布置。单位像素块pb1的第二像素晶体管阵列的源极跟随器晶体管dx12可以定位成与单位像素块pb2的第二像素晶体管阵列的源极跟随器晶体管dx22相邻,并且源极跟随器晶体管dx12和dx22可以共享驱动电压节点vdx。

[0070]

在定位成与单位像素块pb2相邻的单位像素块pb3中,第二像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上侧,并且第一像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的另一侧,例如下侧。因此,第一像素晶体管阵列可以设置在子像素块pb_s1和pb_s2之间,以与第二像素晶体管阵列相对。

[0071]

在一些实现方式中,单位像素块pb2的第一像素晶体管阵列和单位像素块pb3的第二像素晶体管阵列可以沿x轴方向布置,并且单位像素块pb2的第二像素晶体管阵列和单位像素块pb3的第一像素晶体管阵列可以沿x轴方向布置。因此,在单位像素块pb2和pb3之间的边界区域周围,单位像素块pb2的第一像素晶体管阵列的突出部分(复位晶体管rx2位于该突出部分中)可以定位成与单位像素块pb3的第二像素晶体管阵列相邻。由于单位像素块pb3的第二像素晶体管阵列不包括复位晶体管,因此第二像素晶体管阵列具有从单位像素块pb2和pb3之间的边界区域凹入的形状。单位像素块pb2的第一像素晶体管阵列的突出部分可以位于单位像素块pb3的第二像素晶体管阵列的凹入部分中。

[0072]

在单位像素块pb3中,被包含在第一像素晶体管阵列中的晶体管可以与被包含在单位像素块pb1的第一像素晶体管阵列中的晶体管按照相同的顺序布置,并且被包含在第二像素晶体管阵列中的晶体管可以与被包含在单位像素块pb1的第二像素晶体管阵列中的晶体管按照相同的顺序布置。

[0073]

在定位成与单位像素块pb3相邻的单位像素块pb4中,第二像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上部,并且第一像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的另一侧,例如下部。因此,第一像素晶体管阵列可以设置在子像素块pb_s1和pb_s2之间,以与第二像素晶体管阵列相对。

[0074]

单位像素块pb3的第二像素晶体管阵列和单位像素块pb4的第二像素晶体管阵列

可以相对于单位像素块pb3和pb4之间的边界线彼此对称地布置。因此,尽管单位像素块pb3的第二像素晶体管阵列的组成元件与单位像素块pb4的第二像素晶体管阵列的组成元件尺寸相同,但单位像素块pb3的第二像素晶体管阵列的组成元件的布置顺序不同于单位像素块pb4的第二像素晶体管阵列的组成元件的布置顺序。单元像素块pb3和pb4的第二像素晶体管阵列的上述布置结构可以被认为是倒装形状布置结构。在此情况下,单位像素块pb3的第二像素晶体管阵列的源极跟随器晶体管dx32可定位成与单位像素块pb4的第二像素晶体管阵列的源极跟随器晶体管dx42相邻,使得源极跟随器晶体管dx32和dx42可以共享驱动电压节点vdx。

[0075]

单位像素块pb3的第一像素晶体管阵列和单位像素块pb4的第一像素晶体管阵列可以形成为倒装形状结构,并且相对于单位像素块pb3和pb4之间的边界线彼此对称地布置。单位像素块pb3的第一像素晶体管阵列的源极跟随器晶体管dx31可以定位成与单位像素块pb4的第一像素晶体管阵列的源极跟随器晶体管dx41相邻,使得源极跟随器晶体管dx31和dx41可以共享驱动电压节点vdx。

[0076]

图6是示出基于本公开的技术的一些实现方式而布置的各自包括8共享像素结构的四个单位像素块的示意图。

[0077]

参照图6,像素阵列100可以包括定位成在x轴方向上彼此相邻的两个单位像素块pb1和pb2。尽管为了便于描述,图6所示的单位像素块pb1和pb2在x轴方向上重复布置,但是其它实现方式也是可能的。在图6中,像素阵列100可以包括在x轴和y轴方向上重复布置的多个两单位像素块pb1和pb2。在图6中,两单位像素块pb1至pb2在下文中将被称为单位像素块组。

[0078]

单位像素块pb1至pb2中的每一个可以包括两个浮置扩散(fd)区fd1和fd2、两个源极跟随器晶体管dx11至dx22、两个选择晶体管sx11至sx22以及单个复位晶体管rx1和rx2。每个单位像素可以包括单个光电转换元件pd1至pd8和单个传输晶体管tx1至tx8。

[0079]

图6所示的单位像素块pb1和pb2中的每一个可以包括两个子像素块pb_s1和pb_s2,两个子像素块pb_s1和pb_s2中的每个允许单个浮置扩散(fd)区由四个单位像素共享。单位像素块pb1和pb2中的每一个可以包括分别设置在子像素块pb_s1两侧的第一像素晶体管阵列和第二像素晶体管阵列。

[0080]

在图6所示的单位像素块组中,第一像素晶体管阵列和第二像素晶体管阵列可以沿x方向交替布置。在一些实现方式中,在图6所示的单位像素块组中,第一像素晶体管阵列和第二像素晶体管阵列可以按照之字形方式布置。例如,单位像素块pb1的第一像素晶体管阵列位于单位像素块pb1的子像素块pb_s1的上部,单位像素块pb2的第一像素晶体管阵列位于单位像素块pb2的子像素块pb_s1的下部,定位成在右侧与单位像素块pb2相邻的单位像素块pb1的第一像素晶体管阵列位于单位像素块pb1的子像素块pb_s1的上部,并且单位像素块pb2的第一像素晶体管阵列位于单位像素块pb2的子像素块pb_s1的下部。类似地,单位像素块pb1的第二像素晶体管阵列位于单位像素块pb1的子像素块pb_s1的下部,单位像素块pb2的第二像素晶体管阵列位于单位像素块pb2的子像素块pb_s1的上部,定位成在右侧与单位像素块pb2相邻的单位像素块pb1的第二像素晶体管阵列位于单位像素块pb1的子像素块pb_s1的下部,并且单位像素块pb2的第二像素晶体管阵列位于单位像素块pb2的子像素块pb_s1的上部。例如,第一像素晶体管阵列和第二像素晶体管阵列中的每一个在单位

像素块pb1和pb2中的每一个中的位置可以关于单位像素块pb1和pb2的子像素块pb_s1的中心对角对称。

[0081]

例如,在单位像素块pb1中,第一像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上部,并且第二像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的另一侧,例如下部。因此,第二像素晶体管阵列可以设置在子像素块pb_s1和pb_s2之间,以与第一像素晶体管阵列相对。此外,在单位像素块pb2中,第二像素晶体管阵列可以设置在子像素块pb_s1的在y轴方向上的一侧,例如上部,并且第一像素晶体管阵列可以设置在定位成与第一像素晶体管阵列相对的另一侧。

[0082]

如上所述,第一像素晶体管阵列和第二像素晶体管阵列以之字形方式布置。因此,在单位像素块pb1和pb2之间的边界区域周围,单位像素块pb2的第一像素晶体管阵列的突出部分(单位像素块pb2的复位晶体管rx2位于该突出部分中)可以定位成插入到单位像素块pb1的第二像素晶体管阵列的凹入部分中。

[0083]

在第一像素晶体管阵列中,复位晶体管rx1和rx2可以联接在复位电压节点vrx与浮置扩散(fd)区fd1和fd2之间。例如,复位晶体管rx1和rx2中的每一个可以与选择晶体管sx11至sx22和源极跟随器晶体管dx11至dx22分开地形成在单个有源区中。在对应的有源区act1中,位于复位栅极一侧的源极区/漏极区可以联接到复位电压节点vrx,并且位于复位栅极另一侧的源极区/漏极区可以联接到对应的单位像素块pb1和pb2的浮置扩散(fd)区fd1和fd2。

[0084]

在第一像素晶体管阵列和第二像素晶体管阵列中,选择晶体管sx11至sx22可以在驱动电压节点vdx和输出节点out1到out4之间分别串联联接到源极跟随器晶体管dx11至dx22。例如,选择晶体管和源极跟随器晶体管可以形成为在被形成为沿x轴方向延伸的单个有源区中共享源极区/漏极区。选择晶体管sx11至sx22的定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到输出节点out1到out4。源极跟随器晶体管dx11至dx22的定位成与共享源极区/漏极区相对的源极区/漏极区可以联接到驱动电压节点vdx。

[0085]

在一些实现方式中,单位像素块pb1和pb2中的每一个可以包括两个驱动晶体管组,并且每一驱动晶体管组包括串联联接的一个源极跟随器晶体管和一个选择晶体管。两个驱动晶体管组可以彼此并联联接在驱动电压节点vdx和输出节点out1至out4之间

[0086]

在单位像素块pb1和pb2中的每一个的两个驱动晶体管组中,源极跟随器晶体管和选择晶体管可以彼此不同地布置。例如,在单位像素块pb1的第一像素晶体管阵列的驱动晶体管组中,选择晶体管sx11可以位于左侧,例如相比于靠近驱动电压节点vdx而言更靠近输出节点out1,并且源极跟随器晶体管dx11可以位于右侧,例如相比于靠近输出节点out1而言更靠近驱动电压节点vdx。在单位像素块pb1的第二像素晶体管阵列的驱动晶体管组中,选择晶体管sx12可以位于右侧,例如相比于靠近驱动电压节点vdx而言更靠近输出节点out1,并且源极跟随器晶体管可以位于左侧,例如相比于靠近输出节点out1更靠近驱动电压节点vdx。第一像素晶体管阵列和第二像素晶体管阵列中的选择晶体管和驱动晶体管的不同布置也可以应用于单位像素块pb2。

[0087]

以此方式,两个源极跟随器晶体管dx11和dx12可以沿对角线方向(即第一对角线方向)布置在单位像素块pb1中,并且两个源极跟随器晶体管dx21和dx22可以沿另一对角线方向(即第二对角线方向)布置在单位像素块pb2中。在一些实现方式中,第二对角线方向与

第一对角线方向交叉。另外,两个选择晶体管sx11和sx12可以沿第二对角线方向布置在单位像素块pb1中,并且两个选择晶体管sx21和sx22可以沿第一对角线方向布置在单位像素块pb2中。

[0088]

在一些实现方式中,在单位像素块pb1和pb2中的每一个中,两个源极跟随器晶体管可以形成为具有相同尺寸(例如,相同沟道宽度),并且两个选择晶体管也可以形成具有相同尺寸(例如,相同沟道宽度)。

[0089]

从以上描述显而易见,根据本公开的技术的实施方式的图像感测装置可以通过扩大布置在单位像素块中的源极跟随器晶体管和选择晶体管的沟道宽度来改进8共享像素结构中的源极跟随器增益。

[0090]

根据本公开的技术的实施方式的图像感测装置可以通过减小选择晶体管的电阻来增加一个或更多个像素信号的转移速率。

[0091]

尽管已经描述了多个说明性实施方式,但是应当理解,本领域技术人员可以设计出许多其它的修改和实施方式。特别地,在本公开、附图和所附权利要求的范围内的组成部分和/或布置中,可以进行许多变型和修改。除了组成部分和/或布置的变型和修改之外,替选的使用对于本领域技术人员也是显而易见的。

[0092]

相关申请的交叉引用

[0093]

本专利文件要求于2019年7月19日提交的韩国专利申请no.10-2019-0087323的优先权和权益,其全部内容通过引用并入本文。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1