一种异质集成的系统级封装结构及封装方法与流程

[0001]

本发明涉及半导体封装技术领域,特别与一种异质集成的系统级封装结构及封装方法相关。

背景技术:

[0002]

系统级封装sip,system in package技术是一种将不同功能的元器件,通过不同技术混合装载到同一封装之内,并由此提供系统级或子系统级功能的集成封装形式。sip作为在系统层面上延续摩尔定律的技术路线,是满足航天电子产品集成化、小型化的重要手段。

[0003]

航空航天电子、军事电子由于其应用环境的特殊性,需要往小型化、轻量化、高密度化、高可靠性等方面发展,于这类领域的sip产品,其技术先进性与工艺成熟性、产品可靠性都至关重要,互相影响、互相制约,要实现一款sip产品的批量化及规划化生产,既要考虑系统先进性又要兼顾工艺可实现性、成熟性等多方面的要求,确保产品符合应用原理需求与应用环境要求。

[0004]

目前,在系统级封装产品的管壳生产中,多采用单腔结构,但由于单腔结构的腔体尺寸过大,并不能达到小型化和轻量化的要求,且存在很大的可靠性风险;也有部分现有技术采用了双腔结构,来提高可靠性和集成度,但由于双腔结构的管壳的加工平整度很难控制,对工艺要求较高,不利于生产成本控制及批量化生产;同时,目前的双腔结构多应用于仅是多芯片集成封装的情况,少有包含无源分立器件的情况;另一方面,无论是目前的双腔结构,在结构方面的稳定性并不理想,在应用环境的需求越来越高的情况下,不能很好的满足需求。

技术实现要素:

[0005]

针对上述相关现有技术不足,本发明提供一种异质集成的系统级封装结构及封装方法,采用单面挖腔的陶瓷基体及柯伐环形成双面腔体结构,并提高了结构稳定性,缩短信号走线,提高互联效率和系统集成度,并实现了有源与无源器件集成,兼顾工艺成熟性与模块可靠性,为高可靠量产sip提供指导。

[0006]

为了实现本发明的目的,拟采用以下技术方案:一种异质集成的系统级封装结构,其特征在于,包括:陶瓷基体,其一面挖腔形成有第一腔体;柯伐环,设于陶瓷基体另一面,用于形成第二腔体;第一盖板,设于第一腔体开口处,用于封闭第一腔体;第二盖板,设于第二腔体开口处, 用于封闭第二腔体;第一腔体和第二腔体中分别至少设有一个芯片,芯片通过导电胶粘接于陶瓷基体表面;第一腔体或第二腔体中至少设有一个无源分立器件,无源分立器件通过导电胶粘接于

陶瓷基体表面。

[0007]

进一步,第一腔体具有与陶瓷基体一体成型的至少一个第一加强筋,用于将第一腔体分为至少两个腔室;第二腔体具有固定于第二腔体的至少一个第二加强筋,用于将第二腔体分为至少两个腔室;第一加强筋和第二加强筋垂直布置。

[0008]

第二加强筋为柯伐材质,焊接于第二腔体的陶瓷基体表面。

[0009]

芯片和无源分立器件容纳于腔室。

[0010]

进一步,第一腔体和第二腔体中设有无源分立器件的腔体,芯片和无源分立器件通过低温导电胶粘接于陶瓷基体表面的指定位置,该腔体通过平行缝焊工艺密封;第一腔体和第二腔体中不含无源分立器件的腔体,芯片通过高温导电胶粘接于陶瓷基体表面的指定位置,该腔体通过合金融封工艺密封;无源分立器件的两极之间具有绝缘胶,绝缘胶设于无源分立器件底部与陶瓷基体表面之间;芯片通过键合金线与陶瓷基体的线路连接。

[0011]

进一步,陶瓷基体是由多层陶瓷烧结压制而成,依次包括第一陶瓷体和第二陶瓷体,第一陶瓷体包括多层陶瓷,第二陶瓷体包括至少一层陶瓷,第二陶瓷体的单层陶瓷厚度均大于第一陶瓷体的各单层陶瓷厚度,第二陶瓷体的部分区域挖腔至第一陶瓷体与第二陶瓷体贴合的一面以形成第一腔体,第二陶瓷体的剩余区域为第一腔体的腔体侧壁。

[0012]

进一步,第一陶瓷体具有键合指、预设线路、外部焊盘,外部焊盘连接有外引脚,芯片的pad通过键合金线连接对应的键合指,键合指连接预设线路,预设线路连接外部焊盘,各层陶瓷之间的预设线路通过设于键合指的过孔导通。

[0013]

一种异质集成的系统级封装结构的封装方法,其特征在于,包括步骤:提供一陶瓷基体,对其一面挖腔,形成第一腔体;在陶瓷基体另一面设置柯伐环,形成第二腔体;在第一腔体中至少设置一个芯片,芯片通过高温导电胶粘接于陶瓷基体表面的指定位置;进行高温导电胶固化工序,然后使芯片通过键合金线与陶瓷基体的线路连接;装配第一盖板,并通过合金融封工艺密封第一腔体;在第二腔体中至少设置一个芯片和至少一个无源分立器件,芯片和无源分立器件通过低温导电胶粘接于陶瓷基体表面的指定位置;在无源分立器件的两极之间设有绝缘胶,绝缘胶设于无源分立器件底部与陶瓷基体表面之间;进行低温导电胶固化工序,然后使芯片通过键合金线与陶瓷基体的线路连接;装配第二盖板,并通过平行缝焊工艺密封第二腔体。

[0014]

进一步,形成第一腔体时,同时形成有至少一个与陶瓷基体一体成型的第一加强筋,用于将第一腔体分为至少两个腔室;形成第二腔体时,同时在第二腔体的陶瓷基体表面焊接有至少一个第二加强筋,用于将第二腔体分为至少两个腔室;第一加强筋和第二加强筋垂直布置。

[0015]

进一步,通过多层陶瓷烧结压制获得陶瓷基体,陶瓷基体依次包括第一陶瓷体和第二陶瓷体,第一陶瓷体预设有键合指、预设线路、外部焊盘,外部焊盘连接有外引脚,第一陶瓷体包括多层陶瓷,第二陶瓷体包括至少一层陶瓷,第二陶瓷体的单层陶瓷厚度均大于第一陶瓷体的各单层陶瓷厚度;对陶瓷基体一面的挖腔是在第二陶瓷体的部分区域挖腔至第一陶瓷体与第二陶瓷体贴合的一面以形成第一腔体,第二陶瓷体的剩余区域为第一腔体的腔体侧壁;芯片的pad通过键合金线连接对应的键合指,键合指连接预设线路,预设线路连接外部焊盘,各层陶瓷之间的预设线路通过设于键合指的过孔导通。本发明的有益效果:1、相比于传统单腔结构,通过单面挖腔的陶瓷基体配合焊接固定的柯伐环形成双腔结构,使得整个封装结构占用体积小,可靠性提高,并且集成能力提高,缩短了布线,并在一个封装结构中同时集成了有源和无源器件,在系统级层面延续摩尔定律,降低研制成本和周期;2、相比于现有的双腔结构,只需陶瓷基体一面挖腔,另一腔由柯伐环形成,解决了现有的双腔存在的加工平整度难以控制问题,减小平整度风险,同时陶瓷基体本身的强度也相比于双面挖腔结构有明显提高和保证,更加适合应用于批量化生产;同时,在双腔中均设置有加强筋,并且呈十字型布置,可以起到很好的力学加固作用,极大提高了系统级封装双腔的结构稳定性,可以很好的适配单面腔体较大需要容纳大尺寸芯片或较多有源及无源器件的情况,确保结构稳定性;3、同时将有源和无源器件集成于封装结构中,封装过程中依次从高温步骤向低温步骤进行,为上腔放置芯片和分立器件,采用低温导电胶粘接,采用平行缝焊工艺进行密封;下腔芯片采用高温导电胶粘接,采用密封性更优的合金融封工艺进行密封,解决了封装工艺问题,使得这种集成利于实施且对无源分立器件具有保护作用,同时能够实现更多功能的封装结构,以满足应用场景需求;4、陶瓷基体采用多层陶瓷烧结压制而成,便于形成多层线路结构,在缩小体积的同时,以满足系统级封装中有源和无源器件的走线需求,压制成型后从第二陶瓷体至少一层进行挖腔,便于形成第一腔体及其腔体壁,以配合第一盖板形成密封的上腔,结构稳定,平整度可控性好。

附图说明

[0016]

本文描述的附图只是为了说明所选实施例,而不是所有可能的实施方案,更不是意图限制本发明的范围。

[0017]

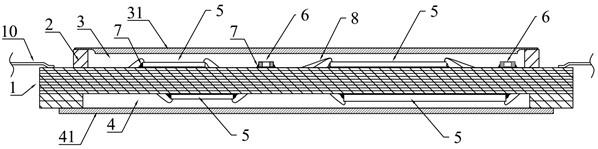

图1为本发明实施例的整体示意图一。

[0018]

图2为本发明实施例的整体示意图二。

[0019]

图3为本发明实施例的无源分立器件封装结构示意图。

[0020]

图4为本发明实施例的陶瓷基体结构示意图。

[0021]

图5为本发明实施例的第一加强筋结构示意图一。

[0022]

图6为本发明实施例的第二加强筋结构示意图一。

[0023]

图7为本发明实施例的第一加强筋结构示意图二。

[0024]

图8为本发明实施例的第二加强筋结构示意图二。

[0025]

图9为本发明实施例的电气连接示意图。

[0026]

图10为本发明实施例的封装方法流程图。

具体实施方式

[0027]

为使本发明实施例的目的、技术方案和优点更加清楚,下面结合附图对本发明的实施方式进行详细说明,但本发明所描述的实施例是本发明一部分实施例,而不是全部的实施例。

[0028]

实施例1本实例提供的一种异质集成的系统级封装结构,包括两个腔体。

[0029]

具体的,如图1所示,第一腔体4是在陶瓷基体1一面挖腔形成;第二腔体3是在陶瓷基体1另一面焊接柯伐环2形成。

[0030]

第一腔体4开口处,装配用于封闭第一腔体4的第一盖板41。

[0031]

第二腔体3开口处,装配用于封闭第二腔体3的第二盖板31。

[0032]

第一腔体4和第二腔体3中分别至少设有一个芯片5,芯片5通过导电胶7粘接于陶瓷基体1表面。

[0033]

第一腔体4或第二腔体3中至少设有一个无源分立器件6,无源分立器件6通过导电胶7粘接于陶瓷基体1表面。

[0034]

出于可制造性及规模化生产的考虑,经过管壳生产和封装的可行性评估,由于单腔结构的腔体尺寸过大,存在很大的可靠性风险,而目前的双腔结构的管壳的加工平整度很难控制,若是陶瓷双面挖腔,则两个腔体的平整度都要严格控制,会对生产工艺和良率提出更高挑战。同时,陶瓷本体双面挖腔会降低陶瓷本体强度,这对sip器件可靠性是不利的。

[0035]

通过本实例的封装结构,对于陶瓷本体,只需一面挖腔,减小平整度风险,同时陶瓷本体强度相比于双面挖腔也有所保证,另一面的腔体通过可伐环来形成,可以在保证平整度的同时,降低工艺难度,并且提高整体封装结构的稳定性。

[0036]

在本实例中,该封装结构的上下两个腔体均有加强筋,且上下腔的加强筋呈十字型,具体如图5~8所示:第一腔体4具有与陶瓷基体1一体成型的第一加强筋42,用于将第一腔体4分为两个腔室;第二腔体3具有固定于第二腔体3的一个第二加强筋32,用于将第二腔体3分为两个腔室;第一加强筋42和第二加强筋32垂直布置。

[0037]

第一加强筋42与陶瓷基体1一体成型,在挖腔时形成。

[0038]

第二加强筋32为柯伐材质,焊接于第二腔体3的陶瓷基体1表面。

[0039]

芯片5和无源分立器件6分别对应容纳于指定腔室。

[0040]

考虑封装的可靠性,将所有的芯片平铺。受芯片密度的影响,管壳的结构为上下双腔结构,由于芯片尺寸比较大,上下单腔腔体尺寸比较大,所以考虑通过加强筋将上下腔体各自分成双腔或多腔,在本实例中为双腔,且上下腔体的加强筋呈十字结构,可以更好的起到力学加固作用,可有效增强管壳的整体强度。

[0041]

作为本实例的具体实施方式,如图2所示,第二腔体3设有2个无源分立器件6和2个芯片51、52。通过引入无源分立器件6,可以极

大提高系统级封装产品的功能特性,满足更多的应用场景需求。具体的,在第二腔体3中芯片51、52和2个无源分立器件6通过低温导电胶71粘接于陶瓷基体1表面的指定位置,如图3所示,无源分立器件6为电容时,两极之间具有绝缘胶9,绝缘胶9设于无源分立器件6底部与陶瓷基体1表面之间。后期通过低温固化,可以有效确保无源分立器件6在封装过程中的稳定性,以及避免了高温的影响。第二腔体3通过平行缝焊工艺密封。芯片5通过键合金线8与陶瓷基体1的线路连接。

[0042]

第一腔体4中设有2个芯片53、54,2个芯片53、54通过高温导电胶72粘接于陶瓷基体1表面的指定位置,后期通过高温固化,芯片5通过键合金线8与陶瓷基体1的线路连接,该腔体通过合金融封工艺密封。

[0043]

根据一个腔体为高温封装一个腔体为低温封装的结构特性,可以在第二腔体3中选择适应低温固化的芯片,提高了封装结构的实用性,为适配芯片提供了更多选择范围。

[0044]

作为本实例的具体实施方式,陶瓷基体1是由多层陶瓷烧结压制而成,依次包括第一陶瓷体11和第二陶瓷体12,第一陶瓷体11包括多层陶瓷,第二陶瓷体12包括至少一层陶瓷,第二陶瓷体12的单层陶瓷厚度均大于第一陶瓷体11的各单层陶瓷厚度,第二陶瓷体12的部分区域挖腔至第一陶瓷体11与第二陶瓷体12贴合的一面以形成第一腔体4,第二陶瓷体12的剩余区域为第一腔体4的腔体侧壁。

[0045]

具体的,如图4所示,本实例的第一陶瓷体11包括9层厚度为0.2mm的陶瓷层,第二陶瓷体12包括2层厚度为0.5mm的陶瓷层。下腔体深度为1mm,是通过去除10-11层部分陶瓷体形成的,1-9层陶瓷保持完整。

[0046]

需要说明的是,管壳/基体生产中,是各层陶瓷压制成一体再挖腔,便于对各层陶瓷粘合稳定性的控制,同时利于挖腔过程中对腔体表面平整度的控制,以利于芯片粘合,提高粘合强度。

[0047]

高可靠陶瓷外壳/基体是实现机械连接与电气互联的封装基体,芯片5和分立器件6均通过导电胶7粘接在腔体表面,腔体表层有键合指14,内部有预设线路/金属走线15。芯片间的电气互联通过“第一芯片pad-第一键合线-第一键合指-外壳内部布线-第二键合指-第二键合线-第二芯片pad”实现。

[0048]

具体的,如图9所示的电气连接方式,第一陶瓷体11具有键合指14、预设线路15、外部焊盘16,外部焊盘16连接有外引脚10,芯片5的pad通过键合金线8连接对应的键合指14,键合指14连接预设线路15,预设线路15连接外部焊盘16,各层陶瓷之间的预设线路15通过设于键合指14的过孔141导通。

[0049]

如图9所示,内部芯片间信号连接以及对外信号连接通过以下情况实现:芯片51的第一pad 511、第二pad 512,分别通过一键合金线8连接一键合指14;芯片52的第一pad 521、第二pad 522、第三pad 523、第四pad 524,分别通过一键合金线8连接一键合指14。

[0050]

芯片51的第一pad 511对应的键合指14与芯片52的第一pad 521对应的键合指14通过预设线路/金属走线15连接,并与一外部焊盘16连接,该外部焊盘16连接一外引脚10。

[0051]

芯片51的第二pad 512对应的键合指14与芯片52的第二pad 522对应的键合指14通过预设线路/金属走线15连接。

[0052]

芯片52的第三pad 523对应的键合指14通过预设线路/金属走线15连接一一外部

焊盘16连接,该外部焊盘16连接一外引脚10。

[0053]

芯片52的第四pad 524对应的键合指14具有过孔141,过孔141连接到下一层走线。

[0054]

需要说明的是,图中仅一种芯片布局的连接关系示意,是为清楚描述,但不限定芯片布局及电气连接关系仅为此。

[0055]

实施例2本实例提供一种异质集成的系统级封装结构的封装方法,至少包括以下步骤,步骤流程如图10所示:步骤1)外壳处理提供一陶瓷基体1,对其一面挖腔,形成第一腔体4;在陶瓷基体1另一面设置柯伐环2,形成第二腔体3,如图1~2所示;其中,如图5~8所示,形成第一腔体4时,同时形成有一个与陶瓷基体1一体成型的第一加强筋42,用于将第一腔体4分为两个腔室;形成第二腔体3时,同时在第二腔体3的陶瓷基体1表面焊接有一个第二加强筋32,用于将第二腔体3分为两个腔室;第一加强筋42和第二加强筋32垂直布置。

[0056]

其中,如图4所示,通过多层陶瓷烧结压制获得陶瓷基体1,陶瓷基体1依次包括第一陶瓷体11和第二陶瓷体12,第一陶瓷体11预设有键合指14、预设线路15、外部焊盘16,键合指14连接预设线路15,预设线路15连接外部焊盘16,各层陶瓷之间的预设线路15通过设于键合指14的过孔141导通,外部焊盘16连接有外引脚10,第一陶瓷体11包括多层陶瓷,第二陶瓷体12包括至少一层陶瓷,第二陶瓷体12的单层陶瓷厚度均大于第一陶瓷体11的各单层陶瓷厚度;对陶瓷基体1一面的挖腔是在第二陶瓷体12的部分区域挖腔至第一陶瓷体11与第二陶瓷体12贴合的一面以形成第一腔体4,第二陶瓷体12的剩余区域为第一腔体4的腔体侧壁。

[0057]

2)下腔装片在第一腔体4中至少设置一个芯片5,如图1~2所示为设置了2个芯片5于下腔,芯片5通过高温导电胶72粘接于陶瓷基体1表面的指定位置。

[0058]

3)高温导电胶固化。

[0059]

4)然后使第一腔体4中的芯片5通过键合金线8与陶瓷基体1的线路连接,具体是芯片5的pad通过键合金线8连接对应的键合指14。

[0060]

5)装配第一盖板41,并通过合金融封工艺密封第一腔体4。

[0061]

6)上腔装片和分立元器件安装在第二腔体3中至少设置一个芯片5和至少一个无源分立器件6,如图2所示,设置2个芯片5和2个无源分立器件6,并通过低温导电胶71粘接于陶瓷基体1表面的指定位置;在无源分立器件6的两极之间设有绝缘胶9,如fp4526,绝缘胶9设于无源分立器件6底部与陶瓷基体1表面之间;7)进行低温导电胶固化工序8)然后使第二腔体3的芯片5通过键合金线8与陶瓷基体1的线路连接,具体是芯片5的pad通过键合金线8连接对应的键合指14。

[0062]

9)装配第二盖板31,并通过平行缝焊工艺密封第二腔体3。

[0063]

10)打标出货。

[0064]

需要说明的是,由于分立器件不能耐高温,因此上腔采用低温导电胶粘接,采用平行缝焊工艺进行密封。下腔芯片采用高温导电胶粘接,采用密封性更优的合金融封工艺进行密封。该封装过程是由温度梯度决定的,下腔粘片后固化温度峰值温度最低(min.)310℃,最高(max.)350,℃;下腔封帽,峰值温度最低(min.)280℃, 最高(max.)330℃;上腔粘片峰值温度最低(min.)150℃,最高(max.)180℃,下腔封帽,只会在焊接处产生局部高温,腔体内部不会出现明显温升;封装过程中依次从高温步骤向低温步骤进行。

[0065]

上述实施例提供的异质集成的系统级封装结构及封装方法,实现以单面挖腔陶瓷为封装基体配合柯伐环形成双腔结构,并增设加强筋,键合线、导电胶等为互联材料,合金盖板为密封材料实现有源与无源器件的异质集成,在提高集成度、实现小型化的同时,以高可靠应用、批量生产为目的,综合考虑工艺成熟性与产品可靠性。

[0066]

以上仅为本发明的优选实施例,并不用于限制本发明,显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1