GaN基双沟道HEMT器件

gan基双沟道hemt器件

技术领域

1.本发明涉及一种hemt器件,具体涉及一种gan基双沟道hemt器件。

背景技术:

2.基于gan/algan异质结的高电子迁移率晶体管(hemt)有望替代传统硅基器件,实现高频高功率工作条件下的低能量损耗电力转换和信号传输,从而在高铁及新能源汽车功率控制单元、智能电网芯片,以及5g用微波射频前端等领域中获得广泛应用。

3.常见的hemt器件主要有耗尽型(常开)和增强型(常关)两种类型。其中,耗尽型器件在0v外加偏压状态时处于导通状态,而增强型器件则是0v外加偏压时处于关闭状态。以金属极性的耗尽型hemt器件为例,其结构如图1所示,包括势垒层11、沟道层12、缓冲层13、衬底14、源电极16、漏电极17、栅电极18。一般势垒层禁带宽度较大,例如由algan构成,沟道层是信号传输的通道,禁带宽度较低,例如由gan构成。缓冲层通常由高阻gan等构成,以降低器件漏电流。电子积累在gan沟道层和algan势垒层界面的三角形势阱中,形成二维电子气(2deg)。而氮极性gan/algan增强型hemt器件的结构可以参阅图2所示,其通常包括沟道层21、势垒层22、缓冲层23、衬底24、源电极27、漏电极28、栅电极29等,栅电极29与沟道层21之间设置有栅介质层26。但是,无论是现有的耗尽型gan hemt器件,还是增强型gan hemt器件,其器件结构中的2deg只存在于单一界面,导致面密度不高,器件输出电流和功率不足。

4.尽管有一些研究人员提出了在gan基hemt器件中采用“双异质结”的方案,但是这些双异质结的基本思路是在gan沟道层和缓冲层之间插入一层禁带宽度更大的algan形成背势垒,以降低漏电流,其2deg依然只存在于顶部势垒层和沟道层界面处,面密度进一步提升存在瓶颈。

技术实现要素:

5.本发明的主要目的在于提供一种gan基双沟道hemt器件,从而克服现有技术的不足。

6.为实现前述发明目的,本发明采用的技术方案包括:

7.本发明的一些实施例提供了一种gan基双沟道hemt器件,其包括:

8.外延结构,包括沿设定方向依次设置的第一半导体层、第二半导体层和第三半导体层,所述第一半导体层、第二半导体层和第三半导体层的禁带宽度依次增大,所述第一半导体层、第三半导体层中的任一者与第二半导体层的界面处均形成有二维电子气,并且组成所述第二半导体层、第三半导体层的半导体材料具有相同晶格常数;以及

9.与所述外延结构配合的源极、漏极及栅极。

10.在一些实施方式中,所述源极、漏极、栅极均与所述第三半导体层电性接触。

11.在一些实施方式中,所述栅极与第一半导体层之间还设置有栅介质层。

12.在一些实施方式中,所述栅极与第三半导体层之间还设置有第五半导体层。

13.与现有技术相比较,本发明实施例所提供的gan基双沟道hemt器件因具有双沟道

层和双势垒层结构,提高了二维电子气的面密度,从而大幅提高了hemt器件的输出电流和输出功率密度,进一步的,通过使双势垒层的组成材料具有相同的晶格常数,还有效降低了外延结构内部的位错密度和应力,从而提高了hemt器件工作的稳定性和可靠性。

附图说明

14.图1是现有的一种金属极性algan/gan耗尽型hemt器件的结构示意图;

15.图2是现有的一种氮极性gan/algan增强型hemt器件的结构示意图;

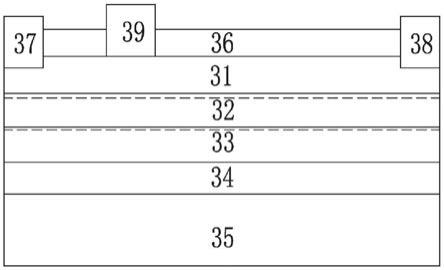

16.图3是本发明一典型实施方式中一种金属极性双沟道耗尽型gan hemt器件的结构示意图;

17.图4是本发明另一典型实施方式中一种氮极性双沟道增强型gan hemt器件的结构示意图;

18.图5是图3所示的一种金属极性双沟道耗尽型gan hemt器件的alinn/algan/gan双异质结能带图;

19.图6是本发明实施例1中一种双沟道hemt器件各结构层的禁带宽度图;

20.图7是本发明实施例1中一种双沟道hemt器件的转移特性曲线图;

21.附图标记说明:11-algan势垒层、12-gan沟道层、13-gan缓冲层、14-衬底、15-钝化层、16-源极、17-漏极、18-栅极、21-gan沟道层、22-algan势垒层、23-gan缓冲层、24-衬底、25-钝化层、26-栅介质层、27-源极、28-漏极、29-栅极、31-alinn势垒层、32-algan势垒层、33-gan沟道层、34-gan缓冲层、35-衬底、36-钝化层、37-源极、38-漏极、39-栅极、41-gan沟道层、42-algan势垒层、43-alinn势垒层、44-gan缓冲层、45-衬底、46-钝化层、47-栅介质层、48-源极、49-漏极、410-栅极。

具体实施方式

22.如前所述,鉴于现有gan hemt器件中2deg只存在于单一界面,导致面密度不高,器件输出电流和功率不足等缺陷,本案发明人经长期研究和实践,得以提出本发明的技术方案,如下将予以解释说明。

23.本发明的一些实施例提供的一种gan基双沟道hemt器件包括:

24.外延结构,包括沿设定方向设置的第一半导体层、第二半导体层和第三半导体层,所述第一半导体层、第二半导体层和第三半导体层的禁带宽度依次增大,所述第一半导体层、第三半导体层中的任一者与第二半导体层的界面处均形成有二维电子气,并且组成所述第二半导体层、第三半导体层的半导体材料具有相同晶格常数;以及

25.与所述外延结构配合的源极、漏极及栅极。

26.其中,所述第一半导体层、第二半导体层、第三半导体层的材质可以分别采用gan、algan、alinn,但不局限于此,而还可以采用其它的iii-v族半导体材料。

27.其中,若第二半导体层、第三半导体层分别采用algan、alinn,则可以通过调制alinn中in组分含量等方式,使alinn与algan具有相同的晶格常数,从而降低外延结构内部的位错密度和应力。

28.在一些实施方式中,所述第一半导体层的厚度为1-200nm。

29.在一些实施方式中,所述第二半导体层的厚度为1-20nm。

200nm。gan缓冲层34厚度为100nm-10微米。在该器件中,alinn势垒层31可以视为第一势垒层,algan势垒层32既作为第二势垒层又作为第一沟道层,gan沟道层33可以视为第二沟道层,由此在器件中形成双沟道层、双势垒层结构。

45.该金属极性双沟道耗尽型gan hemt器件中的外延结构可以通过金属有机气相外延(mocvd)、分子束外延(mbe)等方式形成。钝化层为sio2、si3n4、al2o3中的一种或几种的组合,厚度为1-500nm,其可以通过磁控溅射、等离子体增强化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)、mocvd、电子束蒸镀等方式中的一种或几种的组合沉积形成。源极37、漏极38以及栅极39可以采用金属电极,其材质可以为ti、v、al、ni、au、pd、cr中的一种或几种的组合,厚度为10-500nm,制备方式可以包括电子束蒸镀、热蒸镀、磁控溅射中的一种或几种的组合,且不限于此。金属电极制备后可以经过热处理,温度为300-800℃,时间为1-10min,气氛为n2、ar或真空。衬底可以为蓝宝石、硅、碳化硅中的一种,但不限于此。

46.进一步的,对于图3所示器件来说,还可以在alinn势垒层31增加一层gan盖帽层(图中未示出),其厚度可以为1-5nm,用以降低前述金属电极与外延结构之间的接触电阻。

47.进一步的,对于图3所示器件来说,还可以在alinn势垒层31与algan势垒层32之间和/或algan势垒层32与gan沟道层33之间增加一层aln插入层,用以降低alinn、algan等三元合金对2deg的散射作用。该aln插入层的厚度可以为1-5nm。

48.进一步的,对于图3所示器件来说,亦可以在栅极410下方设置一p-gan反型层,该p-gan反型层可以生长于alinn势垒层31表面,以实现增强型器件。该p-gan反型层的厚度可以为5-50nm。

49.请参阅图4示出了本发明另一典型实施方式中的一种氮极性双沟道增强型gan hemt器件,其包括gan沟道层41、algan势垒层42、alinn势垒层43、gan缓冲层44、衬底45、钝化层46、栅介质层47、源极48、漏极49以及栅极410,虚线为2deg。alinn势垒层43中铝组分为0%-100%,且禁带宽度最大,厚度为1-100nm。algan势垒层42中铝的组分为0%-100%,且禁带宽度小于alinn,但大于gan,厚度为1-20nm。并且alinn和algan晶格常数匹配。gan沟道层41厚度为1-200nm。gan缓冲层44厚度为100nm-10微米。在该器件中,alinn势垒层43可以视为第一势垒层,algan势垒层42既作为第二势垒层又作为第一沟道层,gan沟道层41可以视为第二沟道层,由此在器件中形成双沟道层、双势垒层结构。

50.该氮极性双沟道增强型gan hemt器件中的外延结构也可以通过金属有机气相外延(mocvd)、分子束外延(mbe)等方式形成。钝化层也可以为sio2、si3n4、al2o3中的一种或几种的组合,厚度为1-500nm,其可以通过磁控溅射、pecvd、lpcvd、mocvd、电子束蒸镀等方式中的一种或几种的组合沉积形成。栅极介电材料可以为aln、si3n4、al2o3中的一种或几种的组合,厚度为1-100nm,生长方式可以为磁控溅射、pecvd、lpcvd、mocvd、电子束蒸镀中的一种或多种。源极、漏极以及栅极可以采用金属电极,其材质可以为ti、v、al、ni、au、pd、cr中的一种或几种的组合,厚度为10-500nm,制备方式可以包括电子束蒸镀、热蒸镀、磁控溅射中的一种或几种的组合,且不限于此。金属电极制备后可以经过热处理,温度为300-800℃,时间为1-10min,气氛为n2、ar或真空。衬底可以为蓝宝石、硅、碳化硅中的一种,但不限于此。

51.为了更加清楚地说明本发明以上实施例所提供的双沟道hemt器件的工作原理,可以采用能带工程,通过自洽求解一维薛定谔/泊松方程,对不同alinn、algan组分和厚度的

能带结构和费米能分布进行理论仿真。以图3所示金属极性耗尽型hemt器件为例,其能带图可以参阅图5。在alinn/algan界面和algan/gan界面,均存在2deg的累积。即algan和gan构成双沟道结构。

52.如下将结合实施例对本发明的技术方案进行更为详细的说明。需要指出的是,若非特别说明,则如下实施例中采用的各类原料及设备等均可以通过市场购买等途径获取,而其中外延生长、刻蚀等操作均可以依据本领域已知的方式实施。

53.实施例1:该实施例提供了一种在2英寸蓝宝石衬底上外延制备的金属极性双沟道耗尽型hemt器件,其结构可以参阅图3。在制备该hemt器件时,在2英寸蓝宝石衬底上依次外延生长厚2μm的gan缓冲层、厚50nm的gan沟道层、厚10nm的al

0.2

ga

0.8

n层、厚15nm的al

0.85

in

0.15

n层,之后在顶部沉积厚200nm的si3n4钝化层。栅源距离lgs=2μm,栅漏距离lgd=3μm。栅极长为3μm,宽为100μm。源、漏极可以由从下向上依次沉积的厚30nm的ti、厚120nm的al、厚30nm的n、厚100nm的au形成。栅极可以由从下向上依次沉积的厚30nm的ni、厚100nm的au形成。al

0.2

ga

0.8

n与al

0.85

in

0.15

n的晶格常数相同,各层禁带宽度如图6所示。

54.对比例1该对比例还提供了一种具有图1所示结构的金属极性耗尽型hemt器件,其可以包括在2英寸蓝宝石衬底上依次外延生长形成的厚2μm的gan缓冲层、厚50nm的gan沟道层、厚30nm的al

0.2

ga

0.8

n层,al

0.2

ga

0.8

n上沉积有厚200nm的si3n4钝化层。栅源距离lgs=2μm,栅漏距离lgd=3μm。栅极长为3μm,宽为100μm。源、漏极也可以由从下向上依次沉积的厚30nm的ti、厚120nm的al、厚30nm的n、厚100nm的au形成。栅极亦可以由从下向上依次沉积的厚30nm的ni、厚100nm的au形成。

55.该实施例1的金属极性双沟道耗尽型hemt器件(本专利双沟道hemt)与该对比例1的金属极性耗尽型hemt器件(传统hemt)的转移特性曲线如图7所示,显然,该实施例1的双沟道hemt器件具有更大的输出电流。

56.本发明以上实施例通过采用alinn、algan沉积在gan之上,构成双势垒层和双沟道层,能够大幅度提高2deg的面密度和hemt的输出电流、输出功率,从而克服现有单沟道gan hemt器件导通电流低、器件输出功率低的问题。

57.本发明以上实施例所提供的氮极性增强型器件中,存在alinn和algan两层背势垒,可以有效降低器件的缓冲层漏电,提高击穿电压和栅调控能力,抑制器件的短沟道效应。

58.本发明以上实施例通过调节alinn和algan中的组分,可以实现两者的晶格常数相匹配,因此有助于降低外延结构的内部应力,减少外延结构内的位错和缺陷,提高器件工作的稳定性和可靠性

59.本发明以上实施例可以通过调节alinn和algan势垒层厚度,进行能带工程调控,提高了对二维电子气的束缚力,从而降低电流坍塌效应。

60.本发明的各方面、实施例、特征及实例应视为在所有方面为说明性的且不打算限制本发明,本发明的范围仅由权利要求书界定。在不背离所主张的本发明的精神及范围的情况下,所属领域的技术人员将明了其它实施例、修改及使用。

61.在本发明案中标题及章节的使用不意味着限制本发明;每一章节可应用于本发明的任何方面、实施例或特征。尽管已参考说明性实施例描述了本发明,但所属领域的技术人员将理解,在不背离本发明的精神及范围的情况下可做出各种其它改变、省略及/或添加且

可用实质等效物替代所述实施例的元件。

62.另外,可在不背离本发明的范围的情况下作出许多修改以使特定情形或材料适应本发明的教示。因此,本文并不打算将本发明限制于用于执行本发明的所揭示特定实施例,而是打算使本发明将包含归属于所附权利要求书的范围内的所有实施例。此外,除非具体陈述,否则术语第一、第二等的任何使用不表示任何次序或重要性,而是使用术语第一、第二等来区分一个元素与另一元素。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1