存储器结构及其操作方法与流程

1.本发明涉及一种半导体结构及其操作方法,尤其涉及一种存储器结构及其操作方法。

背景技术:

2.由于非易失性存储器(non-volatile memory)具有存入的数据在断电后也不会消失的优点,因此许多电器产品中必须具备此类存储器,以维持电器产品开机时的正常操作。然而,在利用栅极(如,浮置栅极(floating gate))存储电荷的存储器中,由于位于栅极与基底之间的栅介电层通常较薄,因此存储在栅极中的电荷容易流失,进而降低存储器元件的数据保存能力(data retention capacity)。

技术实现要素:

3.本发明提供一种存储器结构及其操作方法,其可具有较佳的数据保存能力。

4.本发明提出一种存储器结构,包括基底、栅极结构、电荷存储层与第一控制栅极。基底具有鳍部。部分栅极结构设置在鳍部上。栅极结构与鳍部彼此电性绝缘。电荷存储层耦合于栅极结构。电荷存储层与栅极结构彼此电性绝缘。第一控制栅极耦合于电荷存储层。第一控制栅极与电荷存储层彼此电性绝缘。

5.依照本发明的一实施例所述,在上述存储器结构中,电荷存储层未电连接至电压源。

6.依照本发明的一实施例所述,在上述存储器结构中,电荷存储层与栅极结构之间的介电材料的厚度可大于栅极结构与鳍部之间的介电材料的厚度。

7.依照本发明的一实施例所述,在上述存储器结构中,栅极结构可包括第一栅极与第二栅极。第一栅极设置在鳍部上。第一栅极与鳍部可彼此电性绝缘。第一栅极与第二栅极可彼此分离且彼此电连接。电荷存储层耦合于第二栅极。电荷存储层与第二栅极可彼此电性绝缘。

8.依照本发明的一实施例所述,在上述存储器结构中,还可包括隔离结构。隔离结构设置在基底上,且位于鳍部周围。第二栅极、电荷存储层与第一控制栅极可设置在隔离结构上。

9.依照本发明的一实施例所述,在上述存储器结构中,电荷存储层可位于第二栅极的一侧。

10.依照本发明的一实施例所述,在上述存储器结构中,电荷存储层还可位于第二栅极的顶面上。

11.依照本发明的一实施例所述,在上述存储器结构中,第一控制栅极与电荷存储层之间的总耦合面积(coupling area)可小于第二栅极与电荷存储层之间的总耦合面积。

12.依照本发明的一实施例所述,在上述存储器结构中,可包括多个第二栅极与多个电荷存储层。多个第二栅极可彼此电连接。多个电荷存储层可彼此电连接。多个电荷存储层

耦合于多个第二栅极。

13.依照本发明的一实施例所述,在上述存储器结构中,栅极结构可包括栅极。栅极设置在鳍部上。栅极与鳍部可彼此电性绝缘。电荷存储层可耦合于栅极。电荷存储层与栅极可彼此电性绝缘。

14.依照本发明的一实施例所述,在上述存储器结构中,电荷存储层可位于栅极的顶面上。

15.依照本发明的一实施例所述,在上述存储器结构中,还可包括第二控制栅极。第二控制栅极耦合于电荷存储层。第二控制栅极与电荷存储层可彼此电性绝缘。第一控制栅极与电荷存储层之间的总耦合面积可小于第二控制栅极与电荷存储层之间的总耦合面积。

16.依照本发明的一实施例所述,在上述存储器结构中,基底可具有多个鳍部。第一栅极可跨设在多个鳍部上。

17.依照本发明的一实施例所述,在上述存储器结构中,还可包括接触窗(contact)。接触窗电连接至鳍部中的掺杂区。接触窗与电荷存储层可源自于同一个材料层。

18.依照本发明的一实施例所述,在上述存储器结构中,还可包括选择栅极。选择栅极设置在第一栅极的一侧的鳍部上。选择栅极与鳍部可彼此电性绝缘。

19.依照本发明的一实施例所述,在上述存储器结构中,还可包括第二控制栅极。第二控制栅极耦合于电荷存储层。第二控制栅极与电荷存储层可彼此电性绝缘。

20.依照本发明的一实施例所述,在上述存储器结构中,还可包括耦合栅极。耦合栅极耦合于电荷存储层。耦合栅极与电荷存储层可彼此电性绝缘。

21.依照本发明的一实施例所述,在上述存储器结构中,第一控制栅极与电荷存储层之间的总耦合面积可小于耦合栅极与电荷存储层之间的总耦合面积。

22.本发明提出一种存储器结构的操作方法,包括对上述存储器结构进行编程操作。编程操作可包括以下步骤。使电荷自第一控制栅极注入(inject)电荷存储层。

23.本发明提出一种存储器结构的操作方法,包括对上述存储器结构进行擦除操作。擦除操作可包括以下步骤。使电荷从电荷存储层中经由第一控制栅极排出(eject)。

24.基于上述,在本发明所提出的存储器结构及其操作方法中,由于电荷可存储在耦合于栅极结构的电荷存储层中,因此可防止存储在电荷存储层中的电荷流失,进而提升存储器元件的数据保存能力。

25.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

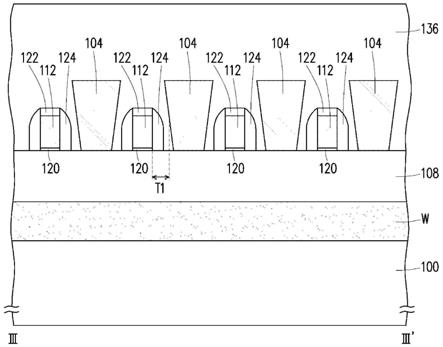

附图说明

26.图1a为根据本发明一实施例的存储器结构的上视图;

27.图1b为沿着图1a中的i-i’剖面线的剖视图;

28.图1c为沿着图1a中的ii-ii’剖面线的剖视图;

29.图1d为沿着图1a中的iii-iii’剖面线的剖视图;

30.图1e为沿着图1a中的iv-iv’剖面线的剖视图;

31.图2为根据本发明一实施例的存储单元阵列的示意图;

32.图3a为根据本发明另一实施例的存储器结构的上视图;

33.图3b为沿着图3a中的v-v’剖面线的剖视图;

34.图3c为沿着图3a中的vi-vi’剖面线的剖视图;

35.图4a为根据本发明另一实施例的存储器结构的上视图;

36.图4b为沿着图4a中的vii-vii’剖面线的剖视图。

37.附图标号说明:

38.10,20,30:存储器结构

39.100:基底

40.102:栅极结构

41.104:电荷存储层

42.106,186:控制栅极

43.108:隔离结构

44.110,112:栅极

45.114,120,136,140,180,188,196:介电层

46.116,122,142,182,190,198:顶盖层

47.118,124,144,184,192,200:间隙壁

48.126,134,168,172,176,202,206,210,178:接触窗

49.128,132,166,170,174,204,208,212:接触通孔

50.130:导线

51.138:选择栅极

52.146,148,150:掺杂区

53.152,154,156,158:轻掺杂漏极

54.160:晶体管

55.162:选择晶体管

56.194:耦合栅极

57.f:鳍部

58.m,m1~m4:存储单元

59.ma:存储单元阵列

60.w:阱区

61.t1~t6:厚度

具体实施方式

62.图1a为根据本发明一实施例的存储器结构的上视图。在图1a中,省略图1b至图1e中的部分构件,以清楚地描述图1a中的构件之间的配置关系。图1b为沿着图1a中的i-i’剖面线的剖视图。图1c为沿着图1a中的ii-ii’剖面线的剖视图。图1d为沿着图1a中的iii-iii’剖面线的剖视图。图1e为沿着图1a中的iv-iv’剖面线的剖视图。图2为根据本发明一实施例的存储单元阵列的示意图。

63.请参照图1a至图1e,存储器结构10包括基底100、栅极结构102、电荷存储层104与控制栅极106。在一些实施例中,存储器结构10可为非易失性存储器。基底100具有鳍部f。存储器结构10可与鳍式场效晶体管(finfet)的工艺进行整合。鳍部f可作为存储器元件的有

源区。在本实施例中,基底100是以具有多个鳍部f为例,但本发明并不以此为限。只要鳍部f的数量为一个以上,即属于本发明所涵盖的范围。此外,存储器结构10还可包括隔离结构108。隔离结构108设置在基底100上,且位于鳍部f周围。如图1c所示,鳍部f的顶面可高于隔离结构108的顶面。在一些实施例中,隔离结构108可为浅沟槽隔离结构(shallow trench isolation,sti)。隔离结构108的材料例如是氧化硅。

64.请参照图1a至图1c,部分栅极结构102设置在鳍部f上。栅极结构102与鳍部f彼此电性绝缘。栅极结构102未电连接至电压源。在本实施例中,栅极结构102可包括栅极110与栅极112。部分栅极110设置在鳍部f上。栅极110与鳍部f可彼此电性绝缘。在一些实施例中,栅极110可跨设在多个鳍部f上。此外,部分栅极110可设置在隔离结构108上。栅极110可为金属栅极。栅极110的材料可包括钨或氮化钛(tin)等导体材料。

65.另外,如图1b与图1c所示,存储器结构10还可包括介电层114、顶盖层116与间隙壁118中的至少一者。介电层114设置在栅极110与鳍部f之间,因此栅极110与鳍部f可彼此电性绝缘。介电层114的材料例如是氧化硅或高介电常数材料(high-k material)等介电材料。在一些实施例中,栅极110与介电层114可通过高介电常数金属栅极(high-k metal gate,hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在栅极110与介电层114之间可设置有功函数层(未示出)。在一些实施例中,顶盖层116可设置在栅极110的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于栅极110的顶面上的顶盖层116。顶盖层116的材料例如是氧化硅或氮化硅等介电材料。间隙壁118可设置在栅极110的侧壁上。间隙壁118可为单层结构或多层结构。间隙壁118的材料例如是氧化硅或氮化硅等介电材料。

66.栅极112可设置在隔离结构108上。栅极110与栅极112可彼此分离且彼此电连接。此外,栅极112可不跨设在鳍部f上。栅极112可作为栅极110的延伸部。

67.如图1d所示,存储器结构10还可包括介电层120、顶盖层122与间隙壁124中的至少一者。介电层120可设置在栅极112与隔离结构108之间。栅极112可为金属栅极。栅极112的材料可包括钨或氮化钛(tin)等导体材料。介电层120的材料例如是氧化硅或高介电常数材料等介电材料。在一些实施例中,栅极112与介电层120可通过高介电常数金属栅极(hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在栅极112与介电层120之间可设置有功函数层(未示出)。在一些实施例中,顶盖层122可设置在栅极112的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于栅极112的顶面上的顶盖层122。顶盖层122的材料例如是氧化硅或氮化硅等介电材料。间隙壁124可设置在栅极112的侧壁上。间隙壁124可为单层结构或多层结构。间隙壁124的材料例如是氧化硅或氮化硅等介电材料。

68.如图1a与图1c所示,存储器结构10还可包括接触窗126、接触通孔(contact via)128、导线130、接触通孔132与接触窗134。在本实施例中,接触窗126可穿过顶盖层116而电连接至栅极110,且接触窗134可穿过顶盖层122而电连接至栅极112,且栅极110可通过接触窗126、接触通孔128、导线130、接触通孔132与接触窗134而电连接至栅极112,但本发明并不以此为限。在一些实施例中,接触窗126、接触通孔128、导线130、接触通孔132、接触窗134的材料例如是钨、铝或铜等导体材料。此外,存储器结构10还可包括介电层136。接触窗126、接触通孔128、导线130、接触通孔132、接触窗134可位于介电层136中。在一些实施例中,介电层136可为多层结构。介电层136的材料例如是氧化硅、氮化硅或其组合。

69.此外,可依据产品需求来弹性调整栅极112的数量与形状。在本实施例中,存储器结构10可包括多个栅极112,且栅极112的数量不限于图中所示的数量。只要栅极112的数量为一个以上,即属于本发明所涵盖的范围。多个栅极112可彼此电连接。举例来说,多个栅极112可通过接触窗134而彼此电连接。接触窗134可为狭缝形接触窗(slot contact)。

70.请参照图1a与图1b,存储器结构10还可包括选择栅极138。选择栅极138设置在栅极110的一侧的鳍部f上。选择栅极138与鳍部f彼此电性绝缘。在一些实施例中,选择栅极138可跨设在多个鳍部f上。

71.此外,如图1b所示,存储器结构10还可包括介电层140、顶盖层142与间隙壁144中的至少一者。介电层140设置在选择栅极138与鳍部f之间,因此选择栅极138与鳍部f可彼此电性绝缘。此外,部分选择栅极138可设置在隔离结构108上(图1a)。选择栅极138可为金属栅极。在其他实施例中,选择栅极138可为多晶硅栅极。选择栅极138的材料可包括钨或氮化钛(tin)等导体材料。介电层140的材料例如是氧化硅或高介电常数材料等介电材料。在一些实施例中,选择栅极138与介电层140可通过高介电常数金属栅极(hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在选择栅极138与介电层140之间可设置有功函数层(未示出)。在一些实施例中,顶盖层142可设置在选择栅极138的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于选择栅极138的顶面上的顶盖层142。顶盖层142的材料例如是氧化硅或氮化硅等介电材料。间隙壁144可设置在选择栅极138的侧壁上。间隙壁144可为单层结构或多层结构。间隙壁144的材料例如是氧化硅或氮化硅等介电材料。

72.请参照图1a与图1b,存储器结构10还可包括掺杂区146、掺杂区148与掺杂区150。掺杂区146与掺杂区148可位于栅极110的两侧。举例来说,掺杂区146与掺杂区148可位于栅极110的两侧的鳍部f中。掺杂区148与掺杂区150可位于选择栅极138的两侧。举例来说,掺杂区148与掺杂区150可位于选择栅极138两侧的鳍部f中。此外,掺杂区148可位于栅极110与选择栅极138之间。举例来说,掺杂区148可位于栅极110与选择栅极138之间的鳍部f中。此外,存储器结构10还可包括轻掺杂漏极(lightly doped drain,ldd)152、轻掺杂漏极154、轻掺杂漏极156与轻掺杂漏极158。轻掺杂漏极152可位于掺杂区146与栅极110之间的鳍部f中。轻掺杂漏极154可位于掺杂区148与栅极110之间的鳍部f中。轻掺杂漏极156可位于掺杂区148与选择栅极138之间的鳍部f中。轻掺杂漏极158可位于掺杂区150与选择栅极138之间的鳍部f中。另外,存储器结构10还可包括阱区w。阱区w可位于基底100中。此外,掺杂区146、掺杂区148、掺杂区150、轻掺杂漏极152、轻掺杂漏极154、轻掺杂漏极156与轻掺杂漏极158可位于阱区w中。

73.掺杂区146、掺杂区148、掺杂区150、轻掺杂漏极152、轻掺杂漏极154、轻掺杂漏极156与轻掺杂漏极158可具有第一导电型,且阱区w可具有第二导电型。第一导电型与第二导电型为不同导电型。亦即,第一导电型与第二导电型可分别为n型导电型与p型导电型中的一者与另一者。

74.在另一些实施例中,掺杂区146、掺杂区148与掺杂区150可为由应变材料(strained material)所形成的应变型区域,且可省略轻掺杂漏极152、轻掺杂漏极154、轻掺杂漏极156与轻掺杂漏极158。以适用于p型金属氧化物半导体晶体管的材料为例,应变材料可为含锗的材料,如硅锗(sige)。掺杂区146、掺杂区148与掺杂区150可通过外延生长(epitaxial growth)技术所形成,如选择性外延生长(selective epitaxial growth,

seg)。

75.晶体管160至少包括栅极110、掺杂区146与掺杂区150。选择晶体管162至少包括选择栅极138、掺杂区146与掺杂区150。在晶体管160与选择晶体管162为n型金属氧化物半导体晶体管(nmos transistor)的情况下,第一导电型为n型,且第二导电型为p型。在晶体管160与选择晶体管162为p型金属氧化物半导体晶体管(pmos transistor)的情况下,第一导电型为p型,且第二导电型为n型。此外,晶体管160与选择晶体管162可分别为鳍式场效晶体管(finfet)。

76.在一些实施例中,存储器结构10还可包括接触窗164、接触通孔166、接触窗168、接触通孔170、接触窗172、接触通孔174与接触窗176中的至少一者。选择栅极138可通过接触窗164与接触通孔166而电连接至字线(word line)。接触窗168、接触窗172与接触窗176可分别电连接至鳍部f中的掺杂区146、掺杂区150与掺杂区148。接触窗168、接触窗172、接触窗176与电荷存储层104可源自于同一个材料层。亦即,接触窗168、接触窗172、接触窗176与电荷存储层104可通过相同工艺来同时形成。换句话说,电荷存储层104可视为鳍式场效晶体管工艺平台下的一种接触窗而以接触窗存储电荷。在一些实施例中,掺杂区146可通过接触窗168与接触通孔170而电连接至位线(bit line)。在一些实施例中,掺杂区150可通过接触窗172与接触通孔174而电连接至源极线(source line)。此外,接触窗176可连接至掺杂区148。接触窗168、接触窗172与接触窗176可为狭缝形接触窗。接触窗164、接触通孔166、接触窗168、接触通孔170、接触窗172、接触通孔174与接触窗176的材料例如是钨、铝或铜等导体材料。

77.请参照图1a与图1d,电荷存储层104邻近于(耦合于)栅极结构102。举例来说,电荷存储层104邻近于(耦合于)栅极112。电荷存储层104未电连接至电压源。电荷存储层104可位于栅极112的一侧。电荷存储层104可设置在隔离结构108上。此外,电荷存储层104于隔离结构108上的垂直投影可不重叠于栅极112于隔离结构108上的垂直投影。此外,电荷存储层104与栅极结构102彼此电性绝缘。举例来说,电荷存储层104与栅极112可通过介电层136与间隙壁124而彼此电性绝缘。

78.在本实施例中,存储器结构10可包括多个电荷存储层104,且电荷存储层104的数量不限于图中所示的数量。只要电荷存储层104的数量为一个以上,即属于本发明所涵盖的范围。此外,电荷存储层104的数量与栅极112的数量互相关联,电荷存储层104与栅极112的数量可影响栅极112与电荷存储层104之间的总耦合面积。总耦合面积越多,越能使电荷注入电荷存储层104或从电荷存储层104排出,进而可提升存储器元件的操作表现。因此,可依据产品需求来弹性调整电荷存储层104的数量与形状。此外,当电荷存储层104的数量为多个时,多个电荷存储层104可彼此电连接。举例来说,存储器结构10还可包括接触窗178。多个电荷存储层104可通过接触窗178而彼此电连接。电荷存储层104与接触窗178可为一体成型或各自独立的构件。接触窗178的材料例如是钨、铝或铜等导体材料。

79.请参照图1b至图1d,电荷存储层104与栅极结构102(如,栅极112)之间的介电材料(如,介电层136与间隙壁124)的厚度t1(图1d)可大于栅极结构102(如,栅极110)与鳍部f之间的介电材料(如,介电层114)的厚度t2(图1b与图1c)。亦即,电荷存储层104与栅极结构102之间的介电材料可具有较大的厚度,因此可防止存储在电荷存储层104中的电荷流失,进而提升存储器元件的数据保存能力。

80.请参照图1a与图1e,控制栅极106邻近于(耦合于)电荷存储层104。举例来说,控制栅极106可位于电荷存储层104的一侧。控制栅极106与电荷存储层104彼此电性绝缘。控制栅极106可设置在隔离结构108上。此外,控制栅极106于隔离结构108上的垂直投影可不重叠于电荷存储层104于隔离结构108上的垂直投影。此外,控制栅极106与电荷存储层104之间的总耦合面积可小于栅极112与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。

81.此外,如图1e所示,存储器结构10还可包括介电层180、顶盖层182与间隙壁184中的至少一者。介电层180可设置在控制栅极106与隔离结构108之间。控制栅极106可为金属栅极。控制栅极106的材料可包括钨或氮化钛(tin)等导体材料。介电层180的材料例如是氧化硅或高介电常数材料等介电材料。在一些实施例中,控制栅极106与介电层180可通过高介电常数金属栅极(hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在控制栅极106与介电层180之间可设置有功函数层(未示出)。在一些实施例中,顶盖层182可设置在控制栅极106的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于控制栅极106的顶面上的顶盖层182。顶盖层182的材料例如是氧化硅或氮化硅等介电材料。间隙壁184可设置在控制栅极106的侧壁上。间隙壁184可为单层结构或多层结构。间隙壁184的材料例如是氧化硅或氮化硅等介电材料。此外,控制栅极106与电荷存储层104可通过介电层136与间隙壁184而彼此电性绝缘。

82.请参照图1a与图1e,存储器结构10还可包括控制栅极186。控制栅极186邻近于(耦合于)电荷存储层104。举例来说,控制栅极186可位于电荷存储层104的一侧。控制栅极186与电荷存储层104彼此电性绝缘。控制栅极186可设置在隔离结构108上。此外,控制栅极186于隔离结构108上的垂直投影可不重叠于电荷存储层104于隔离结构108上的垂直投影。此外,控制栅极186与电荷存储层104之间的总耦合面积可小于栅极112与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。

83.此外,如图1e所示,存储器结构10还可包括介电层188、顶盖层190与间隙壁192中的至少一者。介电层188可设置在控制栅极186与隔离结构108之间。控制栅极186可为金属栅极。控制栅极186的材料可包括钨或氮化钛(tin)等导体材料。介电层188的材料例如是氧化硅或高介电常数材料等介电材料。在一些实施例中,控制栅极186与介电层188可通过高介电常数金属栅极(hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在控制栅极186与介电层188之间可设置有功函数层(未示出)。在一些实施例中,顶盖层190可设置在控制栅极186的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于控制栅极186的顶面上的顶盖层190。顶盖层190的材料例如是氧化硅或氮化硅等介电材料。间隙壁192可设置在控制栅极186的侧壁上。间隙壁192可为单层结构或多层结构。间隙壁192的材料例如是氧化硅或氮化硅等介电材料。此外,控制栅极186与电荷存储层104可通过介电层136与间隙壁192而彼此电性绝缘。

84.控制栅极106与控制栅极186分别可作为擦除栅极与编程栅极中的一者与另一者,但本发明并不以此为限。在另一些实施例中,可省略控制栅极186。在省略控制栅极186的情况下,控制栅极106可在擦除操作中作为擦除栅极,且可在编程操作中作为编程栅极。在本实施例中,以控制栅极106作为擦除栅极为例,且以控制栅极186作为编程栅极为例,但本发明并不以此为限。在本实施例中,由于存储器结构10包括控制栅极106与控制栅极186,且控

制栅极106与控制栅极186分别可作为擦除栅极与编程栅极,因此有助于降低电路设计的复杂度。

85.请参照图1a与图1e,存储器结构10还可包括耦合栅极194。耦合栅极194邻近于(耦合于)电荷存储层104。举例来说,耦合栅极194可位于电荷存储层104的一侧。耦合栅极194与电荷存储层104彼此电性绝缘。在一些实施例中,耦合栅极194可用以进行擦除禁止操作(erase inhibit),以防止未选定进行擦除的存储单元受到擦除。在一些实施例中,耦合栅极194可用以进行编程禁止操作(program inhibit),以防止未选定进行编程的存储单元受到编程。耦合栅极194可设置在隔离结构108上,耦合栅极194于隔离结构108上的垂直投影可不重叠于电荷存储层104于隔离结构108上的垂直投影。此外,控制栅极106与电荷存储层104之间的总耦合面积可小于耦合栅极194与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。另外,控制栅极186与电荷存储层104之间的总耦合面积可小于耦合栅极194与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。

86.此外,如图1e所示,存储器结构10还可包括介电层196、顶盖层198与间隙壁200中的至少一者。介电层196可设置在耦合栅极194与隔离结构108之间。耦合栅极194可为金属栅极。耦合栅极194的材料可包括钨或氮化钛(tin)等导体材料。介电层196的材料例如是氧化硅或高介电常数材料等介电材料。在一些实施例中,耦合栅极194与介电层196可通过高介电常数金属栅极(hkmg)技术来形成,但本发明并不以此为限。在一些实施例中,在耦合栅极194与介电层196之间可设置有功函数层(未示出)。在一些实施例中,顶盖层198可设置在耦合栅极194的顶面上,但本发明并不以此为限。在另一些实施例中,可省略位于耦合栅极194的顶面上的顶盖层198。顶盖层198的材料例如是氧化硅或氮化硅等介电材料。间隙壁200可设置在耦合栅极194的侧壁上。间隙壁200可为单层结构或多层结构。间隙壁200的材料例如是氧化硅或氮化硅等介电材料。此外,耦合栅极194与电荷存储层104可通过介电层136与间隙壁200而彼此电性绝缘。

87.在本实施例中,存储器结构10可包括多个耦合栅极194,且耦合栅极194的数量不限于图中所示的数量。只要耦合栅极194的数量为一个以上,即属于本发明所涵盖的范围。在一些实施例中,多个耦合栅极194可彼此电连接。在一些实施例中,存储器结构10还可包括接触窗202、接触通孔204、接触窗206、接触通孔208、接触窗210与接触通孔212中的至少一者。多个耦合栅极194可通过接触窗202而彼此电连接。接触窗202可为狭缝形接触窗。此外,耦合栅极194可通过接触窗202与接触通孔204而电连接至所对应的电压源。控制栅极106可通过接触窗206与接触通孔208而电连接至所对应的电压源。控制栅极186可通过接触窗210与接触通孔212而电连接至所对应的电压源。接触窗202、接触通孔204、接触窗206、接触通孔208、接触窗210与接触通孔212的材料例如是钨、铝或铜等导体材料。

88.以下,通过图1a、图2、表1与表2来说明存储器结构10的操作方法。

89.在本实施例中,以图1a所示的存储器结构10作为一个存储单元m。在图2中,存储单元阵列ma是以包括存储单元m1、存储单元m2、存储单元m3与存储单元m4为例,但本发明并不以此为限。存储单元m1、存储单元m2、存储单元m3与存储单元m4彼此耦接。此外,存储单元m1、存储单元m2、存储单元m3与存储单元m4可分别具有图1中的存储单元m的结构,且可互为镜像。

90.存储器结构10的操作方法包括对存储器结构10进行编程操作。编程操作可包括以下步骤。使电荷(如,电子)注入电荷存储层104。举例来说,可通过fn隧穿(fowler-nordheim tunneling)法使电荷由控制栅极186或控制栅极106注入电荷存储层104。此外,存储器结构10的操作方法包括对存储器结构10进行擦除操作。擦除操作可包括以下步骤。使电荷(如,电子)从电荷存储层104中排出。举例来说,可通过fn隧穿法使电荷从电荷存储层104中经由控制栅极186或控制栅极106排出。

91.举例来说,在晶体管160与选择晶体管162为nmos晶体管的情况下,对存储器结构100进行操作时的电压施加方式如下表1所示。通过表1的电压施加方式,在对存储单元m1进行擦除操作时,可对存储单元m2、存储单元m3与存储单元m4进行擦除禁止操作,以防止对存储单元m2、存储单元m3与存储单元m4进行擦除。此外,通过表1的电压施加方式,可同时对存储单元m1、存储单元m2、存储单元m3与存储单元m4进行编程操作。另外,通过表1的电压施加方式,可对选定的存储单元(如存储单元m1)进行读取操作。

92.表1

[0093][0094]

举例来说,在晶体管160与选择晶体管162为pmos晶体管的情况下,对存储器结构100进行操作时的电压施加方式如下表2所示。通过表2的电压施加方式,在对存储单元m1进行编程操作时,可对存储单元m2、存储单元m3与存储单元m4进行编程禁止操作,以防止对存储单元m2、存储单元m3与存储单元m4进行编程。此外,通过表2的电压施加方式,可同时对存储单元m1、存储单元m2、存储单元m3与存储单元m4进行擦除操作。另外,通过表2的电压施加方式,可对选定的存储单元(如存储单元m1)进行读取操作。

[0095]

表2

[0096]

[0097][0098]

基于上述实施例可知,在存储器结构10及其操作方法中,由于电荷可存储在耦合于栅极结构102的电荷存储层104中,因此可防止存储在电荷存储层104中的电荷流失,进而提升存储器元件的数据保存能力。

[0099]

图3a为根据本发明另一实施例的存储器结构的上视图。在图3a中,省略图3b与图3c中的部分构件,以清楚地描述图3a中的构件之间的配置关系。图3b为沿着图3a中的v-v’剖面线的剖视图。图3c为沿着图3a中的vi-vi’剖面线的剖视图。

[0100]

请参照图1a与图3a至图3b,图3a的存储器结构20与图1a的存储器结构10的差异如下。在存储器结构20中,电荷存储层104还可位于栅极112的顶面上。此外,电荷存储层104于隔离结构108上的垂直投影可部分重叠于栅极112于隔离结构108上的垂直投影。电荷存储层104与栅极结构102彼此电性绝缘。举例来说,电荷存储层104与栅极112可通过顶盖层122与间隙壁124而彼此电性绝缘。电荷存储层104与栅极结构102(如,栅极112)之间的间隙壁124(介电材料)的厚度t3(图3b)可大于栅极结构102(如,栅极110)与鳍部f之间的介电层114(介电材料)的厚度t2(图1b与图1c)。电荷存储层104与栅极结构102(如,栅极112)之间的顶盖层122(介电材料)的厚度t4(图3b)可大于栅极结构102(如,栅极110)与鳍部f之间的介电层114(介电材料)的厚度t2(图1b与图1c)。亦即,电荷存储层104与栅极结构102之间的介电材料可具有较大的厚度,因此可防止存储在电荷存储层104中的电荷流失,进而提升存储器元件的数据保存能力。

[0101]

如图3c所示,在存储器结构20中,电荷存储层104可位于控制栅极106的一侧,且还可位于控制栅极106的顶面上。此外,电荷存储层104于隔离结构108上的垂直投影可部分重叠于控制栅极106于隔离结构108上的垂直投影。电荷存储层104与控制栅极106可彼此电性绝缘。举例来说,电荷存储层104与控制栅极106可通过顶盖层182与间隙壁184而彼此电性绝缘。在存储器结构20中,电荷存储层104可位于控制栅极186的一侧,且还可位于控制栅极186的顶面上。电荷存储层104与控制栅极186可彼此电性绝缘。举例来说,电荷存储层104与控制栅极186可通过顶盖层190与间隙壁192而彼此电性绝缘。在存储器结构20中,电荷存储层104可位于耦合栅极194的一侧,且还可位于耦合栅极194的顶面上。电荷存储层104与耦合栅极194可彼此电性绝缘。举例来说,电荷存储层104与耦合栅极194可通过顶盖层198与间隙壁200而彼此电性绝缘。

[0102]

此外,存储器结构20与存储器结构10中相同的构件使用相同的符号表示,且存储器结构20与存储器结构10中相似的内容,可参考上述实施例对存储器结构10的说明,于此不再说明。

[0103]

图4a为根据本发明另一实施例的存储器结构的上视图。在图4a中,省略图4b中的部分构件,以清楚地描述图4a中的构件之间的配置关系。图4b为沿着图4a中的vii-vii’剖面线的剖视图。

[0104]

请参照图1a与图4a与图4b,图4a的存储器结构30与图1a的存储器结构10的差异如下。在存储器结构30中,省略图1a中的栅极112。亦即,在存储器结构30中,栅极结构102仅包括栅极110。电荷存储层104可邻近于(耦合于)栅极110。举例来说,电荷存储层104可位于栅极110的顶面上。此外,电荷存储层104于隔离结构108上的垂直投影可部分重叠于栅极110于隔离结构108上的垂直投影。电荷存储层104与栅极结构102彼此电性绝缘。举例来说,电荷存储层104与栅极110可通过顶盖层116与间隙壁118而彼此电性绝缘。电荷存储层104与栅极结构102(即,栅极110)之间的顶盖层116(介电材料)的厚度t5可大于栅极结构102(即,栅极110)与鳍部f之间的介电层114(介电材料)的厚度t2。电荷存储层104与栅极结构102(即,栅极110)之间的间隙壁118(介电材料)的厚度t6可大于栅极结构102(即,栅极110)与鳍部f之间的介电层114(介电材料)的厚度t2。亦即,电荷存储层104与栅极结构102之间的介电材料可具有较大的厚度,因此可防止存储在电荷存储层104中的电荷流失,进而提升存储器元件的数据保存能力。

[0105]

在存储器结构30中,电荷存储层104可位于控制栅极106的一侧,且还可位于控制栅极106的顶面上。此外,电荷存储层104于隔离结构108上的垂直投影可部分重叠于控制栅极106于隔离结构108上的垂直投影。电荷存储层104与控制栅极106可彼此电性绝缘。举例来说,电荷存储层104与控制栅极106可通过顶盖层182与间隙壁184而彼此电性绝缘。控制栅极106与电荷存储层104之间的总耦合面积可小于栅极110与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。在存储器结构30中,电荷存储层104可位于控制栅极186的一侧,且还可位于控制栅极186的顶面上。此外,电荷存储层104于隔离结构108上的垂直投影可部分重叠于控制栅极186于隔离结构108上的垂直投影。电荷存储层104与控制栅极186可彼此电性绝缘。举例来说,电荷存储层104与控制栅极186可通过顶盖层190与间隙壁192而彼此电性绝缘。控制栅极106与电荷存储层104之间的总耦合面积可小于控制栅极186与电荷存储层104之间的总耦合面积,因此有助于提升存储器元件的操作表现。

[0106]

此外,在存储器结构30中,还可省略图1a中的接触窗176与耦合栅极194等构件。另外,存储器结构30与存储器结构10中相同的构件使用相同的符号表示,且存储器结构30与存储器结构10中相似的内容,可参考上述实施例对存储器结构10的说明,于此不再说明。

[0107]

基于上述实施例可知,在存储器结构30中,由于省略图1a中的栅极112,因此可有效地缩小存储器结构30的尺寸。另一方面,由于存储器结构10与存储器结构20分别具有延伸的栅极112,因此有利于提升栅极结构102与电荷存储层104之间的总耦合面积,进而可提升存储器元件的操作表现。

[0108]

综上所述,在上述实施例的存储器结构及其操作方法中,由于电荷可存储在耦合于栅极结构的电荷存储层中,因此可防止存储在电荷存储层中的电荷流失,进而提升存储器元件的数据保存能力。

[0109]

虽然本发明已以实施例揭示如上,然而其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,可作些许的更改与润饰,故本发明的保护范围应当

以权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1