非挥发性存储器的存储单元的制作方法

1.本发明涉及一种非挥发性存储器的存储单元,且特别是涉及一种非挥发性存储器的存储单元中具有不对称间隙壁(spacer)的存储元件(memory device)。

背景技术:

2.请参照图1,其所绘示为现有运用于非挥发性存储器的存储元件示意图。该存储元件披露于美国专利us 7,551,494。存储元件10为一p沟道晶体管(p-channel transistor)。

3.如图1所示,存储元件10制作于隔离结构15之间,隔离结构15为浅沟槽隔离结构(shallow trench isolation structure,简称sti)。存储元件10包括:n型阱区(n well region)11、控制栅极层(gate layer)18、栅极介电层(gate dielectric layer)16、氧-氮-氧间隙壁(ono spacer)20、p型源极掺杂区(p+source doped region)12与p型漏极掺杂区(p+drain doped region)14。

4.栅极介电层16与控制栅极层18堆叠于n型阱区11表面上方。再者,氧-氮-氧间隙壁20围绕于栅极介电层16与控制栅极层18的侧壁(side wall)。在n型阱区11表面下方,p型源极掺杂区12位于氧-氮-氧间隙壁20的一侧,而p型漏极掺杂区14位于氧-氮-氧间隙壁20的另一侧。换句话说,栅极介电层16、控制栅极层18与氧-氮-氧间隙壁20位于p型源极掺杂区12与p型漏极掺杂区14之间的n型阱区11表面上方。

5.在n型阱区11表面下方,p型源极掺杂区12与p型漏极掺杂区14之间为沟道区域(channel region)。沟道区域包括:第一沟道(first channel)19、第二沟道(second channel)29与第三沟道(third channel)39。第一沟道19、第二沟道29与第三沟道39的沟道长度(channel length)分别为l1、l2与l3。第一沟道19位于控制栅极层18正下方,第二沟道29位于p型漏极掺杂区14与第一沟道19之间,第三沟道39位于第一沟道19与p型源极掺杂区12之间。

6.再者,氧-氮-氧间隙壁20包括:氧化硅层(silicon oxide layer)22、氮化硅层(silicon nitride layer)24与氧化硅层26。氧化硅层22接触于栅极介电层16与控制栅极层18的侧壁,且氧化硅层22接触于n型阱区11表面并延伸至p型源极掺杂区12与p型漏极掺杂区14。再者,氮化硅层24覆盖于氧化硅层22上,且氧化硅层26覆盖于氮化硅层24上。基本上,氮化硅层24为电荷抓取层(charge-trapping layer)。

7.请参照图2,其所绘示为现有存储元件进行编程动作(program operation)的偏压示意图。对存储元件10进行编程动作时,p型漏极掺杂区14接收漏极电压vd,p型源极掺杂区12为浮接(floating),n型阱区11接收接地电压(亦即,v

nw

=0v),控制栅极层18接收栅极电压vg。举例来说,漏极电压vd=-3v~-5v,栅极电压vg=0v~2v。在上述的偏压条件下,控制栅极层18下方的第一沟道19会被关闭(turn off)。再者,n型阱区11与p型漏极掺杂区14之间的结(junction)会产生电子空穴对(electron-hole pairs),并发生带间热电子注入效应(band-to-band hot electron injection,简称bbhe效应),使得电子由第二沟道29注入漏极侧(drain side)的氮化硅层24中。

8.当然,除了利用bbhe效应之外,也可以利用其他的偏压方式来对存储元件10进行编程动作。举例来说,提供栅极电压vg来开启(turn on)第一沟道19,并发生沟道热空穴感应热电子注入效应(channel hot hole induced hot electron injection,简称chhihe效应),使得电子由第二沟道29注入漏极侧(drain side)的氮化硅层24中。另外,由于电子是由第二沟道29注入氮化硅层24,所以注入沟道长度与总沟道长度之间的比值为

9.换句话说,在编程动作时,控制电子注入或者不注入第二沟道29上方的氮化硅层24可以使得存储元件10呈现二种不同的存储状态(storage state)。再者,提供其他的偏压也可以对存储元件10进行抹除动作(erase operation)与读取动作(read operation),其详细运作原理不再赘述。

10.利用现今半导体工艺来制作存储元件10,接触于控制栅极层18侧壁的氧-氮-氧间隙壁20会呈现对称的形状。因此,存储元件10中的第二沟道29与第三沟道39的长度几乎相同。

技术实现要素:

11.本发明的主要目的在于提出一种非挥发性存储器的存储单元,存储单元中的存储元件具有不对称间隙壁。在编程动作时,更多载流子可注入较宽间隙壁的电荷抓取层(charge-trapping layer)。再者,本发明设计出特别结构的存储单元。举例来说,设计较长的第二沟道,用以提高注入沟道长度与总沟道长度之间的比值。因此,能够更有效率地进行编程动作。

12.本发明是有关于一种非挥发性存储器的存储单元,该存储单元具有一存储元件,该存储元件包括:一阱区;一栅极结构,形成于该阱区的一表面上,且该栅极结构包括至少一凸出部;一间隙壁,围绕于该栅极结构的一侧壁,且该间隙壁接触该阱区的该表面,其中该间隙壁包括一第一部分与一第二部分;以及,一第一掺杂区与一第二掺杂区,形成于该阱区的该表面下方,且该第一掺杂区与该第二掺杂区之间为一沟道区域,该沟道区域包括一第一沟道与一第二沟道;其中,该栅极结构的该侧壁包括多个表面,且该至少一凸出部的一第一表面平行于该沟道区域中的一沟道长度方向;其中,该第一沟道位于该栅极结构下方,该第二沟道位于该第一沟道与该第二掺杂区域之间,且该第一部分的该间隙壁位于该第二沟道上方;其中,在一编程动作时,多个载流子经由该第二沟道注入该第一部分的该间隙壁中的一电荷抓取层。

13.本发明是有关于一种非挥发性存储器的存储单元,该存储单元包括:一存储元件,包括:一阱区、一第一栅极结构、一第一间隙壁、一第一掺杂区与一第二掺杂区;该第一栅极结构形成于该阱区的一表面上,且该第一栅极结构包括至少一凸出部;该第一间隙壁围绕于该第一栅极结构的一侧壁,该第一间隙壁接触该阱区的该表面,且该第一间隙壁包括一第一部分与一第二部分;该第一掺杂区与该第二掺杂区形成于该阱区的该表面下方,且该第一掺杂区与该第二掺杂区之间为一沟道区域,该沟道区域包括一第一沟道与一第二沟道;该第一栅极结构的该侧壁包括多个表面,且该至少一凸出部的一第一表面平行于该沟道区域中的一沟道长度方向;该第一沟道位于该第一栅极结构下方,该第二沟道位于该第

一沟道与该第二掺杂区域之间,该第一部分的该第一间隙壁位于该第二沟道上方;以及,一选择晶体管,包括:该阱区、一第二栅极结构、一第二间隙壁与一第三掺杂区;该第二栅极结构形成于该阱区的该表面上;该第二间隙壁围绕于该第二栅极结构的一侧壁,且该第二间隙壁接触该阱区的该表面;该第三掺杂区形成于该阱区的该表面下方;该第一掺杂区与该第三掺杂区之间为一第四沟道,且该第四沟道位于该第二栅极结构下方;其中,在一编程动作时,多个载流子经由该存储元件的该第二沟道注入该第一部分的该第一间隙壁中的一电荷抓取层。

14.为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合所附的附图,作详细说明如下:

附图说明

15.图1为现有运用于非挥发性存储器的存储元件示意图;

16.图2为现有存储元件进行编程动作的偏压示意图;

17.图3a至图3f为本发明第一实施例非挥发性存储器的存储单元的制作流程俯视图与a-b方向的剖视图;

18.图3g为第一实施例存储单元进行各种动作时的偏压示意图;

19.图4a与图4b为第一实施例来修改的第一变化型存储元件及其进行各种动作的偏压示意图;

20.图4c为第一实施例来修改的第二变化型存储元件的示意图;

21.图4d为第一实施例来修改的第三变化型存储元件的示意图;

22.图4e为第一实施例来修改的第四变化型存储元件的示意图;

23.图4f为第一实施例来修改的第五变化型存储元件的示意图;

24.图5a与图5b为本发明第二实施例非挥发性存储器的存储单元俯视图与a-b方向的剖视图;

25.图5c为第二实施例存储单元中的存储元件进行各种动作时的偏压示意图;

26.图5d为n沟道晶体管作为存储元件并进行各种动作时的偏压示意图;

27.图5e为第二实施例来修改的第二变化型存储元件的示意图;

28.图6a与图6b为本发明第三实施例非挥发性存储器的存储单元俯视图与a-b方向的剖视图;以及

29.图7a与图7b为本发明第四实施例非挥发性存储器的存储单元俯视图与a-b方向的剖视图。

30.符号说明

31.10:存储元件

32.11:n型阱区

33.12,14:掺杂区

34.15:隔离结构

35.16:栅极介电层

36.18:控制栅极层

37.19:第一沟道

38.20:间隙壁

39.22,26:氧化硅层

40.24:氮化硅层

41.29:第二沟道

42.39:第三沟道

43.300,300a,300c,300d,300e,300f,300g,300h,500,500e:存储元件

44.310,310a,310d,310e,310f,610:阱区

45.320,340,320a,340a,320c,320d,340d,320e,340e,320f,340f:掺杂区

46.322,342,322d,342d,322e,342e,322f,342f,641,652:金属电极

47.330,330d,330e,330f,630,670:间隙壁

48.332,336,632,636,672,676:氧化硅层

49.334,634,674:氮化硅层

50.380,660,680:栅极结构

51.380a,380b,410:凸出部

52.380c,380d,411:表面

53.382,662,682:栅极介电层

54.384,384d,384e,384f,664,684:控制栅极层

55.386:开口

56.391,691:第一沟道

57.392,692:第二沟道

58.393,693:第三沟道

59.400,622,652:延伸部

60.502,502e,702:辅助电极

61.504,704:介电层

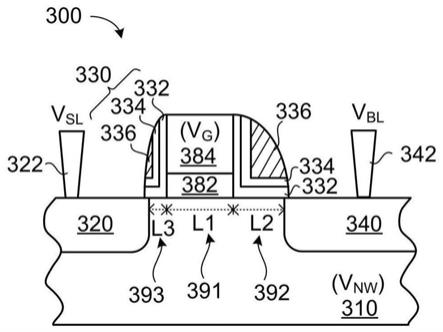

62.620,640,650:掺杂区

63.694:第三沟道

具体实施方式

64.请参照图3a至图3f,其所绘示为本发明第一实施例非挥发性存储器的存储单元的制作流程俯视图与a-b方向的剖视图。

65.如图3a与图3b所示,在阱区(well region)310上形成一c形(c-shaped)的栅极结构380。栅极结构380具有两个互相平行的凸出部(protrusion part)380a、380b,两个凸出部380a、380b有面对面的表面(surface)380c、380d。换句话说,两个凸出部380a、380b可建构成c形的栅极结构380,并定义出一开口(notch)386。再者,栅极结构380包括栅极介电层382与控制栅极层(control gate layer)384。栅极介电层382先形成于阱区310表面上,而控制栅极层384再覆盖于栅极介电层382。其中,控制栅极层384为多晶硅(polysilicon)控制栅极层,栅极介电层382为氧化硅层(silicon oxide layer)。

66.如图3c与图3d所示,形成一间隙壁330围绕于栅极结构380的侧壁(side wall)。其中,间隙壁330为氧-氮-氧间隙壁(ono spacer)。间隙壁330包括:氧化硅层332、氮化硅层

334与氧化硅层336。氧化硅层332接触于栅极结构380的侧壁,且氧化硅层332接触于阱区310的表面。氮化硅层334覆盖于氧化硅层332上。氧化硅层336覆盖于氮化硅层334上。其中,氮化硅层334为电荷抓取层(charge-trapping layer)。

67.根据本发明的实施例,在进行间隙壁330工艺时,由于间隙壁330的材料同时填充并接触于c形栅极结构380开口386处的三个表面(亦即,两个表面380c与380d加上两个表面380c与380d之间的表面),因此进行蚀刻后c形栅极结构380开口386处会残留较多的间隙壁330材料,使得栅极结构380两侧形成不对称间隙壁330。换句话说,间隙壁330包括右侧部分与左侧部分,右侧部分与左侧部分的宽度相异,且右侧部分的物理高度会比左侧部分高。右侧部分间隙壁330位于两个凸出部380a、380b并接触于c形栅极结构380开口386处的三个表面。因此,如图3d所示,宽度相异的右侧部分间隙壁330的宽度大于左侧部分间隙壁330的宽度。

68.如图3e与图3f所示,进行源/漏掺杂工艺(source/draindoping process),在栅极结构380与间隙壁330的两侧形成第一掺杂区320与第二掺杂区340。而利用金属电极322、342分别连接至第一掺杂区320与第二掺杂区340后,即完成存储元件300。其中,第一掺杂区320与第二掺杂区340为p型掺杂区,阱区310为n型阱区。换言之,本发明第一实施例非挥发性存储器的存储单元包括一存储元件300,存储元件300为一p沟道晶体管(p-channel transistor),第一掺杂区320为源极(source),第二掺杂区340为漏极(drain)。

69.如图3e与图3f所示,阱区310表面下方第一掺杂区320与第二掺杂区340之间为沟道区域(channel region)。其中,栅极结构380的两个表面380c、380d平行于沟道区域的沟道长度方向(length direction)。沟道区域包括:第一沟道391、第二沟道392与第三沟道393。第一沟道391、第二沟道392与第三沟道393的沟道长度分别为l1、l2与l3。第一沟道391位于栅极结构380正下方,位于第二沟道392与第三沟道393之间。第二沟道392位于第二掺杂区340与第一沟道391之间。第三沟道393位于第一掺杂区320与第一沟道391之间。另外,右侧部分较宽的间隙壁330位于第二沟道392上方,左侧部分较窄的间隙壁330位于第三沟道393上方。

70.在本发明的实施例中,存储元件300具有c形的栅极结构380,亦即栅极结构380的侧壁中,有三个表面相邻于第二沟道392,可残留较多间隙壁330的材料,造成较宽的间隙壁330。如图3f所示,间隙壁330的氧化硅层332接触于栅极结构380的侧壁,且氧化硅层332接触于阱区310的表面并分别延伸至第一掺杂区320与第二掺杂区340。在氧化硅层332上覆盖氮化硅层334与氧化硅层336,并进行蚀刻后,将可形成不对称的间隙壁330。由于栅极结构380两侧形成宽度不同的间隙壁330,将使得第二沟道392与第三沟道393的长度不同。根据本发明的实施例,第二沟道392的长度大于第三沟道393的长度,且第二沟道392的长度小于等于第三沟道393的三倍长度。也就是说,右侧间隙壁330的宽度大于左侧间隙壁330的宽度,右侧间隙壁330的宽度小于3倍左侧间隙壁330的宽度。再者,由于右侧间隙壁330较宽,所以右侧间隙壁330有更长的氮化硅层334可以存储更多的电子。

71.基此,由于右侧部分间隙壁330在物理高度上较高,可在进行源/漏掺杂工艺时阻挡更多掺杂离子(dopant ion)以防止氧化硅层332下方形成第二掺杂区340,如此可提高第二沟道392的长度,使存储元件300具有较长的第二沟道392,所以注入沟道长度与总沟道长

度之间的比值(亦即,)会增加。当存储元件300进行编程动作时,将有更多的载流子(carrier)经由第二沟道392注入间隙壁330的氮化硅层334。因此,本发明的存储元件300可更有效率的进行编程动作,并缩短编程动作的时间。

72.请参照图3g,其所绘示为第一实施例存储单元进行各种动作时的偏压示意图。其中,第一掺杂区320接收源极线电压v

sl

、第二掺杂区340接收位线电压v

bl

、控制栅极层384接收栅极电压vg、阱区310接收阱区电压(well voltage,v

nw

)。值得注意的是,图3e与图3f为简化绘图,所以连接于控制栅极层384上用来接收栅极电压vg的接触点会予以省略并未绘示。

73.利用带间热电子注入效应(bbhe效应)来对存储元件300进行编程动作(pgm)时,源极线电压v

sl

为浮接(floating)、栅极电压vg为大于等于0v的电压、位线电压v

bl

为-6v、阱区电压v

nw

为0v。由于栅极电压vg大于位线电压v

bl

,栅极结构380下方的第一沟道391会被关闭(turn off)。再者,阱区310与第二掺杂区340之间的结(junction)会产生电子空穴对(electron-hole pairs),并发生bbhe效应,使得电子由第二沟道392注入漏极侧(drain side)的氮化硅层334中。也就是说,电子由第二沟道392注入靠近第二掺杂区340侧较宽间隙壁330中的电荷抓取层。

74.利用沟道热电子注入效应(channel hot electron injection,简称che效应)来对存储元件300进行编程动作(pgm)时,源极线电压v

sl

为0v、栅极电压vg为-1v、位线电压v

bl

为-6v、阱区电压v

nw

为0v。由于栅极电压vg小于源极线电压v

sl

,栅极结构380下方的第一沟道391会被开启(turn on),第一掺杂区320与第二掺杂区340之间的沟道区域(channel region)开启,产生编程电流(programcurrent)。当电子经过第二沟道392时,che效应发生,使得电子由第二沟道392注入漏极侧(drain side)的氮化硅层334中。也就是说,电子由第二沟道392注入靠近第二掺杂区340侧较宽间隙壁330中的电荷抓取层。

75.利用沟道热空穴注入效应(channel hot hole injection,简称chh效应)来对存储元件300进行抹除动作(ers)时,源极线电压v

sl

为0v、栅极电压vg为-6v、位线电压v

bl

为-6v、阱区电压v

nw

为0v。由于栅极电压vg小于源极线电压v

sl

,栅极结构380下方的第一沟道391会被开启(turn on),第一掺杂区320与第二掺杂区340之间的沟道区域(channel region)开启。当空穴经过第二沟道392时,chh效应发生,使得空穴由第二沟道392注入漏极侧(drainside)的氮化硅层334中,使得氮化硅层334中的电子与空穴结合以完成抹除动作(ers)。

76.利用沟道fn隧穿效应(fowler-nordheim tunneling,简称fn效应)来对存储元件300进行抹除动作(ers)时,源极线电压v

sl

为+6v、栅极电压vg为-6v、位线电压v

bl

为+6v、阱区电压v

nw

为+6v。由于栅极电压vg小于阱区电压v

nw

,fn效应发生,使得氮化硅层334中的电子由氮化硅层334退出(eject)至阱区310以完成抹除动作(ers)。

77.利用带间热空穴注入效应(band-to-band hot hole injection,简称bbhh效应)来对存储元件300进行抹除动作(ers)时,源极线电压v

sl

为浮接、栅极电压vg为-6v、位线电压v

bl

为-6v、阱区电压v

nw

为0v。由于栅极电压vg以及位线电压v

bl

为-6v,栅极结构380下方的第一沟道391会被关闭(turn off)。再者,阱区310与第二掺杂区340之间的结(junction)会产生电子空穴对(electron-hole pair)并产生带间热空穴注入效应(bbhh效应)。因此,空穴由第二沟道392注入漏极侧(drain side)的氮化硅层334中,使得氮化硅层334中的电子

与空穴结合以完成抹除动作(ers)。

78.对存储元件300进行读取动作(read)时,源极线电压v

sl

为-1v、栅极电压vg为-1v、位线电压v

bl

为0v、阱区电压v

nw

为0v。此时,第一掺杂区320与第二掺杂区340之间的沟道区域(channel region)开启,并产生读取电流(read current)。基本上,当存储元件300的氮化硅层334中存储电子时,读取电流比较大,可视为存储元件300的第一存储状态。反之,当存储元件300的氮化硅层334中未存储电子/空穴时,读取电流比较小,可视为存储元件300的第二存储状态。换言之,根据读取电流的大小可以决定存储元件300的存储状态。

79.基本上,上述存储单元中,存储元件300的各种动作所提供的偏压仅是本发明的范例而已,并非用来限制本发明。在此领域的技术人员可以修改各种动作的偏压,并对存储元件300进行编程动作、抹除动作与读取动作。

80.另外,本发明第一实施例存储单元内的存储元件也不限定于p沟道晶体管(p-channel transistor),第一实施例存储单元中的存储元件也可以是n沟道晶体管(n-channel transistor)。

81.请参照图4a,其所绘示为根据第一实施例来修改的第一变化型存储元件。存储单元中的第一变化型存储元件300a为n沟道晶体管。图4b为第一变化型存储元件进行各种动作的偏压示意图。其中,存储元件300a与存储元件300的结构类似,以下说明之。

82.如图4a所示,存储单元中的存储元件300a包括:阱区310a、栅极介电层382、控制栅极层384、间隙壁330、第一掺杂区320a与第二掺杂区340a。间隙壁330包括:氧化硅层332、氮化硅层334与氧化硅层336。另外,第一掺杂区320a与第二掺杂区340a为n型掺杂区,且阱区310a为p型阱区。相同地,在阱区310a表面下方第一掺杂区320a与第二掺杂区340a之间为沟道区域(channel region)。沟道区域包括:第一沟道391、第二沟道392与第三沟道393。

83.由于存储元件300a具有c形的栅极结构,亦即栅极结构的侧壁三个表面相邻于第二沟道392。因此,可在栅极结构两侧形成宽度不同的间隙壁330,将使得第二沟道392与第三沟道393的长度不同。根据本发明的实施例,第二沟道392的长度大于第三沟道393的长度,且第二沟道392的长度小于等于第三沟道393的三倍长度。

84.如图4b所示,第一掺杂区320a接收源极线电压v

sl

、第二掺杂区340a接收位线电压v

bl

、控制栅极层484接收栅极电压vg、阱区310a接收阱区电压v

pw

。

85.利用带间热空穴注入效应(band-to-band hot hole injection,简称bbhh效应)来对存储元件300a进行编程动作(pgm)时,源极线电压v

sl

为浮接(floating)、栅极电压vg为小于等于0v的电压、位线电压v

bl

为+6v、阱区电压v

pw

为0v。由于栅极电压vg小于位线电压v

bl

,第一沟道391会被关闭(turn off)。再者,阱区310a与第二掺杂区340a之间的结(junction)会产生电子空穴对(electron-hole pairs),并发生bbhh效应,使得空穴由第二沟道392注入漏极侧(drain side)的氮化硅层334中。也就是说,空穴由第二沟道392注入靠近第二掺杂区340侧较宽间隙壁330中的电荷抓取层。

86.利用沟道热电子注入效应(channel hot electron injection,简称che效应)来对存储元件300a进行抹除动作(ers)时,源极线电压v

sl

为0v、栅极电压vg为+6v、位线电压v

bl

为+6v、阱区电压v

pw

为0v。由于栅极电压vg大于源极线电压v

sl

,第一沟道391会被开启(turn on),第一掺杂区320a与第二掺杂区340a之间的沟道区域(channel region)开启。当电子经过第二沟道392时,che效应发生,使得电子由第二沟道392注入漏极侧(drain side)的氮化

硅层334中,使得氮化硅层334中的电子与空穴结合,以完成抹除动作。

87.对存储元件300a进行读取动作(read)时,源极线电压v

sl

为+1v、栅极电压vg为+1v、位线电压v

bl

为0v、阱区电压v

pw

为0v。此时,第一掺杂区320a与第二掺杂区340a之间的沟道区域(channel region)开启,并产生读取电流(read current)。因此,根据读取电流的大小可以决定存储元件300a的存储状态。

88.再者,本发明第一实施例存储单元中的存储元件的栅极结构也不限定为c形(c-shaped)的栅极结构,在此领域的技术人员也可以将c形的栅极结构修改为其他形状的栅极结构,并且制造出不对称的间隙壁。

89.请参照图4c,其所绘示为根据第一实施例来修改的第二变化型存储元件。相较于图3f中的存储元件300,图4c存储元件300c内的第一掺杂区320c还包括一延伸部400,其为轻掺杂漏极区(lightly doped drain region,简称ldd区)。也就是说,在较窄间隙壁300的那一侧会额外进行一轻掺杂漏极工艺(lightly doped drain process,简称ldd工艺)。当第一掺杂区320c的延伸部400完成后,较窄间隙壁300下方的第三沟道将会消失,使得注入沟道长度与总沟道长度之间的比值(亦即,)增加。因此,存储元件300c可更有效率的进行编程动作。值得注意地,较宽间隙壁300的那一侧可以不进行ldd工艺,亦即让第二沟道392存在而不消失。由于第二沟道392仍存在,所以电子即可经由第二沟道392注入漏极侧(drain side)的氮化硅层334中。

90.请参照图4d,其所绘示为根据第一实施例来修改的第三变化型存储元件。存储元件300d具有l形的控制栅极层384d,亦即存储元件300d具有l形的栅极结构。栅极结构具有一个凸出部410,凸出部410的表面411则平行于沟道区域的沟道区域长度方向。再者,间隙壁330d围绕于栅极结构的侧壁。于进行源/漏掺杂工艺后,在阱区310d内所形成的第一掺杂区320d与第二掺杂区340d分别位于间隙壁330d的两侧。将金属电极322d、342d分别连接至第一掺杂区320d与第二掺杂区340d,即完成存储元件300d。

91.基本上,在进行间隙壁330d形成工艺时,由于间隙壁330d的材料同时填充于l形栅极结构角落(corner)处,因此进行蚀刻后l形栅极结构角落处会残留较多的间隙壁330d材料。也就是说,形成于右侧部分的间隙壁330d会接触于凸出部410的表面411,并接触于l型栅极结构中垂直于表面411的另一侧壁表面。因此,在l型栅极结构的左右两侧即形成宽度不同的间隙壁330d。

92.另外,存储元件300d沿a-b线的剖视图则类似于图3f,此处不再赘述。再者,由于存储元件300d具有l型的栅极结构,将使得栅极结构的侧壁两个表面相邻于第二沟道。

93.请参照图4e,其所绘示为根据第一实施例来修改的第四变化型存储元件。相较于图3e的存储元件300,存储元件300e的栅极结构还延伸至相邻存储元件300g、300h。亦即,存储元件300e、300g、300h共用(shared)控制栅极层384e,且存储元件300e、300g、300h的结构完全相同。

94.相同地,存储元件300e的控制栅极层384e的开口处会残留较多的间隙壁330e材料,使得栅极结构两侧形成宽度不同的间隙壁330e。再者,进行源/漏掺杂工艺后所形成的第一掺杂区320e与第二掺杂区340e分别位于间隙壁330e的两侧。将金属电极322e、342e分别连接至第一掺杂区320e与第二掺杂区340e,即完成存储元件300e。

95.另外,存储元件300e沿a-b线的剖视图则类似于图3f,此处不再赘述。再者,由于存储元件300e具有c型的栅极结构,将使得栅极结构的侧壁三个表面相邻于第二沟道。

96.请参照图4f,其所绘示为根据第一实施例来修改的第五变化型存储元件。相较于图3e的存储元件300,存储元件300f的沟道宽度(channel width)较窄。也就是说,本发明可以根据半导体的工艺规范,设计出较窄的沟道,以降低存储元件300f的尺寸(size)。

97.相同地,存储元件300f的控制栅极层384f的开口处会残留较多的间隙壁330f材料,使得栅极结构两侧形成宽度不同的间隙壁330f。再者,进行源/漏掺杂工艺后所形成的第一掺杂区320f与第二掺杂区340f分别位于间隙壁330f的两侧。将金属电极322f、342f分别连接至第一掺杂区320f与第二掺杂区340f,即完成存储元件300f。

98.另外,存储元件300f沿a-b线的剖视图则类似于图3f,此处不再赘述。再者,由于存储元件300f具有c型的栅极结构,将使得栅极结构的侧壁三个表面相邻于第二沟道。

99.由以上的说明可知,为了让存储元件具有不对称的间隙壁330。本发明的存储元件具有特殊形状的栅极结构,栅极结构的侧壁有多个面,而设计栅极结构380至少有侧壁的两个表面相邻于第二沟道,使得第二沟道上方形成较宽的间隙壁。

100.请参照图5a与图5b,其所绘示为本发明第二实施例非挥发性存储器的存储单元俯视图与a-b方向的剖视图。第二实施例的存储单元包括一存储元件500,此存储元件500是在第一实施例存储元件300的基础上再设计一辅助电极(assisted electrode)502用以加强存储元件500的编程与抹除效率。亦即,第二实施例存储单元中的存储元件500还具有一辅助电极502。以下仅介绍辅助电极502,存储元件的其他结构不再赘述。

101.辅助电极502位于栅极结构380与第二掺杂区域340之间的间隙壁330上方。亦即,辅助电极502位于较宽间隙壁330的上方。再者,介电层(dielectric layer)504位于辅助电极502与间隙壁330之间,介电层504可为电阻保护氧化层(resistance protection oxide layer,简称rpo层)。另外,为了简化绘图,图5a中并未绘示介电层504。

102.请参照图5c,其所绘示为第二实施例存储单元中的存储元件进行各种动作时的偏压示意图。相较于图3g,其差异仅在于增加辅助电压va。以下仅说明辅助电压va,其他的偏压则不再赘述。

103.如图5c所示,当存储元件500为p沟道晶体管时,辅助电极502接收辅助电压va。在编程动作时,辅助电压va可控制电子注入氮化硅层334。另外,在抹除动作时,辅助电压va可控制空穴注入氮化硅层334,或者控制电子退出氮化硅层334。

104.如图5c所示,针对p沟道晶体管的存储元件500,利用bbhe效应来进行编程动作(pgm)时,辅助电压va为+3v。利用che效应来进行编程动作(pgm)时,辅助电压va为-3v。利用chh效应来进行抹除动作(ers)时,辅助电压va为-3v。利用fn隧穿效应来进行抹除动作(ers)时,辅助电压va为-6v。利用bbhh效应来进行抹除动作(ers)时,辅助电压va为-3v。进行读取动作时,辅助电压va为-1v。

105.基本上,上述存储单元中,存储元件500的各种动作所提供的偏压仅是本发明的范例而已,并非用来限制本发明。在此领域的技术人员可以修改各种动作的偏压,并对存储元件500进行编程动作、抹除动作与读取动作。

106.另外,上述本发明第二实施例的存储元件为p沟道晶体管(p-channel transistor)。在此领域的技术人员也可以根据第二实施例来修改成第一变化型存储元件。

spacer),其包括:氧化硅层672、氮化硅层674与氧化硅层676。

116.在选择晶体管的制造过程中会增加一轻掺杂漏极(lightly doped drain,简称ldd)工艺,使得第一掺杂区620与第三掺杂区650各自包括一延伸部622与652,且延伸部622与652位于间隙壁670下方。其中,延伸部662与652为轻掺杂漏极区(ldd region)。

117.因此,在选择晶体管中,阱区(well region)610表面下方具有第一掺杂区620与第三掺杂区650,金属电极652接触于第三掺杂区650。栅极结构形成于阱区610表面上方,第一掺杂区620与第三掺杂区650之间。栅极结构接触于阱区610上表面。间隙壁670围绕于栅极结构的侧壁(side wall),并接触于阱区表面。再者,阱区610表面下方第一掺杂区620与第二掺杂区650之间为第四沟道694。

118.根据本发明的第三实施例,提供适当的偏压开启选择晶体管后,即可对存储元件进行编程动作、抹除动作与读取动作。再者,由于选择晶体管的间隙壁670下方并未存在任何沟道,因此于编程动作时不会有任何载流子注入选择晶体管的间隙壁670。

119.相同地,本发明第三实施例的存储单元中的存储元件与选择晶体管可以同为p沟道晶体管(p-channel transistor),或者同为n沟道晶体管(n-channel transistor)。

120.当然,本发明还可以修改第三实施例中的存储元件。例如,修改栅极结构,使得存储元件具有如图4c所示的l型栅极结构,或者如图4d所示的具有延伸至相邻存储元件的栅极结构。当然,也可以如图4e所示,修改存储元件的沟道宽度。

121.请参照图7a与图7b,其所绘示为本发明第四实施例非挥发性存储器的存储单元俯视图与a-b方向的剖视图。第四实施例的存储单元包括一选择晶体管与一存储元件,此存储单元是在第三实施例存储单元的基础上再设计一辅助电极(assisted electrode)702用以加强存储元件的编程与抹除效率。以下仅介绍辅助电极702,存储单元的其他结构不再赘述。另外,为了简化绘图,图7a中并未绘示介电层704。

122.辅助电极702位于存储元件的栅极结构与第二掺杂区域640之间的间隙壁630上方。亦即,辅助电极702位于较宽间隙壁630的上方。再者,介电层(dielectric layer)704位于辅助电极702与间隙壁630之间,介电层704可为电阻保护氧化层(resistance protection oxide layer,简称rpo层)。

123.根据本发明的第四实施例,提供适当的偏压开启选择晶体管后,即可对存储元件进行编程动作、抹除动作与读取动作。再者,由于选择晶体管的间隙壁670下方并未存在任何沟道,因此于编程动作时不会有任何载流子注入选择晶体管的间隙壁670。

124.相同地,本发明第四实施例的存储单元中的存储元件与选择晶体管可以同为p沟道晶体管(p-channel transistor),或者同为n沟道晶体管(n-channel transistor)。

125.当然,本发明还可以修改第四实施例中的存储元件。例如,修改栅极结构,使得存储元件具有如图4c所示的l型栅极结构,或者如图4d所示的具有延伸至相邻存储元件的栅极结构。当然,也可以如图4e所示,修改存储元件的沟道宽度。另外,辅助电极702也可以与控制栅极层684互相接触。或者,辅助电极702也可以接触于间隙壁630。

126.综上所述,本发明提出一种非挥发性存储器的存储单元。存储单元中的存储元件为一晶体管,且存储元件具有不对称的间隙壁。在存储元件中,较宽间隙壁的下方具有较长的沟道。当存储元件进行编程动作时,将有更多的载流子(carrier)经由较长沟道注入间隙壁的电荷抓取层。因此,本发明的存储单元可更有效率的进行编程动作,并缩短编程动作的

时间。

127.再者,本发明存储元件具有特殊形状的栅极结构,栅极结构的侧壁有多个面,而设计栅极结构至少有侧壁的两个表面相邻于第二沟道,用以形成较宽的间隙壁。

128.综上所述,虽然结合以优选实施例公开了本发明,然而其并非用以限定本发明。本发明所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,可作各种的更动与润饰。因此,本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1