芯腔局部厚金封装外壳、封装器件及制备方法与流程

1.本发明属于陶瓷封装技术领域,具体涉及一种芯腔局部厚金封装外壳、具有芯片和无源器件的封装器件及芯腔局部厚金封装外壳的制备方法。

背景技术:

2.常规的电源sip(超紧凑型系统级封装)产品,内部集成多个芯片及无源器件,例如电容、电阻及电感等。芯片粘接区、电阻、电容及电感的焊盘、芯片键合区域均在同一个平面上,芯片及电阻、电容、电感采用胶粘方式与陶瓷件对应部位焊盘进行连接,焊接需要金层厚度控制在1.3um~5.7um。但是,随着电流及功耗越来越大,特别是在一些特殊应用领域,需要高可靠、高等级的电源类sip产品。

3.为实现高可靠性能要求,芯片需要采用金丝键合,金丝键合需要陶瓷件相应部位键合指金层厚度1.3um~5.7um。电阻、电容及电感为减小接触电阻,增加可靠性,需要采用焊料焊接的方式与陶瓷件对应焊盘连接,焊接需要金层厚度控制在0.03um~0.5um。常规理解,芯片键合部位的镀金层为厚金区,无源器件部位的镀金层为薄金区,薄厚金需要设计在不同的腔体才能实现高可靠性要求,但是大部分陶瓷件由于内部器件布局受限,常规的镀覆及加工方式无法实现同一个陶瓷件内部既有薄金又有厚金。

技术实现要素:

4.本发明实施例提供一种芯腔局部厚金封装外壳、封装器件及制备方法,通过在芯腔底部设置高低不平的平面,为芯片和无源器件提供适配的安装平面,实现封装器件的高可靠性能。

5.第一方面,本发明实施例提供一种芯腔局部厚金封装外壳,包括:具有芯腔的陶瓷件,所述芯腔的底部划分为至少一个芯片安装区和至少一个无源器件安装区;所述芯片安装区设有下沉腔,所述下沉腔的底部与所述无源器件安装区处于不同的水平面;其中,所述下沉腔内的为厚金区,所述无源器件安装区为薄金区;所述下沉腔的底部设有第一镀金层,所述无源器件安装区设有第二镀金层,所述第一镀金层的厚度大于所述第二镀金层的厚度。

6.结合第一方面,在一种可能的实现方式中,所述下沉腔的底部与所述无源器件安装区之间的最小高度差为0.3mm。

7.结合第一方面,在一种可能的实现方式中,所述第一镀金层的顶面与所述第二镀金层的顶面处于不同的水平面。

8.结合第一方面,在一种可能的实现方式中,当所述的下沉腔的数量为多个时,所述下沉腔根据对应的芯片,具有不同的形状。

9.结合第一方面,在一种可能的实现方式中,各所述下沉腔的底面处于相同的水平面。

10.结合第一方面,在一种可能的实现方式中,各所述下沉腔内的第一镀金层处于相

同的水平面。

11.结合第一方面,在一种可能的实现方式中,所述第一镀金层的厚度为1.3um~5.7um。

12.结合第一方面,在一种可能的实现方式中,所述第二镀金层的厚度为0.03um~0.5um。

13.第二方面,本发明实施例还提供了一种芯腔局部厚金封装器件,包括所述的芯腔局部厚金封装外壳,所述芯片安装区设有芯片,所述芯片通过键合丝与所述第一镀金层键合,所述无源器件安装区设有无源器件。

14.第三方面,本发明实施例还提供了一种芯腔局部厚金封装外壳的制备方法,基于所述的芯腔局部厚金封装外壳,所述制备方法包括如下步骤:

15.在所述陶瓷件的芯腔底部,根据预设位置,划分芯片安装区和无源器件安装区;

16.在所述芯片安装区,对应芯片键合点的外侧设置下沉腔,使所述芯腔底部形成高低不同的平面;

17.利用阻焊胶遮盖所述无源器件安装区;

18.在未遮盖的下沉腔内镀金;

19.除去所述无源器件安装区的阻焊胶;

20.再在所述芯腔的底部整体镀金。

21.本发明提供的芯腔局部厚金封装外壳、封装器件及制备方法,与现有技术相比,有益效果在于:本发明采取了将厚金部位的键合指在陶瓷件垂直方向下沉,使其低于薄金部位,从而实现了同一陶瓷件内部不同区域不同镀层厚度的效果,满足低温焊料烧结和金丝键合的使用需求,并满足电流及功耗逐渐增大的电源类sip产品高可靠性能的要求,适应一些特殊应用领域的使用需求。

附图说明

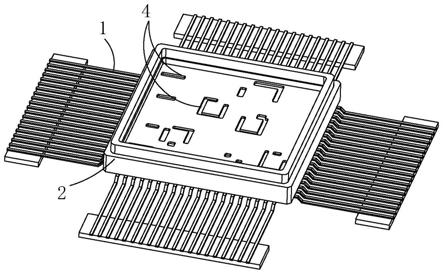

22.图1为本发明实施例提供的芯腔局部厚金封装外壳的结构示意图;

23.图2为本发明实施例提供的芯腔局部厚金封装器件的结构示意图;

24.附图标记说明:

25.1、引脚;2、陶瓷件;3、电容;4、下沉腔;5、芯片;6、键合丝;7、电感;8、无源器件安装区;9、芯腔。

具体实施方式

26.为了使本发明所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

27.请一并参阅图1及图2,现对本发明提供的芯腔局部厚金封装外壳进行说明。所述芯腔局部厚金封装外壳,包括:具有芯腔9的陶瓷件2,芯腔9的底部划分为至少一个芯片安装区和至少一个无源器件安装区8;芯片安装区设有下沉腔4,下沉腔4的底部与无源器件安装区8处于不同的水平面;其中,下沉腔4内的为厚金区,无源器件安装区8为薄金区;下沉腔4的底部设有第一镀金层,无源器件安装区8设有第二镀金层,第一镀金层的厚度大于第二

镀金层的厚度。

28.本实施例提供的芯腔局部厚金封装外壳,与现有技术相比,本发明采取了将厚金部位的键合指在陶瓷件2垂直方向下沉,使其低于薄金部位,从而实现了同一陶瓷件2内部不同区域不同镀层厚度的效果,满足低温焊料烧结和金丝键合的使用需求,并满足电流及功耗逐渐增大的电源类sip产品高可靠性能的要求,适应一些航天航空等特殊应用领域的使用需求。

29.本实施例中,芯片安装区的键合腔作为厚金区,也即第一镀金层,无源器件安装区作为薄金区,也即第二镀金层,芯片通过键合丝6键合在第一镀金层上,实现芯片的可靠性连接。无源器件焊接在第二镀金层,减小接触电阻,提高可靠性。

30.芯腔局部厚金封装外壳主要由陶瓷件、封口环、引线、绝缘瓷条(必要时)及热沉(必要时)组成,陶瓷件材料为90%的氧化铝,采用多层氧化铝陶瓷钨金属化高温共烧工艺制作,封口环材料为铁镍钴合金,引线材料为铁镍合金,热沉材料为钨铜、钼铜及cpc等合金,陶瓷件与封口环、引线及热沉采用银铜焊料焊接。

31.本实施例提供的陶瓷件可具有多个用于容纳芯片或无源器件的多边形腔体;可具有2层到100层的布线结构。封装外壳的封装形式及引线引出形式不限,可以采用cqfp、csop、clcc、cpga、cdip、clga等封装形式。

32.在一些实施例中,设有电感安装区、电容安装区,芯片安装区设置多个。各无源器件安装区8处于同一水平面。

33.在一些实施例中,作为本实施例提供的芯腔局部厚金封装外壳的一种改进的实施方式,参见图1,下沉腔4的底部与无源器件安装区8之间的最小垂直高度差为0.3mm,为芯片安装区与无源器件安装区8的镀金层的厚度不同提供结构条件。

34.作为一种改进的实施方式,参见图1,第一镀金层的顶面与第二镀金层的顶面处于不同的水平面(镀金层在图中未示出)。下沉腔4与芯腔9原底部镀金后,下沉腔4部位仍为下沉结构,芯腔9的底部仍然凹凸不平。以达到同一陶瓷件2内部不同区域不同镀层厚度、不同平面的效果。

35.作为上述特征陶瓷件2的一种变形实施方式,参见图2,当下沉腔4的数量为多个时,下沉腔4根据对应的芯片,具有不同的形状。在一个陶瓷件2内可以设置不同功能的芯片,不同功能的芯片由于键合点的不同,需要对应的设置不同形状的下沉腔4,以便于芯片与镀金层键合。下沉腔4的形状,如一字型、l型、半合围型等。

36.作为上述特征陶瓷件2的一种变形实施方式,参见图1,当设有多个下沉腔4时,各下沉腔4的底面处于相同的水平面。以便于加工、制作和键合。

37.如图1、图2所示,在各下沉腔4的底面处于相同的水平面的基础上,各下沉腔4内的第一镀金层处于相同的水平面。

38.作为上述特征陶瓷件2的一种变形实施方式,第一镀金层的厚度为1.3um~5.7um,以满足芯片高可靠性键合金层厚度的需求。

39.作为上述特征陶瓷件2的一种变形实施方式,第二镀金层的厚度为0.03um~0.5um,以满足电阻、电感7及电容3等无源器件减小接触电阻,且高可靠性要求。

40.基于同一发明构思,参见图1,本技术实施例还提供一种芯腔局部厚金封装器件,包括芯腔局部厚金封装外壳,芯片安装区设有芯片5,芯片5通过键合丝6与第一镀金层键

合,无源器件安装区8设有无源器件。芯片键合部位的镀金层为厚金区,无源器件部位的镀金层为薄金区,薄厚金在同一个芯腔9内设计,实现高可靠性要求。其中,在陶瓷件2的底部四周设有引脚1,陶瓷件2的侧壁外侧设有台阶,便于封装盖板的连接。

41.本实施例提供的封装器件,具有如下的优势:

42.(1)小型化,该类外壳将多个具有不同功能的芯片、阻容及塑封器件其他器件封装在一个气密的壳体内,代替原来单个的封装体,有效实现了封装小型化。

43.(2)优异的电性能,采用焊接方式减小了芯片、电阻、电容及电感的焊接接触电阻。两外由于该类外壳将多个裸芯片封装在一个壳体内,相对于普通陶瓷外壳产品,能最大限度优化系统布线,缩短互连线,故对高频高速下电路的信号噪声和延迟等能显著降低。

44.(3)高集成度,该类外壳具有一个或多个腔体,内部可安装多个芯片和多种无源元件,满足用户高集成度封装要求。

45.(4)高可靠性,由于内部的多个芯片、电容、电阻及电感与管壳对应部位焊盘均采用焊料焊接的方式进行连接,焊接方式相对于胶粘而言,在后续的使用过程中,不会发生老化衰减,更不会释放气体,对封装体内部的气氛造成影响。因此采用本发明后可有效提升器件的可靠性。特别是在一些高等级、大电流及功耗的电源类sip产品中。

46.基于同一发明构思,本技术实施例还提供了一种芯腔局部厚金封装外壳的制备方法,基于所述的芯腔局部厚金封装外壳,所述制备方法包括如下步骤:

47.步骤一,在陶瓷件2的芯腔9底部,根据预设位置,划分芯片安装区和无源器件安装区8;

48.步骤二,在芯片安装区,对应芯片键合点的外侧设置下沉腔4,使芯腔9底部形成高低不同的平面;

49.步骤三,利用阻焊胶遮盖无源器件安装区8;

50.步骤四,在未遮盖的下沉腔4内镀金;

51.步骤五,去除无源器件安装区8的阻焊胶;

52.步骤六,再在芯腔9的底部整体镀金。

53.本发明通过结构设计,使厚金区域腔体下沉,实现具有与薄金区域垂直方向上最小0.30mm的高度差,即将原来在同一平面的键合区域与焊接区域分为两个平面,然后在镀金时先采用阻焊胶将薄金区域进行遮盖,将厚金区域金层镀覆至2um

±

1um时,再清洗除去阻焊胶,进行整体薄金镀覆。最终实现同一腔体内部不同区域不同镀层厚度的效果,满足低温焊料烧结和金丝键合的使用需求。如果不将厚金区域挖腔体下沉,则由于阻焊胶有一定的流动性,其会在涂覆过程中流散漫延,结果是可能会将厚金区域也进行覆盖,无法实现同一只陶瓷件内部不同的区域不同的镀金层厚度。

54.本实施例采用al2o3、aln、玻璃瓷等多层共烧技术,具体流程为:外壳经流延、热切后,冲腔和冲孔、孔金属化后,经印刷、定位、层压、热切成当个生瓷件,再通过烧结、钎焊、后形成单个的陶瓷组装件,然后将封装外壳腔体内部薄金区域用阻焊胶遮盖起来,进行厚金区域镀覆,当厚金区域金层镀覆至要求厚度时,将管壳内部涂覆的光刻胶进行清洗,然后进行薄金区域的镀覆,最后完成管壳所有区域的镀层加工。

55.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1