半导体结构及提供单元阵列的方法与流程

1.本发明涉及一种单元阵列(cell array),更具体地,涉及一种由具有混合单元高度的多个单元形成的单元阵列。

背景技术:

2.集成电路(integrated circuit,ic)已经变得越来越重要。使用ic的应用被数百万人使用。这些应用包括手机、智能手机、平板计算机、膝上型计算机、笔记本计算机、pda、无线电子邮件终端、mp3音频和视频播放器以及便携式无线网络浏览器。集成电路越来越多地包括强大及高效地板上数据存储设备和逻辑电路以用于信号控制和处理。

3.随着集成电路的尺寸越来越小,集成电路变得更加紧凑。对于集成电路中经常被使用的各种单元,当这些单元高度差增大时,单元的布置(arrangement)变得更加复杂。因此,需要一种具有混合单元高度的单元阵列。

技术实现要素:

4.本发明提供半导体结构及提供单元阵列的方法,可提供一种具有混合单元高度的单元阵列。

5.本发明提供的一种半导体结构,包括:单元阵列,该单元阵列包括:布置在第一列中的多个第一单元,每一个该第一单元沿第一方向具有第一单元高度并且被配置为执行第一功能;布置在与该第一列邻接的第二列中的多个第二单元,每一个该第二单元沿该第一方向具有第二单元高度并且被配置为执行第二功能;和布置在该第一列中的至少一个第三单元,该第三单元沿该第一方向具有第三单元高度并且被配置为执行不同于该第一功能和该第二功能的第三功能;其中每一个该第二单元耦合到相应的该第一单元并与相应的该第一单元接触,并且被配置为从相应的该第一单元接收至少一个信号并根据接收到的该信号提供输出信号,其中该第二单元高度大于该第一单元高度,并且该第一单元的数量等于该第二单元的数量,其中该第三单元高度与该第一单元高度成比例。

6.本发明提供的另一种半导体结构,包括:单元阵列,该单元阵列包括:布置在第一列中的多个第一单元,每一个该第一单元具有沿第一方向的第一单元高度并且被配置为执行第一功能;布置在与该第一列邻接的第二列中的多个第二单元,每一个该第二单元沿该第一方向具有第二单元高度并且被配置为执行第二功能;布置在该第一列中的至少一个第三单元,该第三单元沿第一方向具有第三单元高度并且被配置为执行不同于该第一功能的第三功能;和布置在该第二列中的至少一个第四单元,且该第四单元沿第一方向具有为该第二单元高度的一半的高度,并且被配置为执行不同于该第二功能的第四功能,其中每一个该第一单元耦合并接触相应的该第二单元,并且该第一单元被配置为根据输入信号向相应的第二单元提供至少一个信号,其中该第二单元高度大于该第一单元高度,并且该第一单元的数量等于该第二单元的数量,其中该第三单元高度与第一单元高度成比例。

7.本发明提供的一种提供单元阵列的方法,包括:获得多个第一单元的第一单元高

度及多个第二单元的第二单元高度,其中该第二单元高度大于该第一单元高度;根据该第一单元高度与该第二单元高度的最小公倍数获得该单元阵列的阵列高度;将该多个第二单元布置在该单元阵列的第一列中;将该多个第一单元布置在该单元阵列的第二列中,其中布置在该第二列中的该第一单元的数量等于布置在该第一列中的该第二单元的数量,并且每一个该第二单元耦接并接触相应的该第一单元;和在该单元阵列的该第二列中布置至少一个具有第三单元高度的第一附加单元,其中每一个该第一单元被配置为执行第一功能并且每一个该第二单元被配置为执行不同于该第一功能的第二功能,其中该第三单元高度与该第一单元高度成比例,其中每一个该第一单元包括互连结构,该互连结构被配置为耦接并接触相应的该第二单元。

附图说明

8.图1是图示集成电路(ic)的层次(hierarchical)设计过程的流程图。

9.图2是图示根据本发明的一些实施例的ic的第一单元和第二单元的简化图。

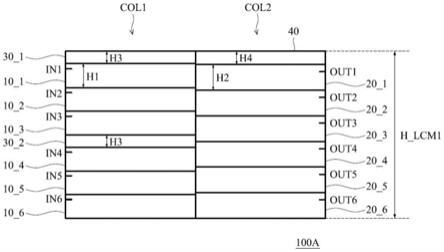

10.图3是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100a的简化图。

11.图4a是图示根据本发明的一些实施例的图3中的单元阵列100a的第一单元以及第二单元的简化图。

12.图4b根据本发明的一些实施例示出图4a中第一单元的器件单元和第二单元的器件单元的简化图。

13.图5是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100b的简化图。

14.图6是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100c的简化图。

15.图7是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100d的简化图。

16.图8是图示根据本发明的一些实施例的具有混合单元高度的单元阵列400a的简化图。

17.图9是根据本发明实施例的提供具有混合单元高度的单元阵列的方法的流程图。

18.图10示出了根据本发明实施例的计算器系统600。

具体实施方式

19.在说明书及权利要求书当中使用了某些词汇来指称特定的组件。本领域技术人员应可理解,硬件制造商可能会用不同的名词来称呼同一个组件。本说明书及权利要求书并不以名称的差异来作为区分组件的方式,而是以组件在功能上的差异来作为区分的准则。在通篇说明书及权利要求当中所提及的“包含”及“包括”为一开放式的用语,故应解释成“包含但不限定于”。“大体上”是指在可接受的误差范围内,本领域技术人员能够在一定误差范围内解决所述技术问题,基本达到所述技术效果。此外,“耦接”一词在此包含任何直接及间接的电性连接手段。因此,若文中描述一第一装置耦接于一第二装置,则代表该第一装置可直接电性连接于该第二装置,或通过其它装置或连接手段间接地电性连接至该第二装

置。以下所述为实施本发明的较佳方式,目的在于说明本发明的精神而非用以限定本发明的保护范围,本发明的保护范围当视权利要求书所界定者为准。

20.接下面的描述为本发明预期的最优实施例。这些描述用于阐述本发明的大致原则而不应用于限制本发明。本发明的保护范围应在参考本发明的权利要求书的基础上进行认定。

21.此外,为了便于描述,本文中可以使用空间相关术语,例如“下方”、“下面”、“下侧”、“之下”、“上方”、“上面”、“上侧”、“之上”等来描述一个元素或特征与图中所示的另一个元素或特征的关系。

22.图1是图示集成电路(ic)的层次(hierarchical)设计过程的流程图。在步骤s110中,获得用于描述由ic执行的功能的寄存器传输级(register-transfer level,rtl)代码。rtl代码可以指示一设计由诸如硬件描述语言(hdl)之类的语音描述硬件来执行。在步骤s120中,合成rtl码以产生包括ic的闸级(gate)(或单元(cell))的网络列表(netlist)。一般而言,ic包括多个区块(block),每个区块为ic提供重要的功能,例如特定的处理器(例如应用处理器、视频处理器、音频处理器或控制器)、内存(例如sram设备)等。此外,每个区块都有对应的rtl代码,因此合成每个区块的rtl代码以生成对应的包括该区块的多个闸级的网络列表。在合成rtl代码之前,执行rtl仿真(simulation)以检查rtl代码的功能正确性。此外,在获得网络列表中的区块的闸级之后,进行闸级层次(gate level)仿真以检查网络列表的功能正确性。在步骤s130中,根据网络列表中区块的闸级,执行摆放(placement)和绕线(routing)程序,以产生ic芯片区域内的整个区块布局(layout)。因此,根据摆放点,执行芯片摆放和绕线程序并获得最终布局。在一些实施例中,布局是整个芯片布局。在一些实施例中,布局是整个芯片布局中与ic的一些数字或模拟电路有关的一部分布局。在步骤s140中,执行分析程序并验证布局以检查布局是否违反各种约束或规则中的任一个。布局完成后,执行设计规则检查(design rule check,drc)、布局与原理图一致性检查(layoutversus schematic,lvs)和电气规则检查(electric rule check,erc)。drc是根据设计规则使用物理测量空间检查布局是否成功完成的过程,lvs是检查布局是否符合相应电路图的过程。另外,erc是检查设备和线/网(wires/nets)之间是否很好地电连接的过程。此外,通过提取和仿真寄生分量(例如寄生电容)来执行后仿真(post-simulation)以检查布局的功能完整性。如果布局没有违规,则根据布局制造(或实施)ic(步骤s150)。如果布局存在违规,则必须修改ic的布局以解决违规,直到不存在违规为止。

23.图2是图示根据本发明的一些实施例的ic的第一单元10和第二单元20的简化图,该第一单元10和第二单元20具有不同的单元高度。第一单元10在y方向上具有单元高度h1,第二单元20在y方向具有单元高度h2,且单元高度h2大于单元高度h1,即h2》h1。此外,第一单元10和第二单元20中的每一个包括多个晶体管。在一些实施例中,晶体管选自由平面晶体管(planar transistor)、鳍式场效应晶体管(finfet)、垂直闸级环绕(gateallaround,gaa)、水平闸级环绕、纳米线、纳米片或其组合组成的组。

24.如图2所示,第一单元10中的晶体管由沿y方向延伸的多个鳍片(fin)12形成,第二单元20中的晶体管由沿y方向延伸的多个鳍片22形成。在该实施例中,第一单元10中的鳍片12的鳍片宽度fw1等于第二单元20中的鳍片22的鳍片宽度fw2,即fw1=fw2。此外,鳍片12的鳍片间距fp1与鳍片22的鳍片间距fp2不同。例如,鳍片间距fp2大于鳍片间距fp1,即fp2》

fp1。

25.在一些实施例中,第一单元10中的鳍片12的鳍片宽度fwl不同于第二单元20中的鳍片22的鳍片宽度fw2。例如,宽度fwl小于宽度fw2(即,fw1《fw2)。在一些实施例中,鳍片12的鳍片间距fp1等于鳍片22的鳍片间距fp2。此外,第一单元10中的鳍片12的数量可以等于或不等于第二单元20中的鳍片22的数量。

26.图3是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100a的简化图。单元阵列100a包括布置(arrange)在第一列col1中的第一单元10_1至10_6和布置在与第一列col1邻接的(abutting)第二列col2中的第二单元20_1至20_6。如上所述,第一单元10_1至10_6的单元高度h1小于第二单元20_1至20_6的单元高度h2。此外,第一单元10_1至10_6的鳍片间距fp1不同于第二单元20_1至20_6的鳍片间距fp2。此外,第一单元10_1至10_6和第二单元20_1至20_6可以是数字单元或模拟单元。在一些实施例中,单元高度h1在约130nm至约410nm的范围内,单元高度h2在约280nm至约420nm的范围内。

27.在图3中,单元阵列100a具有阵列高度h_lcm1(例如,3.64μm),并且阵列高度h_lcm1根据单元高度h1和单元高度h2确定。在一些实施例中,阵列高度h_lcm1是单元高度h1和单元高度h2的最小公倍数(least common multiple,lcm)。例如,如果单元高度h1为260nm,单元高度h2为280nm,则阵列高度h_lcm1为260nm和280nm的lcm,即3.64μm。在一些实施例中,阵列高度h_lcm1是单元高度h1和单元高度h2的lcm的倍数。

28.在单元阵列100a中,第一单元10_1至10_6中的每一个是被配置为执行第一功能的核心设备。此外,第一单元10_1至10_6具有相同的电路配置。类似地,第二单元20_1至20_6中的每一个是被配置为执行第二功能的输入/输出(i/o)设备。此外,第二单元20_1至20_6具有相同的电路配置。

29.在单元阵列100a中,第一列coll中的每一个第一单元10对应第二列col2中的相应第二单元20,并且每一个第一单元10耦接至对应的第二单元20以对输入信号执行第一功能以及第二功能以提供输出信号。例如,第一单元10_1被配置为对输入信号in1执行第一功能以产生至少一个中间信号到第二单元20_1。响应于中间信号,第二单元20_1被配置为对中间信号执行第二功能以提供输出信号out1。因此,输出信号out1是根据输入信号in1并通过第一单元10_1与第二单元20_1之间的信号路径获得的。类似地,第一单元10_3被配置为对输入信号in3执行第一功能以产生至少一个中间信号到第二单元20_3。响应于中间信号,第二单元20_3被配置为对中间信号执行第二功能以提供输出信号out3。因此,输出信号out3是根据输入信号in3并通过第一单元10_3与第二单元20_3之间的信号路径获得的。具体而言,输出信号out1至out6是根据输入信号in1至in6并通过单元阵列100a中的不同信号路径获得的。

30.在单元阵列100a中,第二单元20_1至20_6中的每一个耦合到对应的第一单元10并与之接触。例如,第二单元20_1与第一单元10_1耦合并接触,第二单元20_2与第一单元10_2耦合并接触,第二单元20_3与第一单元10_3耦合并接触,以此类推。

31.在单元阵列100a中,阵列高度h_lcml仅够容纳六个第二单元20,不足以容纳七个第二单元20,因此具有单元高度h4的第四单元(即,附加单元)40被插入至第二列col2中。在这样的实施例中,第四单元40与第二单元20_1邻接。此外,单元高度h4是单元高度h2的一半。第四单元40被配置为执行不同于第一单元10的第一功能和第二单元20的第二功能的功

能。在一些实施例中,第四单元40是虚拟单元(dummy cell)或保护环单元(guardring cell)。在一些实施例中,第四单元40被配置为执行特定电路的特定功能,该特定电路与包括第一单元10_1至10_6和第二单元20_1至20_6的电路不同。

32.为了满足第二列col2中可以摆放的第二单元20的数量,在第一列coll中仅布置了六个第一单元10。因此,具有单元高度h3的第三单元(即,附加单元)30_1和30_2被插入到第一列col1中。此外,单元高度h3是单元高度h1的一半。在这样的实施例中,第三单元30_1与第一单元10_1(例如,列col1的顶部)邻接,并且第三单元30_2与第一单元10_3和10_4(例如,列col1的中间)邻接。第三单元30_1和30_2中的每一个被配置为执行与第一单元10的第一功能和第二单元20的第二功能不同的功能。在一些实施例中,每一个第三单元30是虚拟单元或保护环单元。在一些实施例中,第三单元30被配置为执行特定电路的特定功能,该特定电路与包括第一单元10_1至10_6和第二单元20_1至20_6的电路不同。

33.在单元阵列100a中,第三单元30_1和30_2用作第一列coll中的填充单元(filler cells),第四单元40用作第二列col2中的填充单元。因此,第一列col1和第二列col2中不存在间隙(gap)(即,空白空间),从而避免了由空白空间引起的drc违规。

34.图4a是图示根据本发明的一些实施例的图3中的单元阵列100a的第一单元10_5和10_6以及第二单元20_5和20_6的简化图。第一单元10_5和10_6中的每一个包括多个器件单元(device unit)15和绕线单元(routing unit)17。在每一个第一单元10中,器件单元15和绕线单元17具有单元高度h1并且布置在相同的行(row)中。此外,多个器件单元15可以具有相同或不同的电路配置以执行各种操作,并且同一行中的器件单元15被配置为执行第一单元10的第一功能。类似地,每一个第二单元20_5和20_6包括多个器件单元25。对于每一个第二单元20,器件单元25具有单元高度h2并且布置在同一行中。此外,多个器件单元25可以具有相同或不同的电路配置以执行各种操作,并且同一行中的器件单元25被配置为执行第二单元20的第二功能。

35.在图4a中,在每一个第一单元10中,器件单元15设置在器件范围210中,并且绕线单元17设置在的绕线范围220中。此外,器件单元25设置在每一个第二单元20中的器件范围230中。器件范围210与器件范围230通过绕线范围220分开(separate)。换言之,器件单元15通过绕线单元17与器件单元25分开。在一些实施例中,在绕线单元中不布置晶体管。

36.绕线单元17在x方向上具有单元宽度w1。器件单元15在x方向上具有单元宽度w2,单元宽度w2大于单元宽度w1,即w2>w1。器件单元25在x方向上具有单元宽度w3,单元宽度w3也大于单元宽度w1,即w3>w1。在一些实施例中,在同一行中但对应不同操作的器件单元15可以具有不同的单元宽度,在同一行中但对应不同操作的器件单元25可以具有不同的单元宽度。在一些实施例中,在同一行中且对应相同操作的器件单元15可以具有相同的单元宽度,在同一行中且对应相同操作的器件单元25可以具有相同的单元宽度。

37.在图4a中,第一单元10_5被配置为对输入信号in5执行第一功能以产生中间信号sa5和sb5给第二单元20_5。在接收到中间信号sa5和sb5之后,第二单元20_5被配置为对中间信号sa5和sb5执行第二功能以提供输出信号out5。因此,输出信号out5是根据输入信号in5并通过第一单元10_5与第二单元20_5之间的信号路径获得的,该信号路径由器件范围210、绕线范围220和器件范围230的互连结构(interconnect structure)形成。例如,中间信号sa5通过绕线单元17的互连结构251提供给第二单元20_5,而中间信号sb5通过绕线单

元17的互连结构252提供给第二单元20_5。

38.在第一单元10_5的器件单元15中,输入信号in5通过金属线271被接收,中间信号sa5和sb5分别通过金属线272和273提供给互连结构251和252。此外,输出信号out5通过第二单元20_5的器件单元25中的金属线274提供。在这样的实施例中,金属线271至274在第一金属层中形成。在一些实施例中,金属线271至274在不同的金属层中形成。在一些实施例中,第一单元10_5和第二单元20_5中的金属线具有不同的金属宽度。例如,第一单元10_5中的金属线271的金属宽度mw1小于第二单元20_5中的金属线274的金属宽度mw2。此外,互连结构251和252由第一金属层中的金属线、第一金属层上方的第二金属层中的金属线(例如281)以及第一金属层和第二金属层之间的通孔层中的对应的通孔(例如291)形成。需要说明的是,本实施例中互连结构251和252的配置仅作为示例,并不用于限制本发明。

39.类似地,第一单元10_6被配置为对输入信号in6执行第一功能以产生中间信号sa6和sb6给第二单元20_6。在接收到中间信号sa6和sb6之后,第二单元20_6被配置为对中间信号sa6和sb6执行第二功能以提供输出信号out6。因此,输出信号out6是根据输入信号in6并通过第一单元10_6与第二单元20_6之间的信号路径获得的,该信号路径由器件范围210、绕线范围220和器件范围230的互连结构形成。例如,中间信号sa6通过绕线单元17的互连结构253提供给第二单元20_6,而中间信号sb6通过绕线单元17的互连结构254提供给第二单元20_6。

40.由于单元高度h1不同于单元高度h2,第一单元10_5将不与第二单元20_5对齐,并且第一单元10_6将不与第二单元20_6对齐。因此,列col1中两个邻接的第一单元10的绕线单元17具有不同的互连结构。例如,如图4a所示,第一单元10_5中的绕线单元17的互连结构(例如,251和252)不同于第一单元10_6中的绕线单元17的互连结构(例如,253和254)。

41.图4b根据本发明的一些实施例示出图4a中第一单元10的器件单元15和第二单元20的器件单元25的简化图。

42.在第一单元10_5和10_6的器件范围210中,电源线310和320沿x方向延伸并且交替布置(arranged alternately)。电源线310和电源线320被配置为连接各种电源信号。例如,当电源电压(例如,vdd)被施加到电源线310上时,电源线320接地。相反,当电源电压(例如,vdd)被施加到电源线320上时,电源线310接地。

43.在第一单元10_6中,电源线310_1和310_2分别设置在第一单元10_6的下侧和上侧,并且电源线320_1设置在电源线310_1和310_2之间。此外,在第一单元10_5中,电源线310_2和310_3分别设置在第一单元10_5的下侧和上侧,并且电源线320_2设置在电源线310_2和310_3之间。在此实施例中,电源线310的间距等于电源线320的间距。例如,电源线310_1和310_2之间的距离等于单元高度h1,以及电源线320_1和320_2之间的距离也等于单元高度h1。此外,在第一单元10_6中,电源线310_1和电源线320_1之间的距离以及电源线320_1和电源线310_2之间的距离等于单元高度h1的一半,即单元高度h3。类似地,在第一单元10_5中,电源线310_2与电源线320_2之间的距离以及电源线320_2与电源线310_3之间的距离等于单元高度h1的一半。

44.在第二单元20_5和20_6的器件范围230中,电源线315和325沿x方向延伸并且交替布置。电源线315和电源线325用于连接各种电源信号。例如,当电源电压(例如,vdd)被施加到电源线315上时,电源线325接地。相反,当电源电压(例如,vdd)被施加到电源线325上时,

电源线315接地。

45.在第二单元20_6中,电源线315_1和315_2分别设置在第二单元20_6的下侧和上侧,并且电源线325_1设置在电源线315_1和315_2之间。此外,在第二单元20_5中,电源线315_2和315_3分别设置在第二单元20_6的下侧和上侧,并且电源线325_2设置在电源线315_2和315_3之间。在此实施例中,电源线315的间距等于电源线325的间距。例如,电源线315_1和315_2之间的距离等于单元高度h2,以及电源线325_1和325_2之间的距离也等于单元高度h2。此外,在第二单元20_6中,电源线315_1和电源线325_1之间的距离以及电源线325_1和电源线315_2之间的距离等于单元高度h2的一半,即单元高度h4。类似地,在第二单元20_5中,电源线315_2和电源线325_2之间的距离以及电源线325_2和电源线315_3之间的距离等于单元高度h2的一半。

46.在图4b中,电源线310和320以及电源线315和325在相同的金属层中形成。此外,电源线310和320以及电源线315和325在y方向上具有相同的宽度。在一些实施例中,电源线310和320的宽度不同于电源线315和325的宽度。

47.需要说明的是,电源线310和320以及电源线315和325的配置和布置仅作为示例,并不用于限制本发明。以第一单元10_5和10_6为例,在一些实施例中,多条电源线320设置在两条相邻的(adjacent)电源线310之间,或者多条电源线310设置在两条相邻的电源线320之间。在一些实施例中,电源线310与两条相邻的电源线320的距离不等。在一些实施例中,电源线310和320在不同的层中形成。例如,电源线310在第一金属层中形成,并且电源线320在第一金属层之上或之下的第二金属层中形成。此外,第一金属层的电源线310可以覆盖或不覆盖第二金属层的电源线320。

48.在每个器件单元15中,在底部电源线(例如,310_1)和中间电源线(例如,320_1)之间的有源区域(active region)350中形成多个晶体管,并且在中间电源线(例如,320_1)和顶部电源线(例如,310_2)之间的有源区域355中形成多个晶体管。在每个器件单元25中,在底部电源线(例如,315_1)和中间电源线(例如,325_1)之间的有源区域360中形成多个晶体管,并且在中间电源线(例如,325_1)和顶部电源线(例如,315_2)之间的有源区域365中形成多个晶体管。在一些实施例中,晶体管是finfet,并且器件范围230中的晶体管的鳍片宽度大于器件范围210中的晶体管的鳍片宽度。

49.在第一单元10_5和10_6中的每一个中,沿x方向上延伸的多条金属线330形成在器件单元15的晶体管上方。此外,在第二单元20_5和20_6的每一个中,沿x方向延伸的多条金属线340形成在器件单元25的晶体管上方。在图4b中,金属线330和340在同一金属层中形成。此外,器件范围210中的金属线330与器件范围230中的金属线340具有不同的金属宽度。例如,第一单元10_5中的金属线330的金属宽度mw3小于第二单元20_5中的金属线340的金属宽度mw4。此外,金属线330的线距(line pitch)mp1与金属线340的线距mp2不同。例如,线距mp1小于线距mp2,即mp1<mp2。

50.图5是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100b的简化图。单元阵列100b包括布置在第一列col1中的第一单元10_1至10_6和布置在与第一列col1邻接的第二列col2中的第二单元20_1至20_6。如上所述,第一单元10_1至10_6的单元高度h1小于第二单元20_1至20_6的单元高度h2。

51.单元阵列100b的阵列高度h_lcm1等于图3中的单元阵列100a的阵列高度h_lcm1。

与图3中的单元阵列100a比较,在图5的单元阵列100b中,具有单元高度h3的第三单元30_1和30_2布置在第一列col1的中间位置,并且具有单元高度h4的第四单元40布置在第二列col2的中间位置。因此,单元阵列100b的布局沿线a-aa具有对称配置。换言之,第一单元10_1和10_6的绕线单元17和器件单元15沿线a-aa镜像,第一单元10_2和10_5的绕线单元17和器件单元15沿线a-aa镜像,以及第一单元10_3和10_4的绕线单元17和器件单元15沿线a-aa镜像。类似地,第二单元20_1和20_6的器件单元25沿线a-aa镜像,第二单元20_2和20_5的器件单元25沿线a-aa镜像,第二单元20_3和20_4的器件单元25沿线a-aa镜像。

52.在一些实施例中,单根电源线310和单根电源线320分别设置在第三单元30_1和30_2中的每一个的下侧和上侧。此外,电源线310和320之间的距离等于单元高度h3,即单元高度h1的一半。类似地,单根电源线330和单根电源线340分别设置在第四单元40的下侧和上侧。此外,电源线330和340之间的距离等于单元高度h4,即单元高度h2的一半。

53.在图3的单元阵列100a中,由于第一单元10和第二单元20的非对称布置,第一单元10_1至10_6中的每一个中的绕线单元17具有各自的布局配置。与图3中的单元阵列100a相比,图5中的单元阵列100b具有沿线a-aa对称布置的第一单元10和第二单元20,因此降低了布局成本和工艺复杂度。

54.图6是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100c的简化图。单元阵列100c包括布置在第一列col1中的第一单元10_1至10_6和布置在与第一列col1邻接的第二列col2中的第二单元20_1至20_6。如上所述,第一单元10_1至10_6的单元高度h1小于第二单元20_1至20_6的单元高度h2。

55.在图6中,单元阵列100c的配置类似于图5中的单元阵列100b的配置。图6中的单元阵列100c和图5中的单元阵列100b之间的差异是图5中具有单元高度h3的第三单元30_1和30_2被图6中具有单元高度h1的第五单元50替代。此外,单元阵列100c的布局沿线b-bb的具有对称配置。换言之,第一单元10_1和10_6沿线b-bb镜像,第一单元10_2和10_5沿线b-bb镜像,第一单元10_3和10_4沿线b-bb镜像。类似地,第二单元20_1和20_6沿线b-bb镜像,第二单元20_2和20_5沿线b-bb镜像,第二单元20_3和20_4沿线b-bb镜像。

56.第五单元50被配置为执行不同于第一单元10的第一功能和第二单元20的第二功能的功能。在一些实施例中,第五单元50是虚拟单元或保护环单元。在一些实施例中,第五单元50被配置为执行特定电路的特定功能,该特定电路与包括第一单元10_1至10_6和第二单元20_1至20_6的电路不同。

57.在一些实施例中,双电源线310设置在第五单元50的下侧和上侧,并且一条电源线320设置在双电源线310之间。此外,从每条电源线310到电源线320的距离等于单元高度h1的一半。

58.图7是图示根据本发明的一些实施例的具有混合单元高度的单元阵列100d的简化图。单元阵列100d包括布置在第一列col1中的第一单元10_1至10_6和布置在与第一列col1邻接的第二列col2中的第二单元20_1至20_6。如上所述,第一单元10_1至10_6的单元高度h1小于第二单元20_1至20_6的单元高度h2。

59.在图7中,单元阵列100d的配置类似于图5中的单元阵列100b的配置。图7中的单元阵列100d与图5中的单元阵列100b之间的差异是在图7中具有单元高度h3的第三单元30_1和30_2没有布置在第一列col1的中间位置。在第一列col1中,第三单元30_1被插入在第一

单元10_2和10_3之间,并且第三单元30_2被插入在第一单元10_4和10_5之间。类似地,单元阵列100d的布局沿着线c-cc具有对称配置。换言之,第一单元10_1和10_6沿线c-cc镜像,第一单元10_2和10_5沿线c-cc镜像,并且第一单元10_3和10_4沿线c-cc镜像。类似地,第二单元20_1和20_6沿线c-cc镜像,第二单元20_2和20_5沿线c-cc镜像,并且第二单元20_3和20_4沿线c-cc镜像。

60.在一些实施例中,第三单元30_1被插入在第一列coll的第一单元10_1和10_2之间,并且第三单元30_2被插入在第一列coll的第一单元10_5和10_6之间。

61.图8是图示根据本发明的一些实施例的具有混合单元高度的单元阵列400a的简化图。单元阵列400a包括布置在第一列col1中的第六单元60和布置在与第一列col1邻接的第二列col2中的第七单元70。在这样的实施例中,第六单元60的单元高度h5小于第七单元70的单元高度h6。此外,第六单元60中的鳍片的鳍片间距不同于第七单元70中的鳍片的鳍片间距。例如,第六单元60的鳍片间距小于第七单元70的鳍片间距。在一些实施例中,单元高度h5在约130nm至约410nm的范围内,并且单元高度h6在约280nm至约420nm的范围内。

62.在图8中,单元阵列400a具有阵列高度h_lcm2,并且阵列高度h_lcm2根据单元高度h5和单元高度h6确定。在一些实施例中,阵列高度h_lcm2是单元高度h5和单元高度h6的最小公倍数(lcm)。在一些实施例中,阵列高度h_lcm2是单元高度h5和单元高度h6的lcm的倍数。

63.在单元阵列400a中,第六单元60是被配置为执行第三功能的核心器件。此外,多个第六单元60具有相同的电路配置。类似地,第七单元70是被配置为执行第四功能的输入/输出(i/o)设备。此外,多个第七单元70具有相同的电路配置。

64.第一列coll中的每一个第六单元60对应于第二列col2中的相应第七单元70,并且每一个第六单元60耦合到并接触相应的第七单元70,以对输入信号执行第三功能和第四功能来提供输出信号。因此,根据输入信号in1至in13并通过单元阵列400a中的不同信号路径获得输出信号out1至out13。

65.在单元阵列400a中,阵列高度h_lcm2可以容纳13个第七单元70,因此不需要额外的单元被插入到第二列col2中。为了满足第二列col2中可摆放的第七单元70的数量,在第一列col1中仅布置了13个第六单元60。因此,具有单元高度h5的第八单元80被插入到第一列col1中。

66.在单元阵列400a中,第八单元80用作第一列coll中的填充单元。因此,第一列col1中不存在间隙(即,空白空间),从而避免由空白空间引起的drc违规。

67.图9是根据本发明实施例的提供具有混合单元高度的单元阵列的方法的流程图。图9由能够操作电子设计自动化(electronic design automation,eda)工具的计算器执行。

68.首先,在步骤s510中,获得待布置在单元阵列中的单元的不同单元高度,例如第一单元10的单元高度h1、第二单元20的单元高度h2、第六单元60的单元高度h5和第七单元70的单元高度h6。

69.在步骤s520中,根据在步骤s510中获得的单元高度,获得单元阵列的阵列高度。在一些实施例中,阵列高度是不同单元高度的最小公倍数(lcm)。在一些实施例中,阵列高度h_lcm1是不同单元高度的lcm的倍数。在一些实施例中,阵列高度h_lcm1是不同单元高度的

lcm的整数倍。

70.在步骤s530中,将具有最大单元高度的单元布置在单元阵列的第一列中。布置在第一列中的单元具有相同的电路配置,并且这些单元是被配置为执行相同功能的相同器件。因此,确定了要布置在第一列中的具有最大单元高度的单元的数量。如果阵列高度不是最大的单元高度的整数倍,则在第一列中插入一个或多个附加单元以避免由空白空间引起的drc违规。如上所述,附加单元可以是虚拟单元、保护环单元或其他电路的单元。

71.在步骤s540中,将具有其他单元高度的单元布置在单元阵列的其他列中。例如,具有第一单元高度的单元被布置在单元阵列的第二列中,并且第一单元高度不同于最大单元高度。需要说明的是,第二列中具有第一单元高度的单元的数量等于第一列中具有最大单元高度的单元的数量。在一些实施例中,具有第二单元高度的单元被布置在单元阵列的第三列中,并且第二单元高度不同于最大单元高度和第一单元高度。此外,第二列中具有第二单元高度的单元的数量等于第一列中具有最大单元高度的单元的数量。如上所述,如果单元阵列的阵列高度不是第一单元高度或第二单元高度的整数倍,则在相应的列中插入一个或多个附加单元以避免由空白空间引起的drc违规。

72.在步骤s550中,提供不同列中的单元之间的互连结构。在一些实施例中,互连结构被布置在单元高度小于最大单元高度的特定单元中并且被布置在同一列中。如上所述,互连结构布置在特定单元的绕线单元17中。

73.在互连结构和具有不同单元高度的单元被摆放在单元阵列中之后,单元阵列的布局可以具有非对称配置(例如,图3的单元阵列100a和图8的单元阵列400a)或对称配置(例如,图5的单元阵列100b、图6的单元阵列100c和图7的单元阵列100d)。

74.图10示出了根据本发明实施例的计算器系统600。计算器系统600包括计算器610、显示设备620和用户输入接口630,其中计算器610包括处理器640、内存(memory)650和存储设备(storage)660。计算器610耦合到显示设备620和用户输入接口630,其中计算器610能够操作电子设计自动化(eda)工具。此外,计算器610能够从用户输入接口630接收输入指令或信息(例如时序约束、rtl代码或存储器设备的接口信息)并显示仿真结果、ic和区块或电路在显示设备620上的布局。在一些实施例中,显示设备620是计算器610的gui。此外,显示设备620和用户输入接口630可以在计算器610中实现。用户输入接口630可能是键盘、鼠标等。在计算器610中,存储设备660可以存储操作系统(operating system,os)、应用程序、信息(例如电路功能信息和电源相关信息)和包括应用程序所需的输入数据和/或应用程序生成的输出数据。计算器610的处理器640可以执行本公开中隐含或明确描述的任何方法的一个或多个操作(自动地执行或使用用户输入执行)。例如,在一操作过程中,处理器640可以将存储设备660的应用程序加载到内存650中,然后用户可以使用这些应用程序来创建、查看和/或编辑电路设计(例如,具有混合单元高度的单元阵列)的摆放、平面图和物理布局。

75.本公开中描述的数据结构和代码可以部分或全部存储在计算器可读存储介质和/或硬件模块和/或硬件装置上。计算器可读存储介质可以是但不限于易失性存储器、非易失性存储器、磁和光存储设备,例如磁盘驱动器、磁带、cd(光盘)、dvd(数字通用盘或数字视频盘)或其他现在已知或以后开发的能够存储代码和/或数据的介质。本公开中描述的硬件模块或设备的示例包括但不限于专用集成电路(asic)、现场可编程闸级阵列(fpga)、专用或共享处理器和/或其他已知或后来发展的硬件模块或设备。

76.本发明虽以较佳实施例揭露如上,然其并非用以限定本发明的范围,任何本领域技术人员,在不脱离本发明的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当视权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1