一种高性能SGTMOSFET器件的制作方法

一种高性能sgt mosfet器件

技术领域

1.本实用新型涉及mosfet器件领域,特别涉及一种高性能sgt mosfet 器件。

背景技术:

2.采用sgt技术制造的mosfet属于前沿的功率器件技术,主要应用于中低压(《250v)领域,具有极低的导通损耗和极低的开关损耗,并能在较小的封装中提供更高的电流密度,从而更节省空间更高效率,在快充,电动车,汽车电子,5g,光伏,物联网和智能电子化等中高端应用中越来越广泛。

3.参照现有公开号为cn111211174a的中国专利,其公开了一种 sgt-mosfet半导体器件,属于半导体技术领域,其结构包括n型重掺杂半导体衬底和位于n型重掺杂半导体衬底上表面的n型半导体漂移区;n型半导体漂移区的上表面设有p型区,p型区上表面设有n型重掺杂半导体源区, n型重掺杂半导体源区设有贯穿p型区并延伸至n型半导体漂移区中的控制栅;n型重掺杂半导体源区设有贯穿p型区并延伸至n型半导体漂移区中的屏蔽栅;控制栅设置有至少一个,屏蔽栅设置有至少两个,控制栅设置在相临的两个屏蔽栅之间。

4.上述的这种sgt-mosfet半导体器件利用分裂栅和浮置p阱技术极大改善了沟槽栅器件性能。本发明的浮置p阱配置、以及n-漂移区的配置具有优化的电场分布结构,提高器件耐压,降低导通电阻,从而降低驱动损耗和开关损耗。但是上述的这种sgt-mosfet半导体器件依旧存在着一些缺点,如:现有技术尽管采用高密度trench结构,并且尽量降低衬底反扩最大可能优化rsp到28mohm.mm2左右,但该rsp仍然偏高。

技术实现要素:

5.针对背景技术中提到的问题,本实用新型的目的是提供一种高性能sgtmosfet器件,以解决背景技术中提到的问题。

6.本实用新型的上述技术目的是通过以下技术方案得以实现的:

7.一种高性能sgt mosfet器件,包括mosfet器件体,所述mosfet器件体虚拟分割成cell区域和ring区域,所述mosfet器件体的底部设有n

+

衬底层,所述n

+

衬底层的上部设有epi1层,所述epi1层的上部设有epi2层,所述epi2层的顶部注入形成p型杂质b+层,所述p型杂质b+层的顶部设有介质淀积层,所述介质淀积层的顶部设有金属层,所述cell区域和所述 ring区域分别开设有沟槽,所述沟槽的底部穿透所述epi1层处于所述epi2 层的内部,所述沟槽的内壁设有淀积氧化层,所述cell区域内的所述沟槽的内部设有第一多晶硅和第四多晶硅,所述ring区域内的所述沟槽内分别设有第二多晶硅和第三多晶硅。

8.通过采用上述技术方案,本实用新型涉及60v mosfet器件采用分离栅结构,采用高浓红磷掺杂衬底,其中生长掺磷的双层外延,跟普通trench 的双层外延完全相反,底部epi1层掺杂浓度较淡,顶部epi2层掺杂浓度较浓,沟槽底部穿透顶部外延epi2层,反向偏置时顶部epi2层可以被深沟槽的电荷平衡效果完全耗尽,底部epi1层掺杂较淡,利于扩展耗尽宽度,提升耐压。并且工艺上所有涉及氧化,推阱的步骤都采用低温工艺,这样可以尽可

能降低衬底反扩,从而获得更好的rsp,达到13.8mohm.mm2,相比普通trench工艺rsp性能提升50%,实际流片数据显示rsp性能优于现有同类产品,分离栅特殊的结构又使开关性能提升50%以上。

9.较佳的,所述n

+

衬底层采用的是红磷衬底,所述epi1层和所述epi2 层的电阻率分别是0.2-0.4ohm.cm和0.1-0.2ohm.cm,所述epi1层和所述 epi2层的厚度均是2-4um。

10.通过采用上述技术方案,epi1层和epi2层的厚度能够有效的防止击穿,且电阻率可以实现一定的导电的效果。

11.较佳的,所述淀积氧化层采用的是热生长薄氧化层500a和cvd淀积氧化层2000a-2500a,所述淀积氧化层上再进行hdp淀积氧化层,且隔离氧化层厚度为2500-3000a。

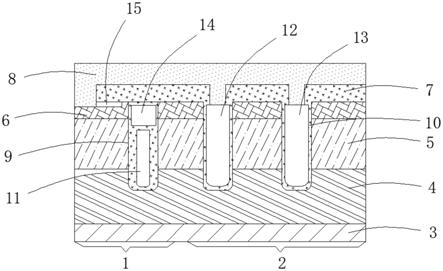

12.通过采用上述技术方案,氧化层能够有效的抑制高密度的电子和空穴陷阱,这些陷阱能引入快界面态,造成偏压与温度应力下的电荷不稳定性,并且减少硅与二氧化硅的热膨胀系数不同而产生了拉伸应力使硅附近氧化层产生较多的缺陷,减少氧化层局部生长速率不均匀引起的小斑点和氧化层针孔。

13.较佳的,所述p型杂质b+层在所述epi2层的顶部浇注推进形成p阱区,所述p阱区的结深为0.7um。

14.通过采用上述技术方案,p型杂质b+层通过注入推进形成,实现不同的导电效率。

15.较佳的,所述p型杂质b+层的顶部一端设有n

+

光刻槽,所述n

+

光刻槽内注入有n

+

层。

16.通过采用上述技术方案,n

+

层的设定能够有效的实现负光阻处理。

17.较佳的,所述金属层包覆在所述介质淀积层上,所述金属层的一端镶嵌在所述介质淀积层和所述p型杂质b+层的端部。

18.通过采用上述技术方案,能够形成有效的线路连接,便于mosfet管的使用。

19.较佳的,所述第一多晶硅用于引出源极,所述第四多晶硅用于引出栅极,所述金属层背面金属化引出漏极。

20.通过采用上述技术方案,可以形成有效的外接电路接头,便于进行线路的连接使用。

21.综上所述,本实用新型主要具有以下有益效果:

22.本实用新型涉及60v mosfet器件采用分离栅结构,采用高浓红磷掺杂衬底,其中生长掺磷的双层外延,跟普通trench的双层外延完全相反,底部epi1层掺杂浓度较淡,顶部epi2层掺杂浓度较浓,沟槽底部穿透顶部外延epi2层,反向偏置时顶部epi2层可以被深沟槽的电荷平衡效果完全耗尽,底部epi1层掺杂较淡,利于扩展耗尽宽度,提升耐压。并且工艺上所有涉及氧化,推阱的步骤都采用低温工艺,这样可以尽可能降低衬底反扩,从而获得更好的rsp,达到13.8mohm.mm2,相比普通trench工艺rsp 性能提升50%,实际流片数据显示rsp性能优于现有同类产品,分离栅特殊的结构又使开关性能提升50%以上。

附图说明

23.图1是本实用新型的现有技术的结构示意图;

24.图2是本实用新型的结构示意图。

25.附图标记:1、cell区域;2、ring区域;3、n

+

衬底层;4、epi1层;5、epi2层;6、p型杂质b+层;7、介质淀积层;8、金属层;9、沟槽;10、淀积氧化层;11、第一多晶硅;12、第二多晶硅;

13、第三多晶硅;14、第四多晶硅;15、n

+

层。

具体实施方式

26.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

27.实施例

28.参考图1-2,一种高性能sgt mosfet器件,包括mosfet器件体,mosfet 器件体虚拟分割成cell区域1和ring区域2,mosfet器件体的底部设有 n

+

衬底层3,n

+

衬底层3的上部设有epi1层4,epi1层4的上部设有epi2 层5,epi2层5的顶部注入形成p型杂质b+层6,p型杂质b+层6的顶部设有介质淀积层7,介质淀积层7的顶部设有金属层8,cell区域1和ring 区域2分别开设有沟槽9,沟槽9的底部穿透epi1层4处于epi2层5的内部,沟槽9的内壁设有淀积氧化层10,cell区域1内的沟槽9的内部设有第一多晶硅11和第四多晶硅14,ring区域2内的沟槽9内分别设有第二多晶硅12和第三多晶硅13。

29.通过采用上述技术方案,本实用新型涉及60v mosfet器件采用分离栅结构,采用高浓红磷掺杂衬底,其中生长掺磷的双层外延,跟普通trench 的双层外延完全相反,底部epi1层4掺杂浓度较淡,顶部epi2层5掺杂浓度较浓,沟槽底部穿透顶部外延epi2层5,反向偏置时顶部epi2层5可以被深沟槽9的电荷平衡效果完全耗尽,底部epi1层4掺杂较淡,利于扩展耗尽宽度,提升耐压。并且工艺上所有涉及氧化,推阱的步骤都采用低温工艺,这样可以尽可能降低衬底反扩,从而获得更好的rsp,达到 13.8mohm.mm2,相比普通trench工艺rsp性能提升50%,实际流片数据显示rsp性能优于现有同类产品,分离栅特殊的结构又使开关性能提升50%以上。

30.本实施例中,优选的,n

+

衬底层3采用的是红磷衬底,epi1层4和epi2 层5的电阻率分别是0.2-0.4ohm.cm和0.1-0.2ohm.cm,epi1层4和epi2 层5的厚度均是2-4um。效果为,epi1层4和epi2层5的厚度能够有效的防止击穿,且电阻率可以实现一定的导电的效果,epi1层4的掺杂浓度比 epi2层5的掺杂浓度低。效果为,底部epi1层4掺杂浓度较淡,顶部epi2 层5掺杂浓度较浓,沟槽底部穿透顶部外延epi2层5,反向偏置时顶部epi2 层5可以被深沟槽的电荷平衡效果完全耗尽,底部epi1层4掺杂较淡,利于扩展耗尽宽度,提升耐压。

31.本实施例中,优选的,淀积氧化层采用的是热生长薄氧化层500a和cvd 淀积氧化层2000a-2500a,淀积氧化层上再进行hdp淀积氧化层,且隔离氧化层厚度为2500-3000a。效果为,氧化层能够有效的抑制高密度的电子和空穴陷阱,这些陷阱能引入快界面态,造成偏压与温度应力下的电荷不稳定性,并且减少硅与二氧化硅的热膨胀系数不同而产生了拉伸应力使硅附近氧化层产生较多的缺陷,减少氧化层局部生长速率不均匀引起的小斑点和氧化层针孔。

32.本实施例中,优选的,p型杂质b+层6在epi2层5的顶部浇注推进形成p阱区,p阱区的结深为0.7um。效果为,p型杂质b+层6通过注入推进形成,实现不同的导电效率。

33.本实施例中,优选的,p型杂质b+层6的顶部一端设有n

+

光刻槽,n

+

光刻槽内注入有n

+

层15。效果为,n

+

层15的设定能够有效的实现负光阻处理。

34.本实施例中,优选的,金属层8包覆在介质淀积层7上,金属层8的一端镶嵌在介质淀积层7和p型杂质b+层6的端部。效果为,能够形成有效的线路连接,便于mosfet管的使用。

35.本实施例中,优选的,第一多晶硅11用于引出源极,第四多晶硅14 用于引出栅极,金属层8背面金属化引出漏极。效果为,可以形成有效的外接电路接头,便于进行线路的连接使用。

36.制备方法:

37.第一步:在n

+

衬底层3上面生长一层n外延层,既是epi1层4,并且在epi1层4上生成epi2层5,比如采用40vn红磷衬底,则epi1层4、epi2 层5的电阻率分别是0.2-0.4ohm.cm和0.1-0.2ohm.cm,外延厚度都是 2-4um;

38.第二步:在epi2层5上进行淀积二氧化硅,厚度为0.6um作为掩蔽层,光刻并刻蚀掩蔽层以形成图案;

39.第三步:以二氧化硅掩蔽层为阻挡,刻蚀硅形成沟槽9,底部epi1层4掺杂浓度较淡,顶部epi2层5掺杂浓度较浓,沟槽9底部穿透顶部外延 epi2层5,反向偏置时顶部epi2层5可以被深沟槽9的电荷平衡效果完全耗尽,底部epi1层4掺杂较淡,利于扩展耗尽宽度,提升耐压;

40.第四步:在epi2层5的表面和沟槽9内形成热生长薄氧化层500a+cvd 淀积氧化层1000a-1500a;

41.第五步:淀积多晶硅,然后刻蚀多晶硅,在沟槽9底部形成多晶硅,在去除上部分的氧化层;

42.第五步:然后进行hdp淀积氧化层,cmp,然后回刻到隔离氧化层厚度为2500-3000a;

43.第六步:再进行栅氧化,多晶硅淀积,多晶硅回刻;

44.第七步:在epi2层5上注入p型杂质b+层6,并推进形成p型杂质b

+

陷区,且结深约0.7um;

45.第八步:然后在p型杂质b+层6的一端进行n+光刻,再将n+层15注入;

46.第九步:在p型杂质b+层6上进行介质淀积,形成介质淀积层7,再进行介质光刻,孔腐蚀;

47.第十步:然后在介质淀积层7上进行金属淀积层8的淀积,光刻,腐蚀,分别引出栅极,源极,背面减薄,背面硅腐蚀,背面金属化形成漏极。

48.尽管已经示出和描述了本实用新型的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本实用新型的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本实用新型的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1