一种基于绝缘层上硅衬底的二维材料/硅异质结阵列及其制备方法

1.本发明属于光电探测技术领域,涉及一种基于绝缘层上硅衬底的二维材料/硅异质结阵列及其制备方法。

背景技术:

2.光电探测技术在食品检测、物质识别、医药研究、生化检测、环境安防、无线通信等领域具有广泛的应用。制备大面积高质量单晶硅的工艺已经非常成熟,在可见光领域,硅的光电探测器已经应用在各个方面。然而在紫外、红外以及高速的场景下,仅仅依靠硅光电探测器难以满足需求。

3.石墨烯等二维材料的引入为纯硅基光电探测器提供了新的思路。新型的二维材料由于量子限域效应,具有优异独特的光学和电学特性,被认为是很有前景的光电探测材料,有可能被应用在下一代微纳电子器件。例如,石墨烯具有超高载流子迁移率、宽吸收谱;过渡金属硫化物有较强的光与物质相互作用。二维材料作为一种通过原子层间范德华力作用形成的层状材料已形成了一个极为丰富的材料体系,在光子学和光电子学领域具有重要应用潜力,特别是具备光谱范围可选和无晶格失配等突出优点。通过二维材料和硅形成异质结,有望实现响应度、带宽及灵敏度等综合高性能的光电探测器。此外,二维材料器件在制备均一性、可靠性、阵列化、规模化等方面都面临着挑战,仍需在阵列、集成和高可靠制备技术工艺等方面取得突破。

技术实现要素:

4.本发明的目的在于针对现有技术的不足,提供一种基于绝缘层上硅衬底的二维材料/硅异质结阵列及其制备方法。该发明提供了一种二维材料/硅异质结的光电器件结构,解决了二维材料/硅器件在制作阵列上的问题,为二维材料与硅的大规模集成提供了方案。

5.本发明的目的是通过以下技术方案来实现的:

6.本发明提供一种基于绝缘层上硅衬底的二维材料/硅异质结阵列,包括组成阵列的若干异质结单元,所述异质结单元是二维材料与硅的垂直异质结;所述阵列是异质结单元的面阵阵列;

7.所述阵列包括绝缘层上硅衬底,所述绝缘层上硅衬底是将顶硅图形化成若干顶硅条带的soi衬底,所述衬底上还设有绝缘层,所述绝缘层中刻有硅窗口阵列和硅接触孔;

8.所述硅窗口阵列的每个硅窗口外围设有二维材料接触电极,每一行/列的硅窗口外围的二维材料接触电极相互连接并引出作为该行/列的公共顶电极;所述二维材料接触电极上覆盖二维材料,所述二维材料通过所述硅窗口与所述顶硅条带接触,形成异质结;所述阵列中的每一列/行异质结共用同一条顶硅条带,每条顶硅条带均通过所述硅接触孔连接有硅接触电极,每一行/列异质结分别做在不同的顶硅条带上。

9.进一步地,所述二维材料为单层或多层的二维薄膜材料,包括单层、多层石墨烯、

宏观组装石墨烯、薄层石墨、单层或多层过渡金属硫化物、单层或多层过渡金属硒化物、单层或多层黑磷。

10.进一步地,所述二维材料与硅接触形成的异质结区是以阵列结构排布的感光区。

11.进一步地,包含二维材料接触电极的顶电极和所述硅接触电极的材质为导电金属。

12.本发明提供一种基于绝缘层上硅衬底的二维材料/硅异质结阵列的制备方法,包括如下步骤:

13.(1)在绝缘层上硅衬底的顶硅表面使用光刻技术制作条状阵列掩膜,刻蚀未被掩膜保护的顶硅以制作顶硅形状是若干顶硅条带的绝缘层上硅衬底;

14.(2)将图形化后的绝缘层上硅衬底的表面进行热氧化处理,之后沉积绝缘材料,以隔离相邻顶硅条带和填充相邻硅条带之间的间隙;

15.(3)通过cmp法平坦化,将沉积的绝缘材料上表面磨平、抛光,形成绝缘层3;

16.(4)在抛光的绝缘层上表面光刻硅的接触孔图形,并用湿法或干法刻蚀绝缘层形成硅接触孔,并在硅接触孔区域进行离子注入以便硅接触电极和硅之间形成良好的欧姆接触;

17.(5)用光刻技术在绝缘层上表面制作电极图形掩膜,沉积电极材料,之后放在去胶溶液中剥离,形成顶电极和硅接触电极;也可以先沉积电极材料,再利用光刻和刻蚀技术图形化电极形成顶电极和硅接触电极;

18.(6)在绝缘层上表面光刻出硅窗口阵列的图形,用湿法或干法刻蚀绝缘层形成硅窗口阵列;

19.(7)转移二维材料到硅窗口阵列上;

20.(8)使用光刻和刻蚀技术图形化二维材料,留下异质结阵列所在区域的二维材料。

21.本发明还提供一种基于绝缘层上硅衬底的二维材料/硅异质结阵列的制备方法,包括如下步骤:

22.(1)在绝缘层上硅衬底的顶硅表面使用光刻技术制作条状阵列掩膜,刻蚀未被掩膜保护的顶硅以制作顶硅形状是若干顶硅条带的绝缘层上硅衬底;

23.(2)在图形化后的绝缘层上硅衬底的上表面上制作硅窗口阵列掩膜和硅接触孔掩膜,之后沉积绝缘材料并放在去胶溶液中进行剥离,留下带有硅窗口和硅接触孔的绝缘层;也可以先沉积绝缘材料,再利用光刻和刻蚀技术图形化绝缘层形成带有硅窗口和硅接触孔的绝缘层;

24.(3)用光刻技术在绝缘层上表面制作电极图形掩膜,沉积电极材料,之后放在去胶溶液中剥离,形成顶电极和硅接触电极;也可以先采沉积电极材料,再利用光刻和刻蚀技术图形化电极形成顶电极和硅接触电极;

25.(4)转移二维材料到硅窗口阵列上;

26.(5)使用光刻和刻蚀技术图形化二维材料,留下异质结阵列所在区域的二维材料。

27.本发明提出的基于绝缘层上硅衬底的二维材料/硅异质结阵列的工作原理为:

28.(1)本发明中的二维材料/硅的垂直异质结,由于二维材料和硅的功函数不同,电子会从费米能级高的材料的流向费米能级低的材料,从而形成势垒和耗尽区。在二维材料接触电极和硅接触电极之间施加一定的反向偏压,二维材料/硅异质结处于反向截止状态,

只有很低的暗电流;对于可见光的入射,当入射光入射到异质结器件上时,入射光进入到半导体衬底的耗尽区,将在耗尽区内激发电子空穴对,电子和空穴在电场的作用下分离,分别被二维材料和硅衬底收集,形成很大的光电流;对于紫外光的探测,使用宽禁带的二维材料和硅形成异质结,依靠二维材料的禁带宽度较大,实现对紫外光的吸收;对于红外光的探测,利用内光电发射效应(ipe)和光热电子发射效应(pti)等效应使电子越过势垒实现光响应。通过检测光电流大小来反映入射光的信息。

29.(2)本发明的二维材料/硅异质结阵列中,每一列/行异质结共用同一条顶硅条带,每一行/列异质结的二维材料接触电极共用同一条顶电极布线。使用选通读出的方式依次读出各异质结单元的信息,即依次对每一行/列的顶电极施加负偏压,在每一列/行的硅接触电极处进行并行电流读出。电流读出方式一般采用正端接地的电阻或电容反馈的运放实现电压的输出。

30.本发明的有益效果如下:

31.1.本发明通过二维材料与硅的垂直异质结拓宽吸收波段、增强光吸收。光生载流子会在电场的作用下分离,被二维材料有效地收集;二维材料是一个很丰富的材料体系,可以选用合适的二维材料,实现各个波段的光探测。

32.2.本发明提供的二维材料/硅异质结阵列,结构和制备工艺简单,可以进行大规模制备,成品率高,并兼容cmos工艺。

33.3.本发明提供的二维材料/硅异质结阵列,不同列/行异质结单元的衬底分离,不同列/行异质结单元之间天然隔离,有效避免像素之间的串扰。通过行/列选通的方式,可以无误地读出阵列中每个异质结单元的信息。

附图说明

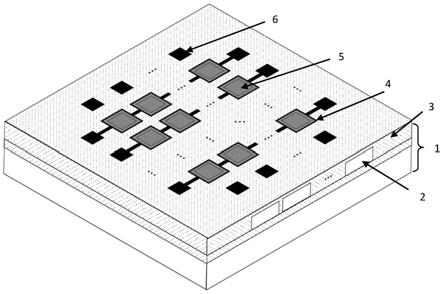

34.图1是本发明实施例提供的一种基于绝缘层上硅衬底的二维材料/硅异质结阵列的立体结构图;

35.图2是本发明实施例提供的一种基于绝缘层上硅衬底的二维材料/硅异质结阵列的剖视图;

36.图中:绝缘层上硅衬底1、顶硅条带2、绝缘层3、二维材料接触电极4、二维材料5、硅接触电极6、硅窗口阵列7。

具体实施方式

37.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行完整的描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.实施例1

39.如图1、2所示,本发明实施例提供的基于绝缘层上硅衬底的二维材料/硅异质结阵列,包括组成阵列的若干异质结器件,所述异质结阵列是在图形化的顶硅条带2上沉积一层绝缘层3并抛光,并在每个顶硅条带上的绝缘层3上刻蚀出硅接触孔并离子注入,之后制作包含二维材料接触电极4的顶电极和硅接触电极6,最后在二维材料接触电极4中间刻蚀出

硅窗口,转移二维材料5并图形化。本实施例中绝缘层上硅衬底的顶硅为n型轻掺硅,电阻率为1~10ω

·

cm,厚度1.5μm

±

5%,绝缘层3采用二氧化硅,二维材料5采用单层石墨烯。

40.制备上述基于绝缘层上硅衬底的二维材料/硅异质结阵列的方法包括以下步骤:

41.(1)取用绝缘层上硅衬底,顶硅为n型轻掺硅,电阻率1~10ω

·

cm,厚度1.5μm

±

5%。

42.(2)在绝缘层上硅衬底的顶硅表面使用光刻技术制作条状阵列掩膜,利用感应耦合等离子干法刻蚀系统(icp)刻蚀未被掩膜保护的顶硅以制作顶硅条带。

43.(3)之后进行表面热氧化处理,利用等离子增强化学气相淀积系统(pecvd)沉积二氧化硅绝缘层,以隔离相邻硅条带和填充相邻硅条带之间的间隙。利用化学机械抛光(cmp)的方法将填充的二氧化硅绝缘层磨平抛光。

44.(4)在抛光的绝缘层上表面使用光刻技术制作硅的接触孔图案,并用湿法或干法刻蚀绝缘层形成硅的接触孔,利用离子注入技术对接触孔区域的顶硅进行重掺杂。

45.(5)在二氧化硅绝缘层表面使用光刻技术制作掩膜,利用磁控溅射技术生长10nm钛和60nm金作为电极,之后在去胶溶液中剥离后形成顶电极和硅接触电极。

46.(6)光刻硅窗口阵列图样,使用缓冲氧化物刻蚀溶液(boe)刻蚀二氧化硅绝缘层;其中,所述缓冲氧化物刻蚀溶液由hf、nh4f和水组成,hf:nh4f:h2o=30ml:60g:100ml(hf浓度为48%)。

47.(7)将硅窗口阵列上方覆盖单层石墨烯薄膜;转移石墨烯使用湿法转移:将单层石墨烯表面均匀旋涂一层聚甲基丙烯酸甲酯(pmma)薄膜,放入铜刻蚀溶液中浸泡约3h刻蚀去除铜箔,留下由pmma支撑的单层石墨烯薄膜;将pmma支撑的石墨烯薄膜用去离子水清洗后转移并覆盖到硅窗口阵列;最后用丙酮和异丙醇浸泡样品去除pmma;其中,所述同刻蚀溶液由cuso4、hcl和水组成,cuso4:hcl:h2o=10g:45ml:50ml。

48.(8)使用光刻技术将光刻胶覆盖所需单层石墨烯图形的区域。再通过氧等离子体反应离子刻蚀技术(oxygen plasma)刻蚀掉多余石墨烯,其功率和刻蚀时间分别为60瓦,2分钟。刻蚀完成后,用丙酮和异丙醇清洗去除残余光刻胶。

49.(9)对器件进行快速退火处理,退火温度为400摄氏度,时间为5分钟。

50.实施例2

51.如图1、2所示,本发明实施例提供的基于绝缘层上硅衬底的二维材料/硅异质结阵列,包括组成阵列的若干异质结器件,所述异质结器件是制作在图形化的顶硅2上沉积一层绝缘层3,并在绝缘层3上制作包含二维材料接触电极4的顶电极,最后在二维材料接触电极4中间刻蚀出硅窗口,转移二维材料5并图形化。本实施例中绝缘层上硅衬底的顶硅为n型轻掺硅,电阻率为1~10ω

·

cm,绝缘层3采用二氧化硅,二维材料5采用单层石墨烯。

52.制备上述基于绝缘层上硅衬底的二维材料/硅异质结阵列的方法包括以下步骤:

53.(1)取用绝缘层上硅衬底,顶硅为n型轻掺硅,电阻率1~10ω

·

cm,厚度1.5μm

±

5%。

54.(2)在绝缘层上硅衬底的顶硅表面使用光刻技术制作条状阵列掩膜,利用感应耦合等离子干法刻蚀系统(icp)刻蚀未被掩膜保护的顶硅以制作顶硅条带。

55.(3)在图形化后的绝缘层上硅衬底1的上表面上制作硅窗口阵列掩膜和硅接触孔掩膜,之后溅射200纳米二氧化硅作为绝缘层材料并放在去胶溶液中进行剥离,留下带有硅

窗口和硅接触孔的绝缘层;

56.(4)在二氧化硅绝缘层表面使用光刻技术制作掩膜,利用磁控溅射技术生长10nm钛和60nm金作为电极,之后在去胶溶液中剥离后形成顶电极和硅接触电极;

57.(5)将硅窗口阵列上方覆盖单层石墨烯薄膜;转移石墨烯使用湿法转移:将单层石墨烯表面均匀旋涂一层聚甲基丙烯酸甲酯(pmma)薄膜,放入铜刻蚀溶液中浸泡约3h刻蚀去除铜箔,留下由pmma支撑的单层石墨烯薄膜;将pmma支撑的石墨烯薄膜用去离子水清洗后转移并覆盖到硅窗口阵列;最后用丙酮和异丙醇浸泡样品去除pmma;其中,所述同刻蚀溶液由cuso4、hcl和水组成,cuso4:hcl:h2o=10g:45ml:50ml。

58.(6)使用光刻技术将光刻胶覆盖所需单层石墨烯图形的区域。再通过氧等离子体反应离子刻蚀技术(oxygen plasma)刻蚀掉多余石墨烯,其功率和刻蚀时间分别为60瓦,2分钟。刻蚀完成后,用丙酮和异丙醇清洗去除残余光刻胶。

59.(7)对器件进行快速退火处理,退火温度为400摄氏度,时间为5分钟。

60.该发明提供了一种使用二维材料/硅异质结的光电器件结构,提出一种制作大规模二维材料/硅异质结阵列的方法。本发明的异质结阵列中,每一列/行异质结共用同一条顶硅条带,每一行/列异质结的二维材料接触电极相互连接,组成一条该行/列的顶电极布线。通过选通的方式依次读出阵列中的各异质结单元的信息。本发明实现了二维材料/硅异质结器件的阵列制作,为二维材料和硅的大规模集成提供了方案。

61.以上所述仅是本发明的优选实施方式,虽然本发明已以较佳实施例披露如上,然而并非用以限定本发明。任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何的简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1