封装结构及其形成方法与流程

1.本公开的实施例是关于芯片封装(chip package)结构及其形成方法,特别是关于具有保护盖(protective lid)的芯片封装结构及其形成方法。

背景技术:

2.半导体集成电路(ic)产业经历快速增长。半导体制造制程的不断进步使得半导体装置具有更精细的部件及/或更高的集成程度(integration)。一般而言,功能密度(亦即,每个芯片面积的互连装置的数量)已经增加,同时部件尺寸(亦即,可以使用制造制程创造的最小组件)已经减少。这种按比例缩小的制程通常通过提高生产效率并降低相关成本来提供益处。

3.芯片封装不仅可以保护半导体装置免受环境污染物的影响,还可以为封装在其中的半导体装置提供连接接口(connection interface)。已开发出占用较少空间或较低高度的较小封装结构,来封装半导体装置。

4.已经开发了新的封装技术,以进一步提高半导体晶粒的密度及功能。这些相对较新的半导体晶粒的封装技术面临制造上的挑战。

技术实现要素:

5.一实施例是关于一种封装结构的形成方法。前述方法包括:设置芯片(chip)结构在基板上方;以及形成第一黏接元件(adhesive element)在基板上方。第一黏接元件具有第一电阻率(electrical resistivity)。前述方法亦包括:形成第二黏接元件在基板上方。第二黏接元件具有第二电阻率,且第二电阻率大于第一电阻率。前述方法还包括:通过(through)第一黏接元件及第二黏接元件附接(attching)保护盖到基板。保护盖围绕(surrounds)芯片结构且覆盖芯片结构的顶表面。

6.另一实施例是关于一种封装结构。前述封装结构包括基板以及在基板上方的芯片结构。前述封装结构亦包括通过第一黏接元件及第二黏接元件附接至基板的保护盖。第一黏接元件及第二黏接元件由不同材料制成。前述封装结构还包括通过第一黏接元件电性连接至保护盖的接地结构。

7.又另一实施例是关于一种封装结构。前述封装结构包括基板以及在基板上方的晶粒封装(die package)。前述封装结构亦包括通过第一黏接元件及第二黏接元件附接至基板的保护盖(protective lid)。保护盖覆盖晶粒封装。第一黏接元件具有第一电阻率,第二黏接元件具有第二电阻率。第二电阻率大于第一电阻率。

附图说明

8.根据以下的详细说明并配合所附图式阅读,能够最好的理解本公开的态样。应注意的是,根据本产业的标准作业,各种部件未必按照比例绘制,且仅用于说明性目的。事实上,可能任意的放大或缩小各种部件的尺寸,以做清楚的说明。

9.图1a至图1d是根据一些实施例,显示用于形成封装结构的一部分的制程的各种阶段的剖面图。

10.图2a至图2d是根据一些实施例,显示用于形成封装结构的一部分的制程的各种阶段的剖面图。

11.图3a至图3d是根据一些实施例,显示用于形成封装结构的一部分的制程的各种阶段的平面图。

12.图4是根据一些实施例,显示封装结构的一部分的平面图。

13.图5是根据一些实施例,显示封装结构的一部分的平面图。

14.图6是根据一些实施例,显示封装结构的一部分的平面图。

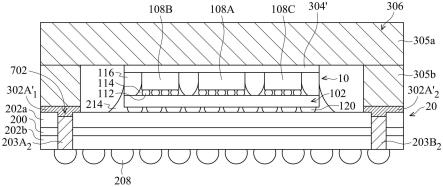

15.图7是根据一些实施例,显示封装结构的一部分的剖面图。

16.图8是根据一些实施例,显示封装结构的一部分的剖面图。

17.图9是根据一些实施例,显示封装结构的一部分的剖面图。

18.图10是根据一些实施例,显示封装结构的一部分的剖面图。

19.图11是根据一些实施例,显示封装结构的一部分的剖面图。

20.其中,附图标记说明如下:

21.10:晶粒封装

22.10’:第二晶粒封装

23.20:基板

24.100:载板

25.101:离型膜

26.102:重布线结构

27.108a,108b,108c:芯片结构

28.108d,108e,108f,108g:装置元件

29.112,120:导电连接件

30.114,214:底部填充结构

31.116:保护层

32.118:载带

33.200:核心部分

34.202a,202b:绝缘层

35.203a1,203a2,203a3,203a4,203b1,203b2,203b3,203b4,203c1,203c2,203c3,203c4,203d1,203d2,203d3,203d4,903a,903b:接地结构

36.208:接合结构

37.230t:顶表面

38.302a1,302a2,302a3,302a4:第一粘接胶

39.302a

’1,302a

’2,302a

’3,302a

’4,602a

’1,602a

’2,602a

’3,602b

’1,602b

’2,602b

’3,602c

’1,602c

’2,602c

’3,602d

’1,602d

’2,602d

’3:第一黏接元件

40.302b1,302b2,302b3,302b4:第二粘接胶

41.302b’,302b

’1,302b

’2,302b

’3,302b

’4:第二黏接元件

42.304:导热胶

43.304’:导热元件

44.305a:上板

45.305b:支撑结构

46.306:保护盖

47.702:突出部分

48.c1,c2,c3,c4:角隅部分

49.s1,s2,s3,s4:侧边部分

具体实施方式

50.以下的公开内容提供许多不同的实施例或范例,以实施所提供的发明标的的不同的部件。以下叙述组件及排列方式的特定范例,以简化本公开。当然,这些特定的范例仅为范例,而非用以限定。举例而言,若是本公开叙述了将第一部件形成于第二部件上方(over)或上(on),即表示其可能包括前述第一部件与前述第二部件是以直接接触(in direct contact)的方式来形成的实施例,且亦可能包括了将其他部件形成于介于前述第一部件与前述第二部件之间,而使前述第一部件与前述第二部件可能未直接接触的实施例。另外,在各种范例中,本公开可能重复使用元件符号及/或标记。这些重复是为了简化与清晰的目的,并非用以限定在此所讨论的各种实施例及/或配置之间有特定的关系。

51.再者,本文所用的空间相关用语,诸如「之下(beneath)」、「下方(below)」、「较低(lower)」、「之上(above)」、「较高(upper)」及其类似用语是用于简化描述,以说明如图所示的一元件/部件与另一(些)元件/部件的关系。除了如图所示的方位之外,这些空间相关用语旨在涵盖使用中或操作中的装置的不同方位。设备可以以其他方式来定向(旋转90度或以其他方像定向),且本文所用的空间相关用语同样可以相应地解释。

52.所属技术领域中具有通常知识者将理解说明书中的用语「实质上地(substantially)」,诸如「实质上平坦(substantially flat)」或「实质上共面(substantially coplanar)」或其类似用语。在一些实施例中,实质上可以移除形容词。在适用时,用语「实质上地(substantially)」亦可以包括具有「整个(entirely)」、「完全地(completely)」、「所有(all)」或其类似用语的实施例。在适用时,用语「实质上地(substantially)」亦可以涉及指定物的90%或更高,诸如95%或更高,尤其是99%或更高,且包括100%。此外,诸如「实质上平行(substantially parallel)」或「实质上垂直(substantially perpendicular)」的用语应解释为不排除与指定的排列的微小偏差,且举例而言,可以包括最多高达10度的偏差。用语「实质上地(substantially)」不排除「完全地(completely)」,例如:「实质上没有(substantially free)」y的组合物可以是完全没有y。

53.与特定的距离或尺寸结合的诸如「大约(about)」的用语将解释为不排除与特定距离或尺寸的微小偏差,且举例而言,可以包括最多高达10%的偏差。与数值x相关的用语「大约(about)」可表示x

±

5%或x

±

10%。

54.描述本公开的一些实施例。可以在描述这些实施例的阶段之前、期间及/或之后提供其他制程。为了不同的实施例,可以替换或消除一些所描述的阶段。可以向半导体装置结构及/或封装结构添加其他部件。对于不同的实施例,可以替换或消除以下描述的一些部件。虽然一些实施例讨论了以特定顺序执行的操作,但是这些操作可以以其他逻辑顺序来

执行。

55.本公开的实施例可以涉及诸如三维(3d)封装或3d-ic装置的封装结构。本公开的实施例形成封装结构,前述封装结构包括承载一或多个晶粒(dies)或封装(packages)的基板以及在晶粒或封装旁边(aside)的保护盖。保护盖也可以用作翘曲控制(warpage-control)元件及/或散热(heat dissipation)元件。在一些实施例中,保护盖通过一或多个黏接元件附接到基板。黏接元件中的一个或一些黏接元件是导电的(electrically conductive)。导电黏接元件可以在介于保护盖及接地结构之间形成电性连接。结果是,保护盖也可以用于减少或防止电磁干扰(electromagnetic interference,emi)至保护盖下方的一或多个晶粒或封装、及/或减少或防止来自保护盖下方的一或多个晶粒或封装的电磁干扰。另一种可能不导电的(electrically non-conductive)黏接元件可有助于降低封装结构破裂的风险。由于混用(hybrid)黏接元件,可同时减少或防止emi的问题及封装可靠性问题。大幅度地提高封装结构的性能及品质。

56.图1a至图1d是根据一些实施例的用于形成封装结构的一部分的制程的各个阶段的剖面图。如图1a所示,提供或接收载板(carrier substrate)100。在制造制程期间中,载板100用作支撑基板。在一些实施例中,载板100是临时支撑载体且将在之后移除。

57.载板100可以由介电材料、半导体材料、一或多个其他合适的材料或其组合制成,或者包括介电材料、半导体材料、一或多个其他合适的材料或其组合。在一些实施例中,载板100是介电基板,诸如玻璃晶圆(glass wafer)。在一些其他实施例中,载板100是半导体基板,诸如硅(silicon)晶圆。前述半导体基板可由硅、锗(germanium)、硅锗(silicon germanium)、一或多个其它合适的半导体材料或其组合制成,或者包括硅、锗、硅锗、一或多个其它合适的半导体材料或其组合。

58.如图1a所示,根据一些实施例,形成重布线(redistribution)结构102在载板100上方。重布线结构102可包括离型膜(release film)101、多个绝缘层及多个导电部件。可以之后一起移除离型膜101及载板100。

59.在一些实施例中,在重布线结构102中的绝缘层是含有聚合物的(polymer-containing)层。绝缘层可以由一或多个聚合物材料制成,或包括一或多个聚合物材料。聚合物材料可以包括聚苯并恶唑(polybenzoxazole,pbo)、聚酰亚胺(polyimide,pi)、环氧类(epoxy-based)树脂、一或多个其它合适的聚合物材料或其组合。在一些实施例中,聚合物材料是感光性的。因此,可以使用光微影制程在绝缘层中形成具有所期望的图案的开口。这些开口可以用来容置(contain)一些导电部件。

60.重布线结构102中的导电部件可以包括导线、导电导孔(conductive via)及/或导电垫片(conductive pads)。导电部件可由铜(copper)、钴(cobalt)、锡(tin)、钛(titanium)、金(gold)、铂(platinum)、铝(aluminum)、钨(tungsten)、一或多种其他合适的材料或其组合来制成,或者可包括铜、钴、锡、钛、金、铂、铝、钨、一或多种其他合适的材料或其组合。导电部件可以使用电镀(electroplating)制程、无电镀(electroless plating)制程、一或多个其他适用的制程或其组合来形成。导电部件的形成可以进一步涉及一或多个蚀刻制程。

61.如上所述,在重布线结构102中的一些导电部件是导电导孔。在一些实施例中,导电导孔的上部比导电导孔的下部更宽。

62.如图1a所示,根据一些实施例,设置多个芯片结构(或含芯片(chip-containing)的结构)108a、108b及108c在重布线结构102上方。在一些实施例中,在设置芯片结构108a、108b及108c之前,对重布线结构102的导电路径进行测试操作,以确保重布线结构102的品质及可靠性。在一些实施例中,芯片结构108a、108b及108c可能是芯片封装(chip package)。

63.在一些实施例中,芯片结构108a、108b及108c通过导电连接件112接合到重布线结构102的导电垫片。在一些实施例中,芯片结构108a、108b及108c中的每一个包括导电柱(或导电垫片),且前述导电柱(或导电垫片)上形成有焊料元件(solder element)。亦可以形成其他焊料元件在重布线结构102的导电垫片上。拾取(picked up)芯片结构108a、108b及108c并放置到重布线结构102上。在一些实施例中,芯片结构108a、108b及108c的焊料元件及/或在重布线结构102的导电垫片上的焊料元件一起回流(reflowed)。结果是,经回流的焊料元件形成导电连接件112。

64.在一些实施例中,导电连接件112是由含锡的(tin-containing)焊料材料制成。含锡的焊料材料可还包括铜、银(sliver)、金、铝、铅(lead)、一或多个其他合适的材料或其组合。在一些其它实施例中,导电连接件112是无铅的(lead-free)。

65.芯片结构108a、108b及108c中的每一个可以是单一半导体晶粒(die)、集成电路上系统(system-on-integrated-chips,soic)及/或包括一或多个受到封装(encapsulated)或保护的半导体晶粒的封装。对于集成电路上系统,可以堆叠多个半导体晶粒并使多个半导体晶粒接合在一起,以在介于这些半导体晶粒之间形成电性连接。这些半导体晶粒可以通过混合接合(hybrid bonding)彼此接合,混合接合可以包括介电质-介电质接合(dielectric-to-dielectric bonding)以及金属-金属接合(metal-to-metal bonding)。

66.在一些实施例中,在芯片结构108a、108b及108c中的每一个中的半导体晶粒是包括多个功能的芯片上系统(system-on-chip,soc)。在一些实施例中,半导体晶粒的背侧(back side)朝向上(face upward),且半导体晶粒的前侧(front side)面向重布线结构102。在一些实施例中,一些半导体晶粒包括诸如高带宽存储器(high bandwidth memory,hbm)装置的存储器装置。

67.在一些其他实施例中,芯片结构108a、108b及108c是其中包括一或多个半导体晶粒的封装。在一些其他实施例中,芯片结构108a是soc晶粒,且芯片结构108b及108c包括存储器装置。

68.在一些实施例中,芯片结构108a~108c中的两个或更多个具有不同的功能。在一些实施例中,芯片结构108a~108c中一个或一些包括高频集成电路(high-frequency integrated circuits)、串化器(serializer)及/或反串化器(deserializer)(serdes)电路、低噪放大器(low-noise amplifier,lna)模块(modules)、低耗损滤波器(low-loss filter)模块、功率放大器(power amplifier,pa)模块、基带(baseband)模块、电源管理集成电路(power management integrated circuit,pmic)、存储器(memory)模块、微机电系统(micro-electromechanical system,mems)模块、纳米机电系统(nano-electromechanical systems,nems)模块、一或多个其他合适的电路或其组合。在某些情况下,在操作芯片结构108a、108b及/或108c的期间中,来自在芯片结构108a、108b及/或108c中的半导体晶粒及/或导电迹线(conductive trace)的高速信号可能会导致附近的其他装

置的电磁干扰(electromagnetic interference)。

69.如图1b中所示,根据一些实施例,形成底部填充(underfill)结构114以围绕及保护导电连接件112。底部填充结构114可以由聚合物材料制成,或者包括聚合物材料,前述聚合物材料诸如其中分散有填料(fillers)的环氧类树脂。填料可包括纤维(诸如二氧化硅(silica)纤维及/或含碳(carbon-containing)纤维)、粒子(诸如二氧化硅粒子及/或含碳粒子)或其组合。

70.然后,根据一些实施例,如图1b所示,形成保护层116在重布线结构102上方,以围绕并保护芯片结构108a、108b及108c。在一些实施例中,保护层116与重布线结构102直接接触。在一些实施例中,通过底部填充结构114,保护层116与在芯片结构108a、108b及108c下方的导电连接件112分离。

71.然而,本公开的实施例并不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其他实施例中,不形成底部填充结构114。在这些情况下,保护层116可以与在芯片结构108a、108b及108c下方的导电连接件112直接接触。

72.在一些实施例中,保护层116由绝缘材料制成,或者包括绝缘材料,前述绝缘材料诸如模塑(molding)材料。模塑材料可以包括聚合物材料,诸如其中分散有填料的环氧类树脂。填料可包括纤维(诸如二氧化硅纤维及/或含碳纤维)、粒子(诸如二氧化硅粒子及/或含碳粒子)或其组合。在一些实施例中,在保护层116中的填料的分布密度大于在底部填充结构114中的填料的分布密度。在一些实施例中,在保护层116中的填料的重量百分比大于在底部填充结构114中的填料的重量百分比。在保护层116及底部填充结构114中的填料的轮廓(profiles)、尺寸及/或材料可以彼此不同。

73.在一些实施例中,引入或注入模塑材料(例如,可流动的(flowable)模塑材料),以覆盖重布线结构102及芯片结构108a、108b及108c。在一些实施例中,然后使用热制程,以固化可流动的模塑材料,并将可流动的模塑材料转变成保护层116。在一些实施例中,对保护层116进行平坦化制程,以提高保护层116的平坦度。举例而言,平坦化制程可以包括研磨(grinding)制程、化学机械研磨(chemical mechanical polishing,cmp)制程、干式研磨(dry polishing)制程、一或多种其他适用的制程或其组合。在一些实施例中,在平坦化制程之后,暴露芯片结构108a、108b及108c的表面。在一些实施例中,保护层116的顶表面与芯片结构108a、108b及108c的表面实质上(substantially)齐平(level with)。

74.然后,根据一些实施例,将如图1b所示的结构翻转(flipped)为上下颠倒(upside down)并附接(attched)到载带(carrier tape)118上。然后,根据一些实施例,如图1c所示,移除载板100及离型膜101。结果是,暴露最初通过载板100覆盖的重布线结构102的表面。

75.然后,根据一些实施例,如图1c所示,形成导电连接件(或接合结构)120在重布线结构102上方。在一些实施例中,导电连接件120的材料与导电连接件112的材料相同或相似。导电连接件120的形成可涉及施加焊料材料及一或多种热回流制程。在一些实施例中,如图1c所示,导电连接件120中的每一个比导电连接件112中的每一个更大。

76.在一些实施例中,切割(sawing)制程用于切穿(cut through)如图1c所示的结构为多个单独的芯片封装。根据一些实施例,如图1d所示,在切割制程之后,从载带118拾取一个晶粒封装(或含芯片结构)10,并上下颠倒地翻转。晶粒封装10与其它元件整体化(intergrated),以形成更大的封装结构。包括芯片结构108a~108c的晶粒封装10也可称

为「芯片结构(chip structure)」或「含有芯片结构(chip-containing structure)」。

77.然而,本公开的实施例并不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其它实施例中,不执行切割制程,来使在图1c中的结构分离成多个较小的晶粒封装。整个封装结构可以直接整体化为更大的封装结构而不需要切割。

78.图2a至图2d是根据一些实施例的用于形成封装结构的一部分的制程的各个阶段的剖面图。图3a至图3d是根据一些实施例的用于形成封装结构的一部分的制程的各个阶段的平面图。

79.在一些实施例中,图3a显示如图2a所示的结构的俯视图。在一些实施例中,图2a显示沿着在图3a中的线段2a-2a截取的结构的剖面图。在一些实施例中,图3b显示如图2b所示的结构的俯视图。在一些实施例中,图2b显示沿着在图3b中的线段2b-2b截取的结构的剖面图。在一些实施例中,图3c显示如图2c所示的结构的俯视图。在一些实施例中,图2c显示沿着在图3c中的线段2c-2c截取的结构的剖面图。在一些实施例中,图3d显示如图2d所示的结构的俯视图。在一些实施例中,图2d显示沿着在图3d中的线段2d-2d截取的结构的剖面图。

80.如图2a及图3a所示,接收或提供基板20(诸如电路基板或封装基板)。在一些实施例中,基板20包括核心(core)部分200。基板20还可以包括多个绝缘层202a及202b、以及多个导电部件(图2a中未示出)。导电部件可用于发送(route)在介于基板20的相对侧之间的电信号。绝缘层202a及202b可以由一或多个聚合物材料制成,或者包括一或多个聚合物材料。导电部件可以由铜、铝、钴、钨、金、一或多个其他合适的材料或其组合制成,或者可包括铜、铝、钴、钨、金、一或多个其他合适的材料或其组合。

81.核心部分200可以包括有机材料,诸如可以容易地层压(laminated)的材料。在一些实施例中,核心部分200可以包括单面或双面覆铜层压板(single-sided or double-sided copper clad laminate)、环氧树脂(epoxy)、树脂(resin)、玻璃纤维(glass fiber)、模塑材料(molding compound)、塑胶(诸如:聚氯乙烯(polyvinylchloride,pvc)、丙烯腈(acrylonitrile)、丁二烯和苯乙烯(butadiene and styrene,abs)、聚丙烯(polypropylene,pp)、聚乙烯(polyethylene,pe)、聚苯乙烯(polystyrene,ps)、聚甲基丙烯酸甲酯(polymethyl methacrylate,pmma)、聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、聚碳酸酯(polycarbonates,pc)、聚苯硫醚(polyphenylene sulfide,pps)、一或多个其他合适的元件或其组合。

82.导电导孔可延伸穿过(extend through)核心部分200,以提供介于设置在核心部分200的任一侧(either side)上的元件之间的电性连接。在一些实施例中,基板20还包括接合结构208。在一些实施例中,接合结构208是焊料凸块(solder bumps)。接合结构208的材料及形成方法可以是与图1d所示的导电连接件120相同或相似。在一些实施例中,接合结构208是用于与诸如印刷电路板的另一元件接合。

83.可以对本公开的实施例进行各种变化及/或修改。在一些其他实施例中,基板20包括陶瓷材料、半导体材料、聚合物材料、一或多个其他合适的材料或其组合。

84.如图2a及图3a所示,根据一些实施例,形成多个接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4在基板20中。在一些实施例中,这些接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4穿透(penetrate through)绝缘层202a、核心部分200及绝缘层20202b,以与接合结构208中的一些电性接触。

85.因此,电性连接到接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4的接合结构208用作接地凸块(ground bumps)。在一些实施例中,接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4的顶表面与基板20的顶表面实质上齐平。

86.在一些实施例中,如图3a所示,对称地布置接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4。举例而言,当基板20旋转大约180度时,接地结构203a1~203a4可以取代接地结构203b1~203b4。当基板20旋转大约180度时,接地结构203c1~203c4可以取代接地结构203d1~203d4。接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4的对称布置可有助于提高后续设置的保护盖的emi保护能力,前述保护盖将在图2d及图3d中进行说明。

87.接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4可以由导电材料制成。导电材料可包括铜、铝、金、钴、钨、含锡焊料、一或多个其他合适的材料或其组合。接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4的形成可涉及一或多个蚀刻制程、一或多个沉积(或电镀)制程以及一或多个平坦化制程。

88.如图2b及图3b所示,接收或提供相同或相似于图1d所示的晶粒封装10的晶粒封装10。在一些实施例中,根据一些实施例,拾取晶粒封装10并放置在基板20上方。然后,如图2b所示,使晶粒封装10通过导电连接件(或接合结构)120接合到基板20。如图3b所示,晶粒封装10还可以包括其他装置元件108d~108g。装置元件108d~108g可以包括芯片结构、被动元件、或一或多个其它合适的元件。

89.在一些实施例中,设置晶粒封装10在基板20上方,使得基板20的导电垫片与接合结构120直接接触。在一些其他实施例中,在设置晶粒封装10在基板20上方之前,可以形成其他焊料元件在基板20的导电垫片上。之后,使用热回流(heat reflow)制程及/或热压(heat compression)制程,以使晶粒封装10接合到基板20。

90.然后,根据一些实施例,沿着晶粒封装10的一侧,分配底部填充材料到基板20上。底部填充材料可以由聚合物材料制成,或者可包括聚合物材料,前述聚合物材料诸如其中分散有填料的环氧类树脂。填料可以包括纤维(诸如二氧化硅纤维及/或含碳纤维)、粒子(诸如二氧化硅粒子及/或含碳粒子)或其组合。底部填充材料可吸入(drawn)到介于晶粒封装10及基板20之间的空间,以通过毛细作用力围绕接合结构120。在一些实施例中,热加热并固化底部填充材料,以形成底部填充结构214。结果是,如图2b所示,形成围绕接合结构120的底部填充结构214。在图3b中,为求简洁及清楚起见,未显示出底部填充结构214。

91.如图2c及图3c所示,根据一些实施例,分配或施加第一黏接胶302a1、302a2、302a3及302a4以及第二黏接胶302b1、302b2、302b3及302b4在基板20上。在一些实施例中,如图3c所示,分配第一黏接胶302a1、302a2、302a3及302a4在侧边部分s1、s2、s3及s4上方,其中接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4位于侧边部分s1、s2、s3及s4。第一黏接胶302a1、302a2、302a3及302a4覆盖接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4。在图3c中,经覆盖的接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4以虚线显示。

92.在一些实施例中,如图3c所示,分配基板20的第二黏接胶302b1、302b2、302b3及302b4在基板20的角隅部分c1、c2、c3及c4上。在一些实施例中,第一黏接胶302a1~302a4及第

二黏接胶302b1~302b4彼此分离。然而,本公开的实施例并不限于此。在一些其他实施例中,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4中的一些是彼此直接接触。

93.在一些实施例中,第一黏接胶302a1~302a4在第二黏接胶302b1~302b4之前分配。在一些其他实施例中,第一黏接胶302a1~302a4在第二黏接胶302b1~302b4之后分配。

94.在一些实施例中,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4的材料不同。

95.在一些实施例中,第一黏接胶302a1~302a4是导电黏接胶(electrically conductive glues),且第二黏接胶302b1~302b4是不导电胶(electrical non-conductive glues)。第一黏接胶302a1~302a4可具有第一电阻率(electrical resistivity),而第二黏接胶302b1~302b4可具有第二电阻率。第二电阻率大于第一电阻率。举例而言,第一电阻率可以是在从大约0.0001欧姆-公分(ohm-cm)至大约0.0004欧姆-公分的范围中。第二电阻率可以是在从大约10

14

欧姆-公分至大约10

16

欧姆-公分的范围中。

96.因为第一黏接胶302a1~302a4为导电胶,因此第一黏接胶302a1~302a4之后可用于形成导电黏接元件。导电黏接元件可以形成介于接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4以及后续设置的保护盖之间的电性连接,前述保护盖可由导电材料制成。由于电性连接,因此保护盖电性接地。结果是,保护盖也可以用于防止或减少传递到保护盖下方的芯片结构及/或来自保护盖下方的芯片结构的电磁干扰(emi)。因此,显著地提升封装结构的可靠性及性能。

97.在一些实施例中,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4包括聚合物材料,且前述聚合物材料中分散有填料。聚合物材料可以包括环氧类树脂。在第一黏接胶302a1~302a4中的填料可以包括银粒子、金粒子、银纤维、金纤维、一或多个其他合适的填料或其组合。在第二黏接胶302b1~302b4中的填料可以包括二氧化硅粒子、氧化铝(alumina)粒子、二氧化硅纤维、氧化铝纤维、一或多个其他合适的填料或其组合。

98.然而,本公开的实施例不限于此。在一些实施例中,第二黏接胶302b1~302b4不包括填料。在一些实施例中,第一黏接胶302a1~302a4为含银的环氧类粘胶(silver-containing epoxy-based glues),而第二黏接胶302b1~302b4为硅类粘胶(silicone-based glues)。

99.第一黏接胶302a1~302a4可具有第一存储模数,而第二黏接胶302b1~302b4可具有第二存储模数。在一些实施例中,第一存储模数大于第二存储模数。在室温下,第一存储模数可以在从大约0.5gpa至大约6gpa的范围内。在室温下,第二存储模数可以在从大约0.005gpa至大约0.01gpa的范围内。

100.第一黏接胶302a1~302a4可以具有第一热膨胀系数(coefficient of thermal expansion),且第二黏接胶302b1~302b4可以具有第二热膨胀系数。在一些实施例中,第二热膨胀系数大于第一热膨胀系数。

101.第一黏接胶302a1~302a4可具有第一黏度(viscosity),而第二黏接胶302b1~302b4可具有第二黏度。在一些实施例中,第二粘度大于第一粘度。第一黏度可以在从大约20pa-s至大约100pa-s的范围中。举例而言,第一粘度可为大约25pa-s或大约50pa-s。第二黏度可以在从大约150pa-s至大约600pa-s的范围中。举例而言,第二粘度可为大约400pa-s。

102.第一黏接胶302a1~302a4可具有第一玻璃转化温度(glass transition temperature),而第二黏接胶302b1~302b4可具有第二玻璃转化温度。在一些实施例中,第一玻璃转化温度高于第二玻璃转化温度。第一玻璃转化温度可在从大约10摄氏度(degrees c)至大约150摄氏度的范围中。举例而言,第一玻璃转化温度可为大约11摄氏度或大约120摄氏度。第二玻璃转化温度可低于0摄氏度。

103.在附接保护盖至基板20之后进行的一些实施例的模拟(simulation)结果中,具有较高存储模数的第一黏接胶302a1~302a4可能导致保护层116及/或底部填充结构114的破裂风险更高。据此,在一些实施例中,具有较高存储模数的第一黏接胶302a1~302a4定位(positioned)在侧边部分s1~s4处。由于基板20的侧边部分s1~s4处的热应力(thermal stress)低于基板20的角隅部分c1~c4处的热应力,因此即使施加第一黏接胶302a1~302a4,可以维持破裂的风险在可接受的程度中。

104.在一些实施例中,使接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4设计为位于基板20的侧边部分s1~s4中,而以第一黏接胶302a1~302a4覆盖接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4。因此,在侧边部分s1~s4上的第一黏接胶302a1~302a4可与接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4电性接触,而不会导致较高的破裂风险。

105.在一些实施例中,具有较低存储模数的第二黏接胶302b1~302b4位于基板20的角隅部分c1~c4处,以补偿较高的角隅应力(corner stress),前述角隅应力由介于基板20及后续附接的保护盖之间的热膨胀系数(coefficient of thermal expansion)失配(mismatch)及/或介于基板20及晶粒封装10之间的热膨胀系数失配所导致。

106.第一黏接胶302a1~302a4可占据基板20的第一面积,而第二黏接胶302b1~302b4可占据基板20的第二面积。在一些实施例中,第二面积大于第一面积。

107.如图2c及图3c所示,根据一些实施例,分配或施加导热胶(thermally conductive glue)304在晶粒封装10的顶部上。如图3c所示,为了简单及清楚起见,由导热胶304所覆盖的芯片结构以虚线来显示。在一些实施例中,在分配或施加第一黏接胶302a1~302a4及第二黏接胶302b1~302b4之后,分配或施加导热胶304。在一些其他实施例中,在分配或施加第一黏接胶302a1~302a4及第二黏接胶302b1~302b4之前,分配或施加导热胶304。

108.可以对本公开的实施例进行各种变形及/或修改。在一些实施例中,一或多个第一黏接胶302a1~302a4以一或多个第一黏接带(adhesive tape)取代。在一些实施例中,一或多个第二黏接胶302b1~302b4以一或多个第二黏接带取代。在一些实施例中,导热胶304由导热胶带(thermally conductive tape)取代。

109.如图2d所示,根据一些实施例,设置保护盖306在晶粒封装10及基板20上方。保护盖306可用作翘曲控制元件及/或散热器(heat spreader)。保护盖306可包括上板305a及支撑结构305b。在一些实施例中,保护盖306及基板20共同围绕封闭的(enclosed)(或者,密封的(sealed))空间,其中晶粒封装10位于前述封闭的(或者,密封的)空间中。

110.在一些实施例中,上板305a及支撑结构305b一体形成(formed in one piece)。在一些其他实施例中,上板305a及支撑结构305b是两个分离的部件,前述上板305a及支撑结构305b通过位于前述上板305a及支撑结构305b之间的导电胶接合在一起。在一些实施例中,保护盖306由导电材料制成,诸如金属材料或经掺杂的半导体材料。导电材料可以包括

钢(steel)、铝、金、铜、经掺杂的半导体材料、一或多个其他合适的材料或其组合。

111.在一些实施例中,如图2d及图3d所示,通过第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4附接保护盖306到基板20上。在一些实施例中,在附接保护盖306到基板20之后,对第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4执行热制程,从而提高介于保护盖306及基板20之间的粘着性。操作温度可以在从大约120摄氏度至大约180摄氏度的范围中。操作时间可以在从大约200秒至大约2小时的范围中。在一些其他实施例中,在附接保护盖306到基板20之前,对第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4执行其他的热制程。

112.在一些实施例中,通过导热元件304,使保护盖306附接到晶粒封装10’。如上所述,在一些实施例中,图3d显示在图2d中所示的结构的俯视图。图2d显示沿着图3d中的线段2d-2d所撷取的结构的剖面图。为了简单及清楚起见,在图3d中不显示保护盖306。

113.在一些实施例中,通过保护盖306的支撑结构305b挤压(squeezed)第一黏接胶302a1~302a4及第二黏接胶302b1~302b4。因此,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4变得更薄,且占据基板20的更大面积。第一黏接胶302a1~302a4及第二黏接胶302b1~302b4分布在介于保护盖306及基板20之间。结果是,如图2d及图3d所示,形成第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4。类似地,导热胶304分布在介于保护盖306及晶粒封装10之间。结果是,形成导热元件304’。

114.在一些实施例中,如图2d及图3d所示,第一黏接元件302a

’1的外边缘(outer edge)实质上与基板20的侧壁及/或保护盖306的支撑结构305b的外侧壁对齐。在一些实施例中,如图2d及图3d所示,导热元件304’的边缘实质上与晶粒封装10的侧壁对齐。

115.在一些实施例中,如图2c及图3c所示,在设置保护盖306于基板20上方之前,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4彼此分离。在设置保护盖306之后,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4朝向彼此延伸,以形成第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4。在一些实施例中,如图3d所示,第一黏接元件302a

’1~302a

’4中的每一个直接接触第二黏接元件302b

’1~302b

’4中的两个。

116.然而,本公开的实施例并不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其他实施例中,在附接保护盖306到基板20之前,第一黏接胶302a1~302a4及第二黏接胶302b1~302b4中的一些彼此直接接触。

117.如上所述,第一黏接元件302a

’1~302a

’4由导电胶形成。因此,第一黏接元件302a

’1~302a

’4也是导电的,且能够形成介于保护盖306及接地结构203a1~203a4、203b1~203b4、203c1~203c4及203d1~203d4之间的电性连接。因此,保护盖306电性接地,且亦可以用于防止或减少传输至保护盖306所保护的晶粒封装10的电磁干扰(emi)及/或防止或减少来自保护盖306所保护的晶粒封装10的电磁干扰。是以,大幅度地提高封装结构的性能及品质。

118.在一些实施例中,第一黏接元件302a

’1~302a

’4位于基板20的侧边部分s1~s4上,而不位于基板20的角隅部分c1~c4上。因此,可以维持封装结构的破裂风险在可接受的程度中。

119.在一些实施例中,第二黏接元件302b

’1~302b

’4位在基板20的角隅部分c1~c4上。第二黏接元件302b

’1~302b

’4可以用于补偿在临近角隅部分c1~c4的较高的热应力。在一

些实施例中,由于混合黏接元件(hybrid adhesive elements)包括第一黏接元件302a

’1~302a

’4及第二黏接元件302b

’1~302b

’4,因此可以同时减少或防止emi问题及封装可靠性问题。

120.可以对本公开的实施例进行各种变形及/或修改。图4是根据一些实施例的封装结构的一部分的俯视图。在一些实施例中,通过第二黏接元件302b’的一部分,使第一黏接元件302a

’1~302a

’4中的每一个与基板20的侧壁分离。在一些实施例中,通过第二黏接元件302b’连续地围绕第一黏接元件302a

’1~302a

’4中的每一个。

121.可以对本公开的实施例进行各种变形及/或修改。图5是根据一些实施例的封装结构的一部分的平面图。类似于图3d中所示的实施例,多个第一黏接元件302a

’1~302a

’4及多个第二黏接元件302b

’1~302b

’4用于附接保护盖306到基板20。

122.在图5中的第一黏接元件302a

’1~302a

’4可以具有与在图3d中的第一黏接元件302a

’1~302a

’4的俯视形状(top view shape)不同的俯视形状。在一些实施例中,如图5所示,第一黏接元件302a

’1~302a

’4具有椭圆状的俯视形状。在一些实施例中,第一黏接元件302a

’1~302a

’4中的一个或一些部分地覆盖基板20,前述基板20不直接位于保护盖306的支撑结构305b下方。

123.在一些实施例中,第一黏接元件302a

’1~302a

’4中的每一个覆盖两个或更多接地结构。然而,本公开的实施例不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其它实施例中,第一黏接元件302a

’1~302a

’4中的一个或一些仅覆盖一个接地结构。

124.图6是根据一些实施例的封装结构的一部分的平面图。在一些实施例中,形成多个第一黏接元件602a

’1~602a

’3在基板20的在侧边部分s1上方。第一黏接元件602a

’1~602a

’3的材料及形成方法可以与第一粘接元件302a

’1~302a

’4相同或相似。

125.在一些实施例中,第一黏接元件602a

’1~602a

’3中的每一个覆盖且电性接触一个对应的接地结构。举例而言,第一黏接元件602a

’1、602a

’2及602a

’3分别覆盖接地结构203a1、203a2及203a3。类似地,在一些实施例中,形成多个第一黏接元件602b

’1~602b

’3在基板20的侧边部分s3上方,以分别覆盖接地结构203b1、203b2及203b3。形成多个第一黏接元件602c

’1~602c

’3在基板20的侧边部分s2上方,以分别覆盖接地结构203c1、203c2及203c3。形成多个第一黏接元件602d

’1~602d

’3在基板20的侧边部分s4上方,以分别覆盖接地结构203d1、203d2及203d3。

126.在一些实施例中,通过第二黏接元件302b’围绕第一黏接元件602a

’1~602a

’3、602b

’1~602b

’3、602c

’1~602c

’3及602d

’1~602d

’3。第二黏接元件302b’可助于减少封装结构的破裂的风险,且第一黏接元件602a

’1~602a

’3、602b

’1~602b

’3、602c

’1~602c

’3及602d

’1~602d

’3形成介于保护盖306及接地结构之间的电性连接。

127.在一些实施例中,接地结构的顶表面与基板20的顶表面实质上齐平。然而,本公开的实施例不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其他实施例中,接地结构的顶表面与基板20的顶表面处于一或多个不同的高度程度(hight level)中。

128.图7是根据一些实施例的封装结构的一部分的剖面图。在一些实施例中,如图7所示,接地结构203a2及203b2的顶表面低于基板20的顶表面。在一些实施例中,提供具有类似于在图2a中所示结构的结构。之后,使用回蚀制程,以部分地移除接地结构203a2及203b2。结果是,形成凹部在接地结构203a2及203b2上。之后,执行类似于图2b至图2d及图3b至图3d中

描述的制程。结果是,形成如图7所示的结构。

129.在一些实施例中,第一黏接元件302a

’1及302a

’2具有填充在接地结构203a2及203b2上的凹部的突出部分702。突出部分702可助于增强介于保护盖306及基板20之间的粘着性。

130.可以对本公开的实施例进行各种变化及/或修改。图8是根据一些实施例的封装结构的一部分的剖面图。在一些实施例中,接地结构203a2及203b2从基板20的顶表面突出。在一些实施例中,如图8所示,接地结构203a2及203b2向上延伸到第一黏接元件302a

’1及302a

’2。接地结构203a2及203b2的顶表面203t位于高于基板20的顶表面的高度程度。接地结构203a2及203b2的顶表面203t介于第一黏接元件302a

’1或第一黏接元件302a

’2的顶表面及底表面之间。

131.在图2d、图7及图8所示的一些实施例中,基板20围绕接地结构。然而,本公开的实施例不限于此。可以对本公开的实施例进行各种变形及/或修改。在一些其他实施例中,接地结构的一部分或全部形成在基板20的外部,而不受基板20围绕。

132.图9是根据一些实施例的封装结构的一部分的剖面图。在一些实施例中,沿着基板20的侧壁形成接地结构903a及903b。一些接合结构208形成为与接地结构903a及903b电性连接,且作为接地凸块。之后,执行类似于图2b至图2d及图3b至图3d所示的制程。结果是,形成如图9所示的结构。第一黏接元件302a

’1及302a

’2形成介于保护盖306及接地结构903a及903b之间的电性连接。因此,保护盖306电性接地,且保护盖306能够减少或防止电磁干扰(emi)到保护盖306下方的一或多个芯片结构及/或封装、及/或减少或防止来自保护盖306下方的一或多个芯片结构及/或封装的电磁干扰。

133.在图2d、图7、图8及图9所示的一些实施例中,第一黏接元件及/或第二黏接元件的内侧壁与保护盖306的支撑结构305b的内侧壁实质上对齐。然而,本公开的实施例不限定于此。可以对本公开的实施例进行各种变形及/或修改。在一些其他实施例中,第一黏接元件及/或第二黏接元件的内侧壁与保护盖306的支撑结构305b的内侧壁为未对准(misaligned)。

134.图10是根据一些实施例的封装结构的一部分的剖面图。在一些实施例中,第一黏接元件302a

’1及302a

’2延伸超出支撑结构305b的内侧壁。在一些实施例中,第一黏接元件302a

’1及302a

’2进一步沿着支撑结构305b的内侧壁向上延伸。在一些实施例中,如图10所示,通过第一黏接元件302a

’1及302a

’2覆盖支撑结构305b的内侧壁的下部。沿着支撑结构305b的内侧壁延伸的第一黏接元件302a

’1及302a

’2的一部分可助于增强介于保护盖306及基板20之间的粘着性及介于保护盖306与接地结构203a2及203b2之间的粘着性。

135.可以对本公开的实施例进行各种变形及/或修改。图11是根据一些实施例的封装结构的一部分的剖面图。在一些实施例中,设置第二晶粒封装(或含芯片的结构)10’到基板20上。在一些实施例中,保护盖306覆盖晶粒封装10,而不覆盖第二晶粒封装10’。由于晶粒封装10通过电性连接到接地结构203a2及203b2的保护盖306的保护,因此显著减少到晶粒封装10及/或来自晶粒封装10的电磁干扰(emi)。显著提升晶粒封装10及第二晶粒封装10’的性能及可靠性。

136.在一些其他实施例中,亦包括其他部件及制程。举例而言,可以包括测试结构,以帮助对3d封装或3d-ic装置进行验证测试。举例而言,测试结构可以包括:在重分布层中或

在基板上形成的测试垫片,前述测试垫片允许对3d封装或3d-ic测试、使用探针(probe)及/或探针卡(probe cards)及其类似物。验证测试可以在中间结构以及最终结构上执行。此外,本文公开的结构及方法可以与测试方法结合使用,前述测试方法包括对于已知良好的晶粒的中间验证,以提高产量并降低成本。

137.本公开的实施例形成具有保护盖的封装结构,前述保护盖用于翘曲控制、散热及/或emi保护。两个或更多个黏接元件用于接合(bond)保护盖至承载一或多个芯片结构的基板。黏接元件中之一者是导电的且能够在介于保护盖及接地结构之间形成电性连接。另一种黏接元件可以帮助降低封装结构破裂的风险。由于混用黏接元件,可以同时减少或防止emi问题及封装可靠性问题。显著地提高封装结构的性能及品质。

138.根据一些实施例,提供封装结构的形成方法。前述方法包括:设置芯片(chip)结构在基板上方;以及形成第一黏接元件(adhesive element)在基板上方。第一黏接元件具有第一电阻率(electrical resistivity)。前述方法亦包括:形成第二黏接元件在基板上方。第二黏接元件具有第二电阻率,且第二电阻率大于第一电阻率。前述方法还包括:通过(through)第一黏接元件及第二黏接元件附接(attching)保护盖到基板。保护盖围绕(surrounds)芯片结构且覆盖芯片结构的顶表面。

139.在一些实施例中,保护盖包括金属材料。在一些实施例中,前述方法还包括:形成接地结构。接地结构通过第一黏接元件电性连接至保护盖。在一些实施例中,在形成第一黏接元件之前,接地结构形成在基板中。在一些实施例中,前述方法还包括:形成多个接地导孔(ground vias)在基板中。形成第一黏接元件以覆盖多个接地导孔的至少一些。在一些实施例中,前述方法还包括:在附接保护盖到基板之前,形成导热(thermally conductive)元件在芯片结构上。在附接保护盖到基板之后,导热元件与保护盖直接接触。在一些实施例中,前述方法还包括:分配(dispensing)第一黏接胶在基板的侧边部分(side portion)上方;分配第二黏接胶在基板的角隅部分(coner portion)上方;以及设置保护盖在第一黏接胶及第二黏接胶上方,使得第一黏接胶及第二黏接胶分别分布(spread)在介于保护盖及基板之间,以形成第一黏接元件及第二黏接元件。在一些实施例中,第一黏接胶具有第一粘度(viscosity),第二黏接胶具有第二粘度,且第二粘度大于第一粘度。在一些实施例中,第一黏接胶具有第一玻璃转化温度(glass transition temperature),第二黏接胶具有第二玻璃转化温度,且第一玻璃转化温度大于第二玻璃转化温度。在一些实施例中,第一黏接胶具有第一存储模数(storage modulus),第二黏接胶具有第二存储模数,且第一存储模数大于第二存储模数。

140.根据一些实施例,提供封装结构。前述封装结构包括基板以及在基板上方的芯片结构。前述封装结构亦包括通过第一黏接元件及第二黏接元件附接至基板的保护盖。第一黏接元件及第二黏接元件由不同材料制成。前述封装结构还包括通过第一黏接元件电性连接至保护盖的接地结构。

141.在一些实施例中,第一黏接元件具有第一电阻率,第二黏接元件具有第二电阻率,且第二电阻率大于第一电阻率。在一些实施例中,通过基板围绕接地结构。在一些实施例中,第一黏接元件直接接触第二黏接元件。在一些实施例中,前述封装结构还包括第二接地结构,其中第一黏接元件覆盖接地结构及第二接地结构。

142.根据一些实施例,提供封装结构。前述封装结构包括基板以及在基板上方的晶粒

封装(die package)。前述封装结构亦包括通过第一黏接元件及第二黏接元件附接至基板的保护盖(protective lid)。保护盖覆盖晶粒封装。第一黏接元件具有第一电阻率,第二黏接元件具有第二电阻率。第二电阻率大于第一电阻率。

143.在一些实施例中,第一黏接元件覆盖基板的侧边部分,且第二黏接元件覆盖基板的角隅部分。在一些实施例中,封装结构还包括通过基板围绕的多个接地导孔。第一黏接元件覆盖接地导孔。在一些实施例中,前述封装结构还包括通过基板围绕的第一接地导孔。第一黏接元件覆盖第一接地导孔。前述封装结构亦包括通过基板围绕的第二接地导孔。前述封装结构亦包括介于保护盖及基板之间的第三黏接元件。其中第三黏接元件覆盖第二接地导孔。在一些实施例中,第三黏接元件具有第三电阻率。第二电阻率大于第三电阻率。

144.前述内文概述了各种实施例的部件,使所属技术领域中具有通常知识者可以更佳地了解本公开的态样。所属技术领域中具有通常知识者应可理解的是,他们可轻易地以本公开为基础来设计或修饰其他制程及结构,并以此达到与在本文中介绍的实施例相同的目的及/或达到相同的优点。所属技术领域中具有通常知识者也应理解的是,这些等效的构型并未脱离本公开的精神与范围,且在不脱离本公开的精神与范围的情况下,可对本公开进行各种改变、取代或替代。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1