电路板及其制作方法与流程

1.本发明涉及一种电路板及其制作方法。

背景技术:

2.近年来,电子产品被广泛应用在日常工作和生活中,其中,摄像头更是起到越来越重要的作用,对摄像头性能的要求也越来越高。为实现这种需求,摄像头内部的各种零件需要相应的优化。目前摄像头采用的微型马达由于采用漆包铜丝做线圈,需进行打件到电路板上,再绕折呈方形结构以适配摄像头。漆包铜线绝缘层一般较厚,不利于实现微型化,线距大,导致线圈层数多产品厚,一般线圈的厚度》0.4mm,且生产流程需电路板的制作及线圈的制作打件,流程较长,生产效率较低。

技术实现要素:

3.有鉴于此,有必要提供一种能解决上述问题的电路板的制作方法。

4.还提供一种上述制作方法制作的电路板。

5.本技术的实施例提供一种电路板的制作方法,包括以下步骤:

6.在基板的第一铜层上蚀刻形成凹槽;

7.在所述凹槽中形成金属层,形成功能区域,所述金属层的蚀刻速率小于第一铜层;

8.在所述第一铜层及所述金属层上进行压膜、曝光、显影,露出部分所述第一铜层及所述功能区域的部分所述金属层;

9.将所述功能区域外的所述第一铜层蚀刻形成第一线路层;

10.在露出的部分所述金属层上电镀形成连接柱及线圈;

11.进行去膜;

12.将所述功能区域中露出的所述金属层及其下方的所述第一铜层蚀刻,使所述功能区域的所述连接柱、所述金属层与所述第一铜层形成第二线路层,使所述线圈、所述金属层与所述第一铜层形成第三线路层。

13.进一步地,在本技术的一些实施例中,在基板的第一铜层上蚀刻形成凹槽的步骤包括:在所述第一铜层上覆盖一层干膜;对所述干膜进行曝光、显影,露出所述第一铜层;对所述第一铜层进行定深蚀刻形成所述凹槽。

14.进一步地,在本技术的一些实施例中,所述凹槽底部的所述第一铜层的厚度在1μm~3μm。

15.进一步地,在本技术的一些实施例中,所述金属层通过磁控溅射、涂层、喷涂或化镀的方法形成。

16.进一步地,在本技术的一些实施例中,所述金属层的厚度小于等于1μm。

17.进一步地,在本技术的一些实施例中,所述金属层与所述第一铜层的蚀刻速率比小于1:10。

18.本技术的实施例还提供一种电路板,包括:

19.一基板,所述基板包括基层及形成于所述基层表面的第一线路层,所述第一线路层中存在功能区域;

20.位于所述功能区域的第二线路层,包括形成于所述基层表面的第一铜层、形成于所述第一铜层表面的金属层及形成于所述金属层表面的连接柱;

21.及位于所述功能区域的第三线路层,包括形成于所述基层表面的第一铜层、形成于所述第一铜层表面的金属层及形成于所述金属层表面的线圈。

22.进一步地,在本技术的一些实施例中,所述金属层与所述第一铜层、所述第一线路层、所述连接柱及所述线圈的材质不同。

23.进一步地,在本技术的一些实施例中,所述第二线路层及所述第三线路层的所述第一铜层的厚度在1μm~3μm。

24.进一步地,在本技术的一些实施例中,所述金属层的厚度小于等于1μm。

25.进一步地,在本技术的一些实施例中,所述电路板能够在所述第一线路层处绕折,形成包括四个所述线圈的矩形结构,四个所述线圈两两相对。

26.本发明提供的电路板,提供电路板的制作工艺将线圈直接通过电镀形成在电路板上,可实现线圈的小型化,且线圈及电路板基板集成一体成型,无需线圈的单独制作及打件,生产效率提高。

附图说明

27.图1是本发明一实施方式的基板的剖视示意图。

28.图2是对图1所示的基板进行压膜的剖视示意图。

29.图3是对图2所示的基板进行曝光、显影及定深蚀刻的示意图。

30.图4是在图3所示基板的凹槽中形成金属层,并进行去膜的示意图。

31.图5是对图4所示的基板进行压膜的示意图。

32.图6是对图5所示基板进行曝光、显影的剖视示意图。

33.图7是对图6所示基板进行蚀刻的剖视示意图。

34.图8是对图7所示基板上的功能区域进行电镀的剖视示意图。

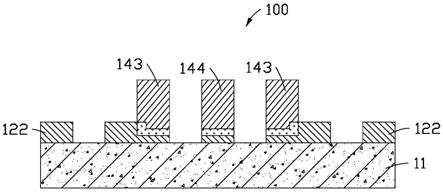

35.图9是对图8所示基板进行去膜的剖视示意图。

36.图10是对图9所示功能区域的金属层进行蚀刻的剖视示意图。

37.图11是对图10所示对功能区域中的第一铜层进行蚀刻的剖视示意图。

38.图12是本发明一实施方式的线圈的示意图。

39.图13是本发明一实施方式的电路板的应用示意图。

40.主要元件符号说明

41.电路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100

42.基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10

43.基层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11

44.第一铜层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

45.凹槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

121

46.第一线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122

47.金属层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13

48.功能区域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

49.连接柱

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

141

50.线圈

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

142

51.第二线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

143

52.第三线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

144

53.干膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20、30

54.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

55.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

56.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

57.下面结合附图,对本发明的一些实施方式作详细说明。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

58.本技术的实施例提供一种电路板的制作方法,包括以下步骤:

59.在基板的第一铜层上蚀刻形成凹槽;

60.在所述凹槽中形成金属层,形成功能区域,所述金属层的蚀刻速率小于第一铜层;

61.在所述第一铜层及所述金属层上进行压膜、曝光、显影,露出部分所述第一铜层及所述功能区域的部分所述金属层;

62.将所述功能区域外的所述第一铜层蚀刻形成第一线路层;

63.在露出的部分所述金属层上电镀形成连接柱及线圈;

64.进行去膜;

65.将所述功能区域中露出的所述金属层及其下方的所述第一铜层蚀刻,使所述功能区域的所述连接柱、所述金属层与所述第一铜层形成第二线路层,使所述线圈、所述金属层与所述第一铜层形成第三线路层。

66.本技术的实施例还提供一种电路板,包括:

67.一基板,所述基板包括基层及形成于所述基层表面的第一线路层,所述第一线路层中存在功能区域;

68.位于所述功能区域的第二线路层,包括形成于所述基层表面的第一铜层、形成于所述第一铜层表面的金属层及形成于所述金属层表面的连接柱;

69.及位于所述功能区域的第三线路层,包括形成于所述基层表面的第一铜层、形成于所述第一铜层表面的金属层及形成于所述金属层表面的线圈。

70.上述电路板,提供电路板的制作工艺将线圈直接通过电镀形成在电路板上,可实现线圈的小型化,且线圈及电路板基板集成一体成型,无需线圈的单独制作及打件,生产效率提高。

71.下面结合附图,对本技术的实施例作进一步的说明。

72.请参阅图1至图11,本发明的一实施方式中电路板100的制作方法,其包括以下步骤:

73.步骤s101,请参阅图1,提供一基板10。所述基板10包括一可挠性的绝缘的基层11及形成于所述基层11表面的第一铜层12。

74.所述基层11的材质可选自聚酰亚胺(polyimide,pi)、液晶聚合物(liquid crystal polymer,lcp)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等材料中的一种。

75.步骤s102,请参阅图2,对基板10进行压膜,在所述第一铜层12上覆盖一层干膜20。

76.步骤s103,请参阅图3,对基板10进行曝光、显影及定深蚀刻制程,在基板10的所述第一铜层12上蚀刻出一凹槽121。

77.具体地,通过曝光、显影将未曝光的干膜20去掉,随后通过选择性蚀刻,在干膜20中暴露的所述第一铜层12上形成凹槽121,使所述凹槽121底部的所述第一铜层12厚度在1μm~3μm。

78.步骤s104,请参阅图4,在凹槽121中形成一金属层13,形成功能区域14,并对基板10进行去膜制程,将所述干膜20去除。

79.具体地,通过磁控溅射方法在凹槽121中形成金属层13,所述金属层13的厚度小于等于1μm。

80.所述金属层13与第一铜层12的材质不同。所述金属层13与第一铜层12的蚀刻速率差别较大。在一些实施例中,所述金属层13的材质可为纳米银、nicr合金等导电金属材料。

81.形成所述金属层13的方法不局限于磁控溅射方法,在一些实施例中,所述金属层13也可通过涂层(coating)、喷涂、化镀等其他方式形成。

82.步骤s105,请参阅图5,对基板10进行压膜,在所述第一铜层12及金属层13上覆盖一层干膜30。

83.步骤s106,请参阅图6,对基板10进行曝光、显影制程,去掉未曝光的干膜30,露出部分第一铜层12及功能区域14的部分金属层13。

84.步骤s107,请参阅图7,对基板10上暴露的第一铜层12进行蚀刻制程,使基板10上除功能区域14外的所述第一铜层12被蚀刻形成第一线路层122。

85.具体地,由于金属层13与第一铜层12不同,采用对铜的蚀刻速度大于金属层13的蚀刻液,蚀刻速率比最好大于10:1(如采用cucl2蚀刻液),功能区域14中由于金属层13的阻挡,因此,其下的第一铜层12未被蚀刻。

86.步骤s108,请参阅图8,对基板10上的功能区域14进行电镀,在功能区域14的金属层13上形成连接柱141及线圈142。所述连接柱141位于所述线圈142与所述第一线路层122之间。

87.步骤s109,请参阅图9,对基板10进行去膜制程,将所述干膜30去除,使得功能区域14中暴露出金属层13。

88.步骤s110,请参阅图10,对功能区域14的金属层13进行蚀刻制程,暴露出金属层13底部的第一铜层12。

89.具体地,通过采用对金属层13蚀刻速率较大的蚀刻液,将功能区域14中暴露的金

属层13蚀刻掉,使其底部的第一铜层12暴露。

90.步骤s111,请参阅图11,对功能区域14中的第一铜层12进行蚀刻制程,暴露出底部的基层11,形成电路板100。

91.具体地,由于功能区域14中的第一铜层12比第一线路层122薄,因此,可通过采用快速蚀刻的方式,将功能区域14中暴露的第一铜层12蚀刻,对其他区域的第一线路层122的蚀刻较小,基本不发生改变,使功能区域14中的连接柱141、金属层13与第一铜层12形成第二线路层143,使线圈142、金属层13与第一铜层12形成第三线路层144。其中,第三线路层144为线圈功能区,当电路板100用于微型马达中时,所述第三线路层144在通电后产生磁场,以此来实现驱动。第二线路层143可以是用于连接第三线路层144与电源之间的连接线。

92.具体地,请参阅图12,由于采用电路板工艺制得线圈142,因此线圈142的线宽及线距可设计的更细。具体地,线圈142形成的第三线路层144中线路的线宽l≤30μm,线距s≤20μm,所述线圈142的厚度大于50μm。产品总厚度可小于等于0.3mm。

93.可以理解的,在一些实施例中,所述电路板100还可设计成双面板或多层板。

94.请同时参阅图图11,本发明的一实施方式还提供一种电路板100,其包括一基板10、位于基板10表面的第二线路层143及位于第二线路层143中第三线路层144。

95.所述基板10包括一可挠性的绝缘的基层11及形成于所述基层11表面的第一线路层122。

96.所述基层11的材质可选自聚酰亚胺(polyimide,pi)、液晶聚合物(liquid crystal polymer,lcp)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等材料中的一种。

97.所述第一线路层122中存在功能区域14,所述第二线路层143及第三线路层144位于所述功能区域14中。

98.所述第二线路层143及所述第三线路层144分别包括形成于所述基层11表面的第一铜层12、形成于第一铜层12表面的金属层13及形成于金属层13表面的连接柱141或线圈142。

99.所述线圈142的数量及匝数均可根据实际的驱动需求进行相应的设置。

100.所述第二线路层143及所述第三线路层144中的第一铜层12厚度小于第一线路层122,范围在1~3μm。

101.所述金属层13的厚度小于等于1μm。所述金属层13与第一铜层12的材质不同。在一些实施例中,所述金属层13的材质可为纳米银、nicr合金等导电金属材料。

102.其中,所述第三线路层144为线圈功能区,第二线路层143可以是用于连接第三线路层144与电源之间的连接线。

103.参阅图13,电路板100可在第一线路层122处进行绕折,形成包括四个所述线圈功能区的矩形结构,四个所述第三线路层144的线圈142两两相对,从而形成用于驱动的磁场,得到的产品可应用于微型马达,如摄像头中。由于其线圈及电路板基板集成一体成型,使其更适于制作微型产品,且效率较高。

104.本发明提供的电路板100,提供电路板的制作工艺将线圈直接通过电镀形成在电路板上,可实现线圈的小型化,且线圈及电路板基板集成一体成型,无需线圈的单独制作及打件,生产效率提高。

105.以上所述,仅是本发明的较佳实施方式而已,并非对本发明任何形式上的限制,虽然本发明已是较佳实施方式揭露如上,并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施方式,但凡是未脱离本发明技术方案内容,依据本发明的技术实质对以上实施方式所做的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1