一种离散与连续混合型的高精度单比特数模转换电路的制作方法

[0001]

本发明属于模数混合电路领域,具体涉及一种离散与连续混合型的高精度单比特数模转换电路。

背景技术:

[0002]

隔离放大器通常由调制电路和解调电路两部分组成。调制电路将模拟信号转换为调制信号传送过隔离带到达副边,副边的解调电路将调制信号转换为模拟信号实现了具有隔离能力的放大器。该调制电路和解调电路最普遍的结构是单比特(sigma-delta)模数转换器(adc)和单比特数模转换器(dac),该结构有很好的线性度和很低的噪声,抗干扰能力强。其中单比特数模转换器有离散型和连续型两种。

[0003]

如图1a所示的离散型数模转换器,由开关电容(switch capacitor,sc)积分器实现。积分器输入根据数字信号x(t)选择接正参考电压vrefp和负参考电压vrefn实现数模转换。该结构对时钟抖动不敏感,可实现很高的信噪比。是dac的主流实现方法。参照图1b,开关电容dac面临压摆(slewing)问题及由采样带来的spur问题,通过合理的设计,可以降低它们对线性度的影响,但是它们对增益带来的影响还是存在。隔离放大器对增益精度要求很高,但该结构的增益精度不够好,尤其是温度变化会影响放大器的压摆率,从而影响增益,使得该结构的增益温漂大。

[0004]

如图2所示,连续型数模转换器,由rc积分器实现。积分器输入根据数字信号x(t)选择接正参考电压vrefp和负参考电压vrefn实现数模转换。该结构对放大器带宽和压摆率要求都很低,没有压摆率建立问题和spur问题,线性度好,增益精度高。但该结构对时钟抖动和x(t)=1或0的时间长度敏感,时钟抖动会引入带内噪声,单个x(t)=1的时长如果与单个x(t)=0的时间不同,会引入失调电压。

技术实现要素:

[0005]

本发明要解决的技术问题是提供一种新型的dac电路其能够避免开关电容积分器的压摆问题和spur问题,并能够避免时钟抖造成rc积分器带入噪声。

[0006]

为此本发明提供一种离散与连续混合型的高精度单比特数模转换电路,包括第一级积分器和第二级积分器,所述第一级积分器的输出端与所述第二级积分器的输入端连接;所述第一级积分器为离散型sc积分器,所述第二级积分器r为连续型rc积分器;所述第一级积分器的输入端连接数字信号输入电路d,所述第二级积分器的输出端为模拟信号输出端。

[0007]

作为本发明一实施方式的进一步改进,所述第一级积分器包括斩波放大器、采样电容组、积分电容组、采样开关组和积分开关组;所述积分电容组包括连接在斩波放大器负输入端和正输出端的第一积分电容和连接在斩波放大器正输入端和负输出端的第二积分电容;所述采样电容组包括第一采样电容和第二采样电容,采样开关组串联第一采样电容和第二采样电容形成与对参考电平的采样回路;所述积分开关组将所述第一采样电容跨接

在第一级积分器的负输入端和第二级积分器的正输出端,所述积分开关组将所述第二采样电容跨接在第一级积分器的正入端和第二级积分器rc2的负输出端。

[0008]

作为本发明一实施方式的进一步改进,所述采样开关组包括连接第一采样电容和第二采样电容的第一采样开关、用于连接第一采样电容和数字输入电路的第二采样开关、用于连接第二采样电容和数字输入电路的第三采样开关。

[0009]

作为本发明一实施方式的进一步改进,所述积分开关组包括连接第一采样电容和斩波放大器负输入端的第一积分开关、连接第一积分电容和第二级积分器正输出端的第二积分开关、连接第二采样电容和斩波放大器正输入端的第三积分开关;连接第二采样电容和第二级积分器负输出端的第四积分开关。

[0010]

作为本发明一实施方式的进一步改进,所述第一采样开关、第二采样开关、第三采样开关以及第一积分开关、第二积分开关、第三积分开关和第四积分开关的控制端连接非交叠时钟电路;第一至三采样开关在第一时钟周期闭合,第一至第四积分开关在第一时钟周期断开;第一至三采样开关在第二时钟周期断开,第一至第四积分开关在第二时钟周期闭合。

[0011]

作为本发明一实施方式的进一步改进,所述第一时钟周期和第二时钟周期为连续的两个时钟周期,所述第一时钟周期的下降沿与第二时钟周期的上升沿之间存在时延。

[0012]

作为本发明一实施方式的进一步改进,所述第一级积分器的负输入端和第二级积分器的正输出端之间连接第一滤波电容;所述第一级积分器的正输入端和第二级积分器的负输出端之间连接第二滤波电容。

[0013]

作为本发明一实施方式的进一步改进,斩波放大器包括输入斩波器和输出斩波器,所输入斩波器包括第一斩波开关、第二斩波开关、第三斩波开关和第四斩波开关,所述第一斩波开关和第四斩波开关连接斩波控制信号s,所述第二斩波开关和第三斩波开关连接斩波控制信号sn。

[0014]

作为本发明一实施方式的进一步改进,所述第二级积分器包括放大器和连接在放大器输入端和输出端的积分电容组,所述积分电容组包括连接在放大器负输入端和正输出端的第一积分电容以及连接在放大器正输入端和负输出端的第二积分电容;所述第一积分电容和第二积分电容分别并联第一反馈电阻和第二反馈电阻;所述放大器的负输入端和正输入端分别连接第一输入电阻和第二输入电阻。

[0015]

作为本发明一实施方式的进一步改进,所述数字信号输入电路包括:数字信号输入端、第一参考电平输入端、第二参考电平输入端以及第一输出端和第二输出端;所述第一参考电平输入端和第一输出端之间连接第一选择开关;所述第一参考电平输入端和第二输出端之间连接第二选择开关;所述第二参考电平输入端和第一输出端连接第三选择开关;所述第二参考电平输入端和第二输出端之间连接第四选择开关;数字信号控制所述第一选择开关和第四选择开关同时开启或关断;所述控制信号控制所述第二选择开关和第三选择开关同时开启或关断。

[0016]

本发明的有益技术效果在于结合了sc电容积分器和rc积分器两种传统方案的优点。第一级采用开关积分器,对时钟抖动和时钟占空比不敏感,噪声低,线性度好。第一级的输出压摆建立过程通过第二级rc积分器滤波消除,第二级rc积分器输出的模拟信号没有压摆建立过程和spur,不会引入增益误差。而第一级输出中的压摆建立和spur由于是在环路

内部,它们引入的增益误差会第一级的开环增益抑制掉,放大器开环增益有100db左右,残余的增益误差可忽略不计,所以该结构的增益精度很高,且对温度不敏感。同时第一级放大器采用斩波放大器(chopped amp),实现了低失调电压。

附图说明

[0017]

图1a是离散型sc积分器结构示意图;

[0018]

图1b是该积分器输出特性曲线;

[0019]

图2是rc积分器结构示意图;

[0020]

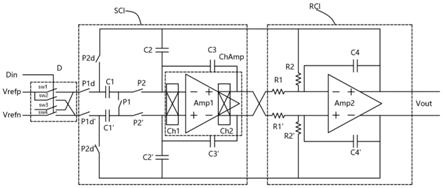

图3是数模转换电路框架结构示意图;

[0021]

图4是数模转换电路内部结构示意图;

[0022]

图5是采样开关组和积分开关组控制时钟信号示意图;

[0023]

图6是斩波器一种实施方式示意图。

具体实施方式

[0024]

以下结合附图对本发明技术方案优选的实施方式进行详细描述,以帮助本领域技术人员理解本发明技术方案,在本申请中使用“组”代表多个同种类型电子器件,例如采样电容组表示多个采样电容。

[0025]

图3所示为数模转换电路框架结构示意图,其中显示了对信号输入输出过程以及信号处理模块,省略了其内部电路细节以及不同模块之间的细微结构。

[0026]

图3所示图数模转换电路,包括第一级积分器sci和第二级积分器rci。第一级积分器sci的输入端sciin与数字信输入电路的输出端dout连接,所述数字信号输入电路d的数字输入端din输入数字信号,第一输入端连接第一参考电平verfp,第二输入端连接第二参考电平verfn。所述第一级积分器sci积分器的输出端sciout与所述第二级积分器rci的输入端rciin连接,所述第一级积分器sci为离散型sc积分器;所述第二级积分器rci为连续型rc积分器。所述第一级积分器sci的输入端sciin连接数字信号输入电路,所述第二级积分器rci的输出端为模拟信号输出端。

[0027]

在上述方案中离散型sc积分器,对时钟抖动和时钟占空比不敏感,噪声特性好,线性度好。其输出压摆建立过程通过第二级rc积分器滤波消除,rc积分器输出的模拟信号没有压摆建立过程和spur,不会引入增益误差。并且由于sc积分器的前置传统的时钟抖动造成rc积分器噪声在上述结构中也不复存在。通过这种离散型sc积分器和rc积分器这种方式构成的数模转换器(dac)兼顾两种传统方案的优点,并规避相应的缺点,具有精度高低失调电压低噪声的优势。

[0028]

参照图4为数模转换电路内部结构示意图,为了清楚其中还示出了数字输入电路内部结构。

[0029]

所述第一级积分器sci包括斩波放大器champ、采样电容组、积分电容组、滤波电容组、采样开关组和积分开关组,这些组件构成全差分结构电路。所述积分电容组包括连接在斩波放大器champ负输入端和正输出端的第一积分电容c3和连接在斩波放大器champ正输入端和负输出端的第二积分电容c3'。所述采样电容组包括第一采样电容c1和第二采样电容c1',采样开关组串联第一采样电容c1和第二采样电容c1'形成与对参考电平verfp/

verfn的采样回路;所述积分开关组将所述第一采样电容c1跨接在第一级积分器sci的负输入端和第二级积分器rci的正输出端,所述积分开关组将所述第二采样电容c1'跨接在第一级积分器sci的正入端和第二级积分器rci的负输出端形成积分回路,第一滤波电容c2和第二滤波电容c2'在积分回路中分别并联在所述第一采样电容c1和第二采样电容c1’两端。

[0030]

该第一级积分器sci使用开关电容替代传统的电阻rc对能够抑制时钟抖动噪声,防止时钟抖动噪声向第二级积分器rci传递。

[0031]

采样开关组包括,第一采样开关p1、第二采样开关p1d和第三采样开关p1d',所述第一采样开关p1连接第一采样电容c1和第二采样电容c1',第二采样开关p1d连接第一采样电容c1的第二端和数字输出电路d的第一输出端;所述第三采样开关p1d'连接第二采样电容c1'和数字输出电路d的第二输出端。

[0032]

所述积分开关组包括,连接第一采样电容c1和斩波放大器champ负输入端的第一积分开关p2、连接第一采样电容c1和第二级积分器rci正输出端的第一积分开关p2d、连接第二采样电容c1'和斩波放大器champ正输入端的第三积分开关p2';连接第二采样电容c1'和第二级积分器负输出端的第四积分开关p2d'。

[0033]

从图4中可以看出上述第一积分电容c3、第二积分电容c3';第一积分开关p2、第三积分开关p2';第二积分开关p2d、第四积分开关p2d';第一采样电容c1、第二采样电容c1';第一滤波电容c2、第二滤波电容c2'分别呈镜像布置连接,该镜像结构构成了第一级积分器sci的差分电路结构。该差分电路结构能够抑制共模信号减少噪声。

[0034]

如图5中所示,第一级积分器sci工作时,采样开关组和积分开关组不断将所述采样电容在采样回路和积分回路中切换。所述采样开关和积分开关对同一时钟控制信号表现出相反的导通性。在第一时钟周期t1中第一采样开关p1第二采样开关p1d和第三采样开关p1d’导通同时第一至第四积分开关断开,并且p1d/p1d'相对p1具有一个较小的时延d1,在第一时钟周期t1所述采样电容c1、c1'连接参考电平verfp和verfn。在第二时钟周期t2中所述第一采样开关p1、第二采样开关p1d和第三采样开关p1d’断开,所述第一积分开关p2、第二积分开关p2d、第三积分开关p2'和第四积分开关p2d'闭合,其中第二积分开关p2d和第四积分开关p2d'相对第一积分开关p2和第三积分开关p2'具有一个较小的时延d2,所述第一采样电容c1和第二采样电容c1'接入积分回路中。在积分回路中所述第一采样电容c1和第二采样电容c1'分别跨接在第二级积分器rci的输出端,同时在积分回路中所述,滤波电容c2与c1并联,降低采样电容c1对vout的冲击,减小向模拟信号输出端vout中引入的纹波。

[0035]

在随后的时钟周期采样开关组和积分开关组重复前述第一时钟周期t1和第二时钟周期t2的动作,进行逐次的采样积分动作。

[0036]

所述时钟信号为非交叠时钟信号。所述第一时钟周期的下降沿和第二时钟周期的上升沿存在时延d3,该时延d3比d1、d2要长。时延d3使得第一时钟周期t1的下降沿和第二时钟周期t2的上升沿不重叠。所述延时d1至d3用于降低积分开关组使用的场效应管沟道注入引入的误差。非交叠时钟可通过利用延时单元将主时钟信号延时生成一个延时时钟信号,并通过与非门、或非门及非门等器件产生多相非交叠时钟信号。

[0037]

所述采样开关组以及积分开关组将所述采样电容c1/c1'连接至采样回路时,采样电容的采集的电压为verfp-verfn或-(verfp-verfn)。采集电压次数由数字信号输入电路d所输入的数字信号决定,所述数字信号为时间相关函数。所述数字输入电路d外部包括第一

参考电平verfp输入端、第二参考电平verfn输入端、第一参输出端、第二输出端sw2;内部包括连接第一参考电平verfp输入端和第一输出端的第一选择开关sw1、连接第一输参考电平入端和第二输出端第二选择开关sw2、连接第二参考电平verfn输入端和第一输出端的第三选择开关sw3、连接第二参考电verfn平输入端和第二输出端的第四选择开关sw4。所述第一至第四选择开关被所述数字输入信号控制,所述数字信号控制所述第一选择开关sw1和第四选择开关sw4同时开启或关断;所述控制信号控制所述第二选择开关sw1和第三选择开关sw3同时开启或关断。具体而言,所述数字信号表示高电平时数字输入电路d的第一选择开关sw1和第四选择开关sw4导通,同时第二选择开关sw2和第三选择开关sw3断开;在采样周期(图5中标号t1)所述第一采样电容c1和第二采样电容c1'串联电压为verfp-verfn。所述数字信号表示低电平时数字输入电路的第二选择开关sw2和第三选择开关sw3导通,在采样周期所述第一采样电容c1和第二采样电容c1'串联电压为-(verfp-verfn)。

[0038]

数字信号电路d输入的第一选择开关sw1至第四选择开关可使用场效应管实现,例如第一至第四选择开关使用nmos,第一选择开关sw1和第四选择开关sw4与数字输入信号连接,第二选择开关sw2和第三选择开sw3关通过数字非门与数字输入信号连接。

[0039]

参照图4和图6斩波放大器champ由放大器amp1和输入斩波器ch1以及输出斩波器ch2构成。所述输入斩波器ch1包括受斩波控制信号控制的开关。第一斩波开关s1、第二斩波开关s2、第三斩波开关s3和第四斩波开关s4;所述第一斩波开关s1和第四斩波开关s4连接斩波控制信号s,所述第二斩波开关s2和第三斩波开关s3连接斩波控制信号sn。用斩波放大器champ(chopped amp),实现了低失调电压。

[0040]

继续参照图4,第二级积分器rci包括放大器amp2和连接在放大器amp2输入端和输出端的积分电容组,所述积分电容组包括连接在放大器amp2负输入端和正输出端的第一积分电容c4以及连接在放大器正输入端和负输出端的第二积分电容c4';所述第一积分电容c4和第二积分电容c4'分别并联第一反馈电阻r2和第二反馈电阻r2';所述放大器的负输入端和正输入端分别连接第一输入电阻r1和第二输入电阻r1'。

[0041]

第二级积分器rci的正输入端和负输入端分别与第一级积分器sci的正输入端和负输入端连接,输入电阻r1/r1'与积分电容c4/c4'组成的rc结构在积分时能够对第一级积分器sci产生的压摆进行滤波,从而使得输出信号精度更高。

[0042]

综上所述,本次发明由输入级的离散型sc积分器和输出级的连续型rc积分器共同组成,第一级采用sc积分器,第二级为rc积分器。第一级放大器采用斩波放大器,实现了低失调电压,并对时钟抖动不敏感。第一级和二级积分器采用全差分结构,能够很好地抑制共模信号噪声。第二级rc积分器对第一级积分器输出信号滤波,消除了sc积分器压摆问题。

[0043]

最后应说明的是:以上实施方式仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施方式对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施方式所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施方式技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1