激光雷达的时间数字转换器避免亚稳态的矫正方法及装置与流程

[0001]

本发明涉及了激光雷达测距技术领域,具体的是一种激光雷达的时间数字转换器避免亚稳态的矫正方法及其矫正装置。

背景技术:

[0002]

本部分的描述仅提供与本发明公开相关的背景信息,而不构成现有技术。

[0003]

在激光雷达测距系统中,为了获得皮秒级别的测距精度,通常使用多级环形振荡器(multi-phase generator)来生成具有多个相位的时钟,一个时钟周期为一个粗计数值(如图1中的ctdc<n:0>),将一个时钟周期再细分成多个等分,所得的计数值称之为细计数值(如图1中的ftdc<p:0>)。为了保持测距的单调性,当粗计数器的ctdc值增加一位时,细计数器的ftdc细计数值必须从最高位(2^(p+1)-1)跳转为最低位(0),常会发生亚稳态(激光返回信号落在ctdc的跳变沿),而导致测距错误。

[0004]

粗计数器ctdc的源时钟是取自于ftdc多相时钟之一。由于多级环形振荡器的时钟到粗计数器ctdc产生计数值的过程中会经过许多延迟,所以第一组粗计数值ctdc0的相位与源时钟的相位关系未知,必须找到一种方法来确认粗计数器ctdc和细计数器ftdc的相位关系,才能实现准确计数。

[0005]

应该注意,上面对技术背景的介绍只是为了方便对本发明的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本发明的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现要素:

[0006]

为了克服现有技术中的缺陷,本发明实施例提供了一种时间数字转换器避免亚稳态的矫正方法及其矫正装置。

[0007]

本申请实施例公开了:一种应用于激光雷达的时间数字转换器避免亚稳态的矫正方法,包括以下步骤:步骤s1:利用触发器来生成检测时钟信号,其中所述检测时钟信号和第一组粗计数值的相位相同或者确定相位关系;步骤s2:打开矫正模式,并通过第二多路复用器来将所述检测时钟信号选通;步骤s3:利用细计数器暨相位解码器对所述检测时钟信号进行取样,来获得所述检测时钟信的细计数值;并将所述检测时钟信号的当前细计数值输出到数字判断逻辑单元中与基准值进行比较,当所述检测时钟信号的所述当前细计数值与所述基准值不等时,提供第一选择信号给第一多路复用器来控制所述第一多路复用器选择下一个相位的时钟信号进入下一级;及步骤s4:重复步骤s3,直到所述检测时钟信号的所述当前细计数值与所述基准值相等,则矫正完成。

[0008]

进一步地,当粗计数值和细计数值的相位关系是正确的,矫正状态位置为1,退出

矫正模式;若遍历全部相位都不能成功,则矫正状态位置为0,退出矫正模式。

[0009]

进一步地,步骤s1是由触发器、反相器、计数器所完成。

[0010]

进一步地,步骤s3是由时间数字转换器,细计数器暨相位解码器,数字判断逻辑模块,第一多路复用器所完成。

[0011]

进一步地,细计数器暨相位解码器由sa触发器、独热编码转二进制译码器组成。

[0012]

本申请实施例公开了:一种应用于激光雷达的时间数字转换器避免亚稳态的矫正装置,包括:多级环形振荡器,用于生成具有多个相位的时钟信号;触发器,用于生成检测时钟信号;第一多路复用器,耦接于所述多级环形振荡器,用于根据第一选择信号来从所述时钟信号选择一个相位输出;数字判断逻辑模块,耦接于所述第一多路复用器,用于判断所述检测时钟信号的当前细计数值是否和基准值相同,当所述检测时钟信号的所述当前细计数值与所述基准值不等时,提供所述第一选择信号给所述第一多路复用器来控制所述第一多路复用器选择下一个相位的所述时钟信号进入下一级;第一计数器,耦接于所述第一多路复用器,用于生成第一组粗计数值;第二计数器,用于生成第二组粗计数值;第二多路复用器,用于根据第二选择信号来从激光信号选择一个输出;粗计数器,用于从所述第一组粗计数值和所述第二组粗计数值中正确选出一组最终粗计数值;细计数器暨相位解码器,用于将粗计数周期分为多个细计数周期,并将相位信号转化为计数值,来生成所述细计数值。

[0013]

进一步地,矫正装置还包括:反相器,用于将所述第一组粗计数值进行反相以生成所述第二组粗计数值。

[0014]

进一步地,所述激光信号是测距时由物体反射回来的,所述激光信号经过光电转换通过采样器得到两组粗计数时间值,当返回的所述激光信号落在第一字段时,则所述第二多路复用器选择所述第一组粗计数值输出;当返回的所述激光信号落在第二字段时,则所述第二多路复用器选择所述第二组粗计数值输出。

[0015]

进一步地,所述时钟信号包括八个相位的时钟,其中所述第一字段与第一个相位的时钟的高电平时间重合,所述第二字段与所述第一个相位的时钟的低电平时间重合,所述第一字段和所述第二字段组成一个周期。

[0016]

进一步地,所述检测时钟和所述第一组粗计数值的相位相同或者确定相位关系。

[0017]

借由以上的技术方案,本发明的有益效果如下:本发明是一种自动选择最终粗计数值ctdc<n:0>的源时钟的矫正方法。通过本发明的矫正方法,生成一个与第一组粗计数值ctdc0<n:0>同相位的检测时钟信号ckd,他们的相位相同。将检测时钟信号ckd作为测距的返回激光信号使用,利用细计数器暨相位解码器170对检测时钟信号ckd进行采样,获得检测时钟信号ckd的细计数值ftdc<p:0>,同时获得了检测时钟信号ckd与细计数值ftdc<p:0>的多相时钟的相位关系,也就获得了第一组粗计数值ctdc0<n:0>和细计数值ftdc<p:0>的多相时钟的相位关系,由此我们可以通过改变最终粗计数值ctdc<n:0>的源时钟进行矫正,进而实现准确计数。如此一来,可避免亚稳态的发生,也就是说,避免因为激光信号ckd落在最终粗计数值ctdc<n:0>的跳变沿而导致测距错误。

[0018]

为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附图式,作详细说明如下。

附图说明

[0019]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0020]

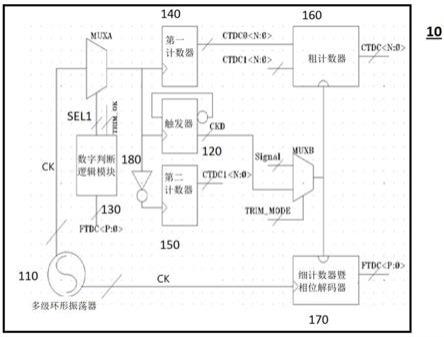

图1是本发明一实施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正装置的框架图。

[0021]

图2是本发明一实施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正方法的时序图。

[0022]

图3是本发明一实施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正方法的流程图。

具体实施方式

[0023]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0024]

需要说明的是,在本发明的描述中,术语“第一”、“第二”等仅用于描述目的和区别类似的对象,两者之间并不存在先后顺序,也不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

[0025]

请参考图1。图1是本发明一实施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正装置的框架图。如图1所示,矫正装置10包括:多级环形振荡器(multi-phase generator)110,用于生成具有多个相位的时钟信号 ck;触发器120,用于生成检测时钟信号ckd;第一多路复用器muxa,耦接于多级环形振荡器110,用于根据第一选择信号sel1来从时钟信号ck选择一个相位输出;数字判断逻辑模块130,耦接于第一多路复用器muxa,用于判断检测时钟信号ckd的当前细计数值ftdc<p:0>是否和基准值相同,当检测时钟信号ckd的当前细计数值ftdc<p:0>与基准值不等时,提供第一选择信号sel1给第一多路复用器muxa来控制第一多路复用器muxa选择下一个相位的时钟信号ck进入下一级;第一计数器140,耦接于第一多路复用器muxa,用于生成第一组粗计数值ctdc0<n:0>;第二计数器150,用于生成第二组粗计数值ctdc1<n:0>;第二多路复用器muxb,用于根据信号trim_mode来从激光信号signal选择一个输出;粗计数器(ctdc)160,用于从第一组粗计数值ctdc0<n:0>和第二组粗计数值crdc1<n:0>中正确选出一组最终粗计数值ctdc<n:0>;细计数器暨相位解码器(ftdc & phase decoder)170,用于将粗计数周期分为多个细计数周期,并将相位信号转化为计数值,来生成细计数值ftdc<p:0>。

[0026]

请注意,检测时钟ckd和第一组粗计数值ctdc0<n:0>的相位相同或者确定相位关系。

[0027]

进一步地,矫正装置10还包括:反相器180,用于将第一组粗计数值ctdc0<n:0>进行反相以生成所述第二组粗计数值ctdc1<n:0>。换句话说,第一组粗计数值ctdc0<n:0>和第二组粗计数值ctdc1<n:0>为两组正交错位的计数值。请一并参考图2。图2是本发明一实

施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正方法的时序图。如图2所示,第二组粗计数值ctdc1<n:0>比第一组粗计数值ctdc0<n:0>要延迟半个lsb。在本实施例中,ck0-ck7分别代表多级环形振荡器110生成的具有八个相位的时钟信号 ck,在具体应用中,也可以生成具有(n+1)个相位的时钟信号ck0到ckn,此并非本发明的限制条件。以具有第一个相位的时钟信号ck0为例,小号的数字0-7分别对应细计数器暨相位解码器170生成的细计数值ftdc<7:0>,也就是说,将一个粗计数值的lsb分为8份。

[0028]

请注意,激光信号ckd是测距时由物体反射回来的,激光信号ckd经过光电转换通过采样器得到两组粗计数时间值,即第一组粗计数值ctdc0<n:0>和第二组粗计数值ctdc1<n:0>,当返回的激光信号ckd落在第一字段zone_a时(如,小号的0, 1, 2, 3),则第二多路复用器选择第一组粗计数值ctdc0<n:0>输出;当返回的激光信号ckd落在第二字段zone_b时(如,小号的4, 5, 6, 7),则第二多路复用器选择第二组粗计数值ctdc1<n:0>输出。

[0029]

值得注意的是,时钟信号ck包括八个相位的时钟ck0-ck7,其中第一字段zone_a与第一个相位的时钟ck0的高电平时间重合,第二字段zone_b与第一个相位的时钟ck0的低电平时间重合,第一字段zone_a和第二字段zone_b组成一个周期。由此可以避免激光信号ckd落在最终粗计数值ctdc<n:0>的跳变沿,造成测距错误。由此可见,细计数值ftdc<p:0>的多相时钟的相位与最终粗计数值ctdc<n:0>的相位有着必须遵守的关系。最终粗计数值ctdc<n:0>的源时钟取自于细计数值ftdc<p:0>的多相时钟之一。由于多级环形振荡器110的时钟ck到粗计数器(ctdc)160生成最终粗计数值ctdc<n:0>的过程中会经过许多延迟,所以最终粗计数值ctdc<n:0>的相位与源时钟的相位关系未知,必须找到一种方法来确认最终粗计数值ctdc<n:0>和细计数值ftdc<p:0>的相位关系,才能实现准确计数。

[0030]

请参考图3。图3是本发明一实施例中的一种激光雷达的时间数字转换器避免亚稳态的矫正方法的流程图。该矫正方法包括以下步骤:步骤s1:利用触发器来生成检测时钟信号,其中检测时钟信号和第一组粗计数值的相位相同或者确定相位关系;步骤s2:打开矫正模式,并通过第二多路复用器来将检测时钟信号选通;步骤s3:利用细计数器暨相位解码器对检测时钟信号进行取样,来获得检测时钟信的细计数值;并将测时钟信号的当前细计数值输出到数字判断逻辑单元中与基准值进行比较,当检测时钟信号的当前细计数值与基准值不等时,提供第一选择信号给第一多路复用器来控制第一多路复用器选择下一个相位的时钟信号进入下一级;及步骤s4:重复步骤s3,直到检测时钟信号的当前细计数值与基准值相等,则矫正完成。

[0031]

请一并参考图1至图3。

[0032]

于步骤s1中,首先生成一个与第一组粗计数值ctdc0<n:0>同相位或者确定相位关系的检测时钟信号(或者检测脉冲信号)ckd。

[0033]

于步骤s2中,打开矫正模式trim mode,并通过第二多路复用器muxb来将检测时钟信号ckd选通。

[0034]

于步骤s3中,利用细计数器暨相位解码器170对检测时钟信号ckd进行取样,来获得检测时钟信ckd的细计数值ftdc0<p:0>;并将测时钟信号ckd的当前细计数值输出到数字判断逻辑单元130中与基准值进行比较,当检测时钟信号ckd的当前细计数值与基准值不等时,提供第一选择信号sel1给第一多路复用器muxa来控制第一多路复用器muxa选择下一个

相位的时钟信号进入下一级。

[0035]

于步骤s4中,重复步骤s3,直到检测时钟信号ckd的当前细计数值与基准值相等,则矫正完成。

[0036]

举例而言,首先选择第一个相位的时钟ck0,当检测时钟信号ckd的当前细计数值ftdc0<p:0>与基准值不等时,选择第二个相位的时钟ck1进入下一级。重复步骤s3,依序选择ck0、ck1、ck2

…

,直到检测时钟信号ckd的当前细计数值ftdc0<p:0>与基准值相等,则矫正完成。值得注意的是,当粗计数值ctdc0<n:0>和细计数值ftdc0<p:0>的相位关系是正确的,矫正状态位置trim_ok为1,退出矫正模式trim mode;若遍历全部相位ck0-ck7都不能成功,则矫正状态位置trim_ok为0,退出矫正模式trim mode。

[0037]

进一步地,步骤s1是由图1中的触发器120、反相器180、第一计数器140、第二计数器150、粗计数器(ctdc)160所完成。

[0038]

进一步地,步骤s3是由时间数字转换器130、细计数器暨相位解码器170、数字判断逻辑模块130、第一多路复用器muxa所完成。

[0039]

进一步地,细计数器暨相位解码器170由sa触发器、独热编码转二进制译码器组成。

[0040]

借由以上的技术方案,本发明的有益效果如下:本发明是一种自动选择最终粗计数值ctdc<n:0>的源时钟的矫正方法。通过本发明的矫正方法,生成一个与第一组粗计数值ctdc0<n:0>同相位的检测时钟信号ckd,他们的相位相同。将检测时钟信号ckd作为测距的返回激光信号使用,利用细计数器暨相位解码器170对检测时钟信号ckd进行采样,获得检测时钟信号ckd的细计数值ftdc<p:0>,同时获得了检测时钟信号ckd与细计数值ftdc<p:0>的多相时钟的相位关系,也就获得了第一组粗计数值ctdc0<n:0>和细计数值ftdc<p:0>的多相时钟的相位关系,由此我们可以通过改变最终粗计数值ctdc<n:0>的源时钟进行矫正,进而实现准确计数。如此一来,可避免亚稳态的发生,也就是说,避免因为激光信号ckd落在最终粗计数值ctdc<n:0>的跳变沿而导致测距错误。

[0041]

本发明中应用了具体实施例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1