一种基于模糊区脉冲检测的高精度异频数字锁相环系统的制作方法

1.本发明涉及锁相环技术领域,尤其涉及一种基于模糊区脉冲检测的高精度异频数字锁相环系统。

背景技术:

2.锁相环是一种相位同步控制系统,在电子通信、自动控制以及自动测量与检测等领域具有广泛应用。传统的锁相环建立在同频鉴相基础之上,被锁信号必须经过频率的归一化处理才能完成与频标信号之间的相位比对,频率的归一化处理需要经过复杂的频率变换过程,容易引入变换线路的附加噪声,最终使锁相环的同步精度难以保证。以异频鉴相为基础的锁相环建立在频标信号和被锁信号稳定频率关系基础之上,在复杂环境应用下当频标信号和被锁信号之间的频率关系复杂或存在大频率偏差时,脉冲鉴相输出的相位差信号不呈现规律性变化,最终使锁相系统的稳定性和可靠性变差。

技术实现要素:

3.本发明的目的在于提供一种基于模糊区脉冲检测的高精度异频数字锁相环系统,采用模糊区脉冲检测技术,能够大幅度提高锁相环的同步精度和相位差测量的分辨率,加强系统的稳定性和可靠性。

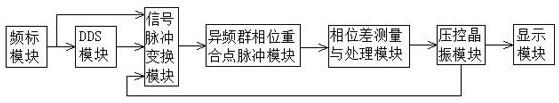

4.为了实现上述目的,本发明采用以下技术方案:一种基于模糊区脉冲检测的高精度异频数字锁相环系统,包括频标模块、dds模块、信号脉冲变换模块、异频群相位重合点脉冲模块、相位差测量与处理模块、压控晶振模块、显示模块和电源模块;频标模块的信号输出端分别连接dds模块的信号输入端和信号脉冲变换模块的信号输入端,dds模块的信号输出端连接信号脉冲变换模块的信号输入端,信号脉冲变换模块的信号输出端连接异频群相位重合点脉冲模块的信号输入端,异频群相位重合点脉冲模块的信号输出端连接相位差测量与处理模块的信号输入端,相位差测量与处理模块的信号输出端连接压控晶振模块的信号输入端,压控晶振模块的信号输出端分别连接信号脉冲变换模块的信号输入端和显示模块的信号输入端;所述的频标模块,用以提供锁定晶体振荡器的10mhz频标信号;所述的dds模块,用以产生与频标信号和晶体振荡器信号进行相位重合的辅助信号;所述的信号脉冲变换模块,用以产生脉冲信号;所述的异频群相位重合点脉冲模块,用以产生频标信号和辅助信号之间的群相位重合点脉冲信号以及辅助信号与晶体振荡器信号之间的群相位重合点脉冲信号;所述的相位差测量与处理模块,用以获得频标信号和晶体振荡器信号之间的相位差值并产生晶体振荡器的压控信号;所述的压控晶体振荡器模块,用以产生晶体振荡器信号即被锁信号;所述的显示模块,用于接收晶体振荡器信号频率即锁相环信号并显示。

5.所述的频标模块采用频率准确度

±5×

10

‑

13

的microsemi 5071a铯原子钟。

6.所述的dds模块采用dds芯片ad9854。

7.所述的信号脉冲变换模块由第一信号调理电路、第二信号调理电路和第三信号调理电路组成;具体的:第一信号调理电路、第二信号调理电路和第三信号调理电路均采用信号调理电路,所述的信号调理电路由施密特触发器74ls14d和反相器74ls04d组成,施密特触发器74ls14d的信号输入端作为信号调理电路的信号输入端,施密特触发器74ls14d的信号输出端与反相器74ls04d的信号输入端连接,反相器74ls04d组成的信号输出端作为信号调理电路的信号输出端;第一信号调理电路的信号输入端连接microsemi 5071a铯原子钟的信号输出端,用于将频标信号送入第一信号调理电路产生频标脉冲信号;第二信号调理电路的信号输入端连接dds模块的信号输出端,用于将辅助信号送入第二信号调理电路产生辅助脉冲信号;第三信号调理电路的信号输入端连接压控晶体振荡器模块的信号输出端,用于将晶体振荡器信号送入第三信号调理电路产生晶体振荡器脉冲信号。

8.所述的异频群相位重合点脉冲模块由移相电路、第一模糊区脉冲产生电路和第二模糊区脉冲产生电路组成;具体的:所述的移相电路采用第一边沿型d触发器74ls175n,第一边沿型d触发器74ls175n的信号输入端连接第二信号调理电路的信号输出端,用于对辅助脉冲信号进行移相;所述的第一模糊区脉冲产生电路由第二边沿型d触发器74ls175n、第一逻辑非门电路74ls04n、第二逻辑非门电路74ls04n、第一2输入逻辑与门电路74ls08n、第二2输入逻辑与门电路74ls08n和第一3输入逻辑与门电路74ls11n组成,第二边沿型d触发器74ls175n的信号输入端d1、第一逻辑非门电路74ls04n的信号输入端和第一2输入逻辑与门电路74ls08n的信号输入端a1军连接第二信号调理电路的信号输出端,第一逻辑非门电路74ls04n的信号输出端连接第一2输入逻辑与门电路74ls08n的信号输入端b1,第一边沿型d触发器74ls175n的时钟端ck1、第二逻辑非门电路74ls04n的信号输入端和第二2输入逻辑与门电路74ls08n的信号输入端a2均连接第一信号调理电路的信号输出端,第二逻辑非门电路74ls04n的信号输出端连接第二2输入逻辑与门电路74ls08n的信号输入端b2,第一2输入逻辑与门电路74ls08n的信号输出端y1、第二2输入逻辑与门电路74ls08n的信号输出端y2和第二边沿型d触发器74ls175n的输出端q1分别连接第一3输入逻辑与门电路74ls11n的信号输入端;将移相后的辅助脉冲信号和频标脉冲信号均送入第一模糊区脉冲产生电路,在第一3输入逻辑与门电路74ls11n的信号输出端获得移相后的辅助脉冲信号和频标脉冲信号之间的第一模糊区脉冲信号,第一模糊区脉冲信号作为相位差测量与处理模块中计数器闸门的开门信号;第二模糊区脉冲产生电路由第三边沿型d触发器74ls175n、第三逻辑非门电路74ls04n、第四逻辑非门电路74ls04n、第三2输入逻辑与门电路74ls08n、第四2输入逻辑与门电路74ls08n和第二3输入逻辑与门电路74ls11n组成,第三边沿型d触发器74ls175n的信号输入端d2、第三逻辑非门电路74ls04n的信号输入端和第三2输入逻辑与门电路74ls08n的信号输入端a3均连接第二信号调理电路的信号输出端,第四逻辑非门电路74ls04n的信

号输出端连接第四2输入逻辑与门电路74ls08n的信号输入端b4,第三边沿型d触发器74ls175n的时钟端ck1、第四逻辑非门电路74ls04n的信号输入端和第四2输入逻辑与门电路74ls08n的信号输入端a4均连接第三信号调理电路的信号输出端,第四逻辑非门电路74ls04n的信号输出端连接第四2输入逻辑与门电路74ls08n的信号输入端b4,第三2输入逻辑与门电路74ls08n的信号输出端y3、第四2输入逻辑与门电路74ls08n的信号输出端y4和第三边沿型d触发器74ls175n的输出端q2均连接第二3输入逻辑与门电路74ls11n的信号输入端;将移相后的辅助脉冲信号和晶体振荡器脉冲信号均送入第二模糊区脉冲产生电路,在第二3输入逻辑与门电路74ls11n的信号输出端获得移相后的辅助脉冲信号和晶体振荡器脉冲信号之间的第二模糊区脉冲信号,第二模糊区脉冲信号作为相位差测量与处理模块中计数器闸门的关门信号。

9.所述的相位差测量与处理模块由可编程分频器、可编程计数器和单片机组成,用以获得频标信号和晶体振荡器信号之间的相位差值并产生压控晶体振荡器模块的压控信号。

10.所述的压控晶体振荡器模块采用kds 19.2mhz dsa535sd 晶体振荡器,用以接收压控信号并调节晶体振荡器的被锁信号频率。

11.所述的显示模块采用lcd液晶显示器。

12.所述的施密特触发器74ls14d、反相器74ls04d、第一边沿型d触发器74ls175n、第二边沿型d触发器74ls175n、第三边沿型d触发器74ls175n、第一逻辑非门电路74ls04n、第二逻辑非门电路74ls04n、第一2输入逻辑与门电路74ls08n、第二2输入逻辑与门电路74ls08n和第一3输入逻辑与门电路74ls11n、第三逻辑非门电路74ls04n、第四逻辑非门电路74ls04n、第三2输入逻辑与门电路74ls08n、第四2输入逻辑与门电路74ls08n和第二3输入逻辑与门电路74ls11n以及可编程分频器、可编程计数器和单片机均可由fpga实现,所述的fpga采用cyclone iv芯片ep4ce75。

13.与现有技术相比,本发明的有益效果为:相对于现有的高精度锁相环,本发明无需鉴相器,采用模糊区脉冲检测方法使相位差测量的分辨率得到了极大提高,任意时刻的相位差测量分辨率优于1ps,大幅度提高了锁相环的同步精度,利用fpga技术使系统结构集成化,降低了开发成本,抑制了相位噪声,加强了系统的稳定性和可靠性。

附图说明

14.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

15.图1为本发明所述的基于模糊区脉冲检测的高精度异频数字锁相环系统的原理框图。

具体实施方式

16.下面将结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.如图1所示,本发明所述的基于模糊区脉冲检测的高精度异频数字锁相环系统,包括频标模块、dds模块、信号脉冲变换模块、异频群相位重合点脉冲模块、相位差测量与处理模块、压控晶振模块、显示模块和电源模块;所述的电源模块用于为频标模块、dds模块、信号脉冲变换模块、异频群相位重合点脉冲模块、相位差测量与处理模块、压控晶振模块和显示模块供电;频标模块的信号输出端分别连接dds模块的信号输入端和信号脉冲变换模块的信号输入端,dds模块的信号输出端连接信号脉冲变换模块的信号输入端,信号脉冲变换模块的信号输出端连接异频群相位重合点脉冲模块的信号输入端,异频群相位重合点脉冲模块的信号输出端连接相位差测量与处理模块的信号输入端,相位差测量与处理模块的信号输出端连接压控晶振模块的信号输入端,压控晶振模块的信号输出端分别连接信号脉冲变换模块的信号输入端和显示模块的信号输入端。

18.所述的频标模块采用microsemi 5071a铯原子钟,频率准确度

±5×

10

‑

13

,用以提供锁定晶体振荡器信号的10mhz频标信号;所述的晶体振荡器信号由所述的压控晶振模块提供。

19.所述的dds模块采用dds芯片ad9854,以10mhz频标信号作为dds芯片ad9854的外部时钟信号,用于在fpga的控制下产生与频标信号和晶体振荡器信号进行相位重合的辅助信号。

20.所述的信号脉冲变换模块由第一信号调理电路、第二信号调理电路和第三信号调理电路组成,具体的:所述的第一信号调理电路、第二信号调理电路和第三信号调理电路均采用信号调理电路,所述的信号调理电路由施密特触发器74ls14d和反相器74ls04d组成,施密特触发器74ls14d的信号输入端作为信号调理电路的信号输入端,施密特触发器74ls14d的信号输出端与反相器74ls04d的信号输入端连接,反相器74ls04d组成的信号输出端作为信号调理电路的信号输出端;第一信号调理电路的信号输入端连接microsemi 5071a铯原子钟的信号输出端,用于将频标信号送入第一信号调理电路产生频标脉冲信号;第二信号调理电路的信号输入端连接dds模块的信号输出端,用于将辅助信号送入第二信号调理电路产生辅助脉冲信号;第三信号调理电路的信号输入端连接压控晶体振荡器模块的信号输出端,用于将晶体振荡器信号送入第三信号调理电路产生晶体振荡器脉冲信号。

21.所述的异频群相位重合点脉冲模块由移相电路、第一模糊区脉冲产生电路和第二模糊区脉冲产生电路组成;具体的:所述的移相电路采用第一边沿型d触发器74ls175n,第一边沿型d触发器74ls175n的信号输入端连接第二信号调理电路的信号输出端,用于对辅助脉冲信号进行移相;具体的:移相量的大小由第一边沿型d触发器74ls175n的时钟周期决定,通过调节第一边沿型d触发器74ls175n的时钟频率改变移相量的大小,进而获得移相后的辅助脉冲信号,第一边沿型d触发器74ls175n能够将频标脉冲信号与辅助脉冲信号之间模糊区脉冲信号以及晶体

振荡器脉冲信号与辅助脉冲信号之间模糊区脉冲信号的被动生成变为主动检测,进而大幅度提高群相位重合点检测的速度和系统的响应时间;所述的第一模糊区脉冲产生电路由第二边沿型d触发器74ls175n、第一逻辑非门电路74ls04n、第二逻辑非门电路74ls04n、第一2输入逻辑与门电路74ls08n、第二2输入逻辑与门电路74ls08n和第一3输入逻辑与门电路74ls11n组成,第二边沿型d触发器74ls175n的信号输入端d1、第一逻辑非门电路74ls04n的信号输入端和第一2输入逻辑与门电路74ls08n的信号输入端a1军连接第二信号调理电路的信号输出端,第一逻辑非门电路74ls04n的信号输出端连接第一2输入逻辑与门电路74ls08n的信号输入端b1,第一边沿型d触发器74ls175n的时钟端ck1、第二逻辑非门电路74ls04n的信号输入端和第二2输入逻辑与门电路74ls08n的信号输入端a2均连接第一信号调理电路的信号输出端,第二逻辑非门电路74ls04n的信号输出端连接第二2输入逻辑与门电路74ls08n的信号输入端b2,第一2输入逻辑与门电路74ls08n的信号输出端y1、第二2输入逻辑与门电路74ls08n的信号输出端y2和第二边沿型d触发器74ls175n的输出端q1分别连接第一3输入逻辑与门电路74ls11n的信号输入端;将移相后的辅助脉冲信号和频标脉冲信号均送入第一模糊区脉冲产生电路,在第一3输入逻辑与门电路74ls11n的信号输出端获得移相后的辅助脉冲信号和频标脉冲信号之间的第一模糊区脉冲信号,第一模糊区脉冲信号作为相位差测量与处理模块中计数器闸门的开门信号;第二模糊区脉冲产生电路由第三边沿型d触发器74ls175n、第三逻辑非门电路74ls04n、第四逻辑非门电路74ls04n、第三2输入逻辑与门电路74ls08n、第四2输入逻辑与门电路74ls08n和第二3输入逻辑与门电路74ls11n组成,第三边沿型d触发器74ls175n的信号输入端d2、第三逻辑非门电路74ls04n的信号输入端和第三2输入逻辑与门电路74ls08n的信号输入端a3均连接第二信号调理电路的信号输出端,第四逻辑非门电路74ls04n的信号输出端连接第四2输入逻辑与门电路74ls08n的信号输入端b4,第三边沿型d触发器74ls175n的时钟端ck1、第四逻辑非门电路74ls04n的信号输入端和第四2输入逻辑与门电路74ls08n的信号输入端a4均连接第三信号调理电路的信号输出端,第四逻辑非门电路74ls04n的信号输出端连接第四2输入逻辑与门电路74ls08n的信号输入端b4,第三2输入逻辑与门电路74ls08n的信号输出端y3、第四2输入逻辑与门电路74ls08n的信号输出端y4和第三边沿型d触发器74ls175n的输出端q2均连接第二3输入逻辑与门电路74ls11n的信号输入端;将移相后的辅助脉冲信号和晶体振荡器脉冲信号均送入第二模糊区脉冲产生电路,在第二3输入逻辑与门电路74ls11n的信号输出端获得移相后的辅助脉冲信号和晶体振荡器脉冲信号之间的第二模糊区脉冲信号,第二模糊区脉冲信号作为相位差测量与处理模块中计数器闸门的关门信号。

22.模糊区脉冲检测方法的原理是具有任意频率关系的两比对信号在经过频标信号的连续时延后送入异频相位重合检测电路进行异频群量子化相位处理产生模糊区脉冲,由于异频群量子化相位处理以最大公因子周期为基础具有优于ps量级的测量分辨率,所有低于系统检测分辨率的相位差脉冲因不能被系统检测器件分辨而输出一簇相位差脉冲形成模糊区脉冲,模糊区脉冲宽度因时延缩短减少了模糊区变化的随机性以及模糊区生成的被

动性,模糊区边沿脉冲作为闸门开关信号消除了因检测器件的不一致和不匹配性所带来的硬件误差,进而使系统在较低的检测分辨率下获得较高的测量精度。

23.所述的相位差测量与处理模块由可编程分频器、可编程计数器和单片机组成,用以获得频标信号和晶体振荡器信号之间的相位差值并产生晶体振荡器的压控信号;具体的:可编程分频器由fpga硬件描述语言编程实现,用以提供参考闸门信号,在参考闸门信号控制下第一模糊区脉冲信号和第二模糊区脉冲信号形成实际闸门信号;可编程计数器由fpga硬件描述语言编程实现,用以在实际闸门时间内对辅助脉冲信号进行脉冲计数,获得计数值;单片机由fpga内部的单片机功能实现,用以处理可编程计数器的计数值和计算相位差值,并产生晶体振荡器的压控信号;相位差值计算的过程如下:将第一模糊区脉冲信号和第二模糊区脉冲信号送入可编程计数器,在参考闸门控制下,第一模糊区脉冲信号为可编程计数器的开门信号,第二模糊区脉冲信号为可编程计数器的关门信号,在开门信号和关门信号之间的时间间隔(实际闸门时间)内对辅助脉冲标信号进行无间隙脉冲计数并获得脉冲计数值,然后经过单片机计算和处理产生相位差值。

24.所述的压控晶体振荡器模块采用kds 19.2mhz dsa535sd 晶体振荡器,用以接收相位差测量与处理模块的压控信号并实时调节kds 19.2mhz dsa535sd晶体振荡器的被锁信号频率,最终达到频标信号和被锁信号之间的同步。

25.所述的显示模块,由lcd液晶显示器组成,用于接收晶体振荡器信号频率即锁相环信号并显示。

26.进一步的,所述的施密特触发器74ls14d、反相器74ls04d、第一边沿型d触发器74ls175n、第二边沿型d触发器74ls175n、第三边沿型d触发器74ls175n、第一逻辑非门电路74ls04n、第二逻辑非门电路74ls04n、第一2输入逻辑与门电路74ls08n、第二2输入逻辑与门电路74ls08n和第一3输入逻辑与门电路74ls11n、第三逻辑非门电路74ls04n、第四逻辑非门电路74ls04n、第三2输入逻辑与门电路74ls08n、第四2输入逻辑与门电路74ls08n和第二3输入逻辑与门电路74ls11n均可用fpga实现,所述的fpga采用cyclone iv芯片ep4ce75,利用fpga技术使系统结构集成化,降低了开发成本,抑制了相位噪声,加强了系统的稳定性和可靠性。

27.本发明的有益效果为:本发明所述的基于模糊区脉冲检测的高精度异频数字锁相环系统,与传统的异频数字锁相环系统相比:传统的异频数字锁相环建立在同频相位比对基础之上,被锁信号必须经过频率的归一化处理才能完成与频标信号之间的鉴相,频率的归一化处理影响了锁相环系统的同步精度,而以异频鉴相为基础的锁相环在复杂环境应用下因鉴相输出信号的不规律性,降低了锁相环系统的稳定性和可靠性;相对于现有的高精度锁相环,本发明无需鉴相器,采用模糊区脉冲检测方法使相位差测量的分辨率得到了极大提高,任意时刻的相位差测量分辨率优于1ps,大幅度提高了锁相环的同步精度,利用fpga技术使系统结构集成化,降低了开发成本,抑制了相位噪声,加强了系统的稳定性和可靠性。

28.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽

管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1