一种基带信号处理板的制作方法

1.本实用新型涉及信号处理技术领域,尤其涉及一种基带信号处理板。

背景技术:

2.信号处理板主要用于对接收的信号进行处理,而现有的信号处理设备其采样能力和发射能力都相对较低,且多通道之间的同步精度不高,数据传输效率低下,因此,如何解决这些问题是目前需要考虑的。

技术实现要素:

3.本实用新型的目的在于克服现有技术的缺点,提供一种基带信号处理板,解决了现有技术存在的问题。

4.本实用新型的目的通过以下技术方案来实现:一种基带信号处理板,它包括第一fpga、第二fpga、下行接收通道、上行发送通道、时钟模块、外部参考时钟、本地时钟、dds模块、话音模块和电源模块;所述第一fpga和第二fpga相互连接;所述下行接收通道通过串行/解串器接口与所述第一fpga相互连接,所述上行发送通道通过串行/解串器接口与所述第二fpga相互连接;所述第二fpga的输出端与所述dds模块和话音模块的输入端连接;所述本地时钟和外部参考时钟的输出端与所述时钟模块的输入端连接,所述时钟模块的输出端与所述下行接收通道、上行发送通道、第一fpga和第二fpga的时钟信号输入端连接;所述电源模块的供电输出端与所述下行接收通道、上行发送通道、第一fpga和第二fpga的供电输入端连接。

5.所述下行接收通道包括8个单通道的ad芯片,每个ad芯片通过串行/解串器接口与所述第一fpga相互连接;所述上行发送通道包括4个双通道的da芯片,每个da芯片通过串行/解串器接口与所述第二fpga相互连接。

6.所述时钟模块包括模拟时钟单元和数字时钟单元;所述时钟模块和外部参考时钟的输出端与所述模拟时钟单元的输入端连接,模拟时钟单元的时钟信号输出端与所述下行接收通道、上行发送通道、第一fpga和第二fpga的时钟信号输入端连接;所述数字时钟单元的时钟信号输出端与第一fpga和第二fpga的时钟信号输入端连接。

7.所述模拟时钟单元包括时钟选择器、时钟分配器、时钟调节器、宽带合成器组件以及时钟缓冲器组件;所述外部参考时钟和本地时钟的输出端与所述时钟选择器的输入端连接,时钟选择器的输出端与时钟分配器的输入端连接;时钟分配器的输出端与时钟调节器的输入端连接,并输出两路100mhz时钟信号;所述时钟调节器的输出端分别与宽带合成器组件和时钟缓冲器组件的输入端连接;宽带合成器组件的时钟信号输出端与下行接收通道和上行发送通道的时钟信号输入端连接;所述时钟缓冲器组件的时钟信号输出端与第一fpga和第二fpga的时钟信号输入端连接;所述时钟调节器的输出端还与第一fpga的输入端连接。

8.所述宽带合成器组件包括6个宽带合成器,每个宽带合成器的时钟信号输出端与

两个ad芯片或者da芯片的时钟信号输入端连接;所述时钟缓冲器组件包括4个时钟缓冲器,每两个时钟缓冲器的时钟信号输出端与第一fpga或者第二fpga的时钟信号输入端连接。

9.所述数字时钟单元包括时钟发生器和两个时钟缓冲器,数字时钟单元输出两路时钟信号到两个时钟缓冲器,两个时钟缓冲器的时钟信号输出端均与第一fpga和第二fpga的时钟信号输入端连接。

10.所述电源模块包括12v电源、多个降压调节器和多个低压差稳压器;所述12v电源的输出端与多个降压调节器的输入端连接,其中一个降压调节器通过一个低压差稳压器与一个ad芯片或者da芯片连接,剩余降压调节器的输出端输出不同电压与第一fpga和第二fpga的供电输入端连接。

11.还包括与第二fpga连接的lvttl接口、lvds接口、串行/解串器接口、以太网接口、光纤接口、gps接口和jtag调试接口。

12.本实用新型具有以下优点:一种基带信号处理板,集成了8通道的高速大带宽ad和8通道da,其采用的高速信号中频采样能力和高速大带宽中频发射能力得到了极大地提高,也提高了8通道高速ad片间的高度同步功能的能力。通过rapidio,pcie,光纤,lvds等专用高速接口以及千兆以太网,rs422和gps等常规通用接口既能够适用于专用协议的高速数据传输,也能够适用于外部通用设备的数据交互。

附图说明

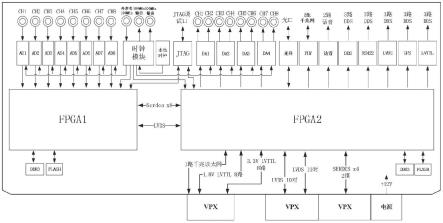

13.图1为本实用新型的结构示意图;

14.图2为模拟时钟单元的电路原理示意图;

15.图3为数字时钟单元的电路原理示意图;

16.图4为电源模块的电路原理示意图;

17.图5为dds模块的连接示意图;

18.图6为lvds接口的连接示意图;

19.图7为lvttl接口的连接示意图。

具体实施方式

20.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。因此,以下结合附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的保护范围,而是仅仅表示本技术的选定实施例。基于本技术的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。下面结合附图对本实用新型做进一步的描述。

21.如图1所示,一种基带信号处理板,它包括第一fpga(fpga1)、第二fpga(fpga2)、下行接收通道、上行发送通道、时钟模块、外部参考时钟、本地时钟、dds模块、话音模块和电源模块;所述第一fpga和第二fpga相互连接;所述下行接收通道通过串行/解串器接口与所述第一fpga相互连接,所述上行发送通道通过串行/解串器接口与所述第二fpga相互连接;所

述第二fpga的输出端与所述dds模块和话音模块的输入端连接;所述本地时钟和外部参考时钟的输出端与所述时钟模块的输入端连接,所述时钟模块的输出端与所述下行接收通道、上行发送通道、第一fpga和第二fpga的时钟信号输入端连接;所述电源模块的供电输出端与所述下行接收通道、上行发送通道、第一fpga和第二fpga的供电输入端连接。

22.进一步地,fpga1和fpga2均采用型号为xc7v690t,xc7v690t-ffg1927型号具有80组serdes高速串行总线(最高线速率13.1gb/s),600路io口,52920kbits block ram,3600个dsp48e1 slices,693120logic cells,能够满足基带处理板的要求。fpga上集成了80路gth高速串行口,串行口的线速率根据不同型号有不同的选择;基带处理板上挂载64位ddr3高速缓存,根据fpga的io口传输速率,根据所选择型号xc7v690t-2ffg1927i,ddr3最高工作速率1600mb/s。

23.所述下行接收通道包括8个单通道的ad芯片,每个ad芯片通过串行/解串器接口与所述第一fpga相互连接;所述上行发送通道包括4个双通道的da芯片,每个da芯片通过串行/解串器接口与所述第二fpga相互连接。

24.进一步地,ad芯片采用的型号为adc12j4000,其为宽带采样和数字调谐器件,支持采用射频直接对大范围频谱采样。集成ddc(数字下变频器)可进行数字滤波和下变频转换。所选频率块适用于jesd204b串行接口。数据以基带15位复数信息形式输出,以减轻下游处理压力。根据数字下变频器(ddc)抽取率和链接输出率设置,该数据将通过串行接口的1至5通道输出。ddc旁路模式还支持输出全速率12位原始adc数据。此运行模式需要8个串行输出通道。da芯片采用的型号为ad9172,其是一款支持12.6gsps的dac采样速率的高性能双通道16位数模转换器(dac)。该器件采用8线15gbps jesd204b数据输入端口、高性能片内dac时钟倍频器和数字信号处理功能,适用于单频段和多频段直接到射频(rf)无线应用场合。每个rf dac具有3个可旁路复用数据输入通道。每个数据输入通道包括可配置的增益级、内插滤波器和用于灵活的多频段规划的通道数控振荡器(nco)。该器件支持每个输入通道高达1.5gsps的复用数据速率,并能够聚合多个复用输入数据流,最大复用数据速率高达1.5gsps。此外,ad9172支持超宽带模式,绕过信道选择器以提供高达3.08gsps(16位分辨率)和4.1gsps(12位分辨率)的最大数据速率。

25.本实用新型可选择的ad能够满足要求的芯片最少需要8组serdes/片,8路ad则总共需要64路serdes(串行/解串器接口);而da有每片双通道能满足要求的芯片,总共需要4片芯片,最少需要32组serdes;8路ad和8路da加起来就需要至少96组serdes(ad 8组单通道,da4组双通道),此外fpga还要引出serdes和光纤接口,所有serdes加起来最少也需要108组serdes,因此一个fpga的serdes数量都达不到这么多,需要采用两片fpga进行才能实现。

26.fpga1挂载8路ad,fpga2挂载8路da,两片fpga之间由serdes x8和lvds(低电压差分信号)互联传输数据和命令;fpga1由于ad使用了64路serdes,加上8路互联serdes,总量已经使用72路serdes,而fpga2的da使用32路serdes,加上8路互联serdes,总量使用40路serdes,fpga2的剩余高速串行接口比fpga1要多,因此本实用新型全部的对外接口从fpga2引出,fpga1只用来采集8路ad信号。

27.所述时钟模块包括模拟时钟单元和数字时钟单元;所述时钟模块和外部参考时钟的输出端与所述模拟时钟单元的输入端连接,模拟时钟单元的时钟信号输出端与所述下行

接收通道、上行发送通道、第一fpga和第二fpga的时钟信号输入端连接;所述数字时钟单元的时钟信号输出端与第一fpga和第二fpga的时钟信号输入端连接。

28.如图2所示,模拟时钟单元包括时钟选择器(hmc849alp4ce)、时钟分配器(adclk944)、时钟调节器(lmk04828)、宽带合成器组件以及时钟缓冲器组件;所述外部参考时钟和本地时钟的输出端与所述时钟选择器的输入端连接,时钟选择器的输出端与时钟分配器的输入端连接;时钟分配器的输出端与时钟调节器的输入端连接,并输出两路100mhz时钟信号;所述时钟调节器的输出端分别与宽带合成器组件和时钟缓冲器组件的输入端连接;宽带合成器组件的时钟信号输出端与下行接收通道和上行发送通道的时钟信号输入端连接;所述时钟缓冲器组件的时钟信号输出端与第一fpga和第二fpga的时钟信号输入端连接;所述时钟调节器的输出端还与第一fpga的输入端连接。

29.所述宽带合成器组件包括6个宽带合成器(lmk2820),每个宽带合成器的时钟信号输出端与两个ad芯片或者da芯片的时钟信号输入端连接;所述时钟缓冲器组件包括4个时钟缓冲器,每两个时钟缓冲器(lmk00304)的时钟信号输出端与第一fpga或者第二fpga的时钟信号输入端连接。

30.本实用新型的模拟时钟需要支持外参考100mhz输入,同时也支持本地100mhz时钟工作,此外,还需要输出两路100mhz时钟;处理板上的外参考和本地时钟可切换输入,输入后的时钟经过时钟锁相环芯片分别输出到8片ad和4片da芯片以及两片fpga。由于ad和da总量较多,需要选择通道数多的时钟芯片,以便减少板上布局压力;基带处理板上包含了8片adc12j4000,4片ad9172和两片fpga,需要的时钟路数非常多,每片ad和da需要1路工作时钟1路参考时钟;本实用新型上在前端使用一片时钟二选一选择芯片,可以选择外参考或本地时钟工作,时钟选择芯片输出到一片adclk944,该芯片可以输出4路信号,其中两路输出到板外,另外一路输出给lmk04828;

31.lmk04828提供了7路工作时钟输出和7路参考时钟输出,此时钟芯片最大工作频率3080mhz,而ad最大采样率在4gsps,da最大采样率6gsps,时钟频率不够,且通道数量也不够,因此选用一片lmk2820将时钟倍频后输出给ad和da,lmk2820可以输出两路工作时钟和两路参考时钟,输出时钟最高频率可达22.6ghz,能够满足要求;

32.两片fpga还需要提供给serdes时钟以及io口工作时钟,板上采用4片lmk00304,每片可以输出4路时钟,分别提供8路到fpga1和fpga2,lmk04828剩余的参考时钟则输入给fpga1。

33.如图3所示,数字时钟单元包括时钟发生器和两个时钟缓冲器,数字时钟单元输出两路时钟信号到两个时钟缓冲器,两个时钟缓冲器的时钟信号输出端均与第一fpga和第二fpga的时钟信号输入端连接。

34.基带处理板数字时钟采用一片idt公司的844n255时钟发生器产生一路100mhz时钟和一路156.25mhz时钟;100mhz时钟输入到一片cdclvd1204时钟buffer,输出4路100mhz时钟分别输出给fpga1和fpga2各两路,用于io接口工作时钟;156.25mhz时钟输入到一片cdclvd1208时钟buffer(缓冲器),输出8路156.25mhz分别输出给fpga1和fpga2各四路,用于serdes高速接口提供时钟。

35.如图4所示,电源模块包括12v电源、多个降压调节器和多个低压差稳压器;所述12v电源的输出端与多个降压调节器的输入端连接,其中一个降压调节器通过一个低压差

稳压器与一个ad芯片或者da芯片连接,剩余降压调节器的输出端输出不同电压与第一fpga和第二fpga的供电输入端连接。

36.xc7v690t的内核电源供应1.0v,外部电源主要为1.2v,1.5v(ddr3),1.8v,vcc_aux_io电源根据ddr3速率选择供电电压,根据速率要求,在配置更改工作速率是此电源需要供应2.0v工作电压,而在没有更高要求的情况下,只需供应1.8v电源即可。

37.基带处理板电源整板由数字部分和模拟部分组成,因此数字部分采用dcdc开关电源提供,模拟部分采用ldo线性电源提供,根据不同电流大小选择对应供电电流的电源芯片。处理板上功耗大的主要有fpga内核电源,8片ad内核电源和4片da内核电源,这些内核电源需要用大电流的dcdc电源供电,这几种电源使用linear公司的ltm4678,该芯片提供两项电源输出,每项输出电流25a;电流小一些的采用ltm4644提供,ltm4644提供4项电源,每项4a,四项电源可以任意组合,四项组合最大可输出16a电流;模拟部分采用ldo电源,ldo电源采用低噪声输出芯片,控制供电底噪,主要采用型号tps7a8500,电流从2a到4a不等。

38.进一步地,如图5所示,dds模块包括三片ad9914,ad9914是一款直接数字频率合成器(dds),内置一个12位数模转换器,目标工作速率最高达3.5gsps。采用先进的dds技术,连同高速、高性能数模转换器,构成数字可编程的完整高频合成器,能够产生最高1.4ghz的频率捷变模拟输出正弦波。ad9914专为提供快速跳频和精密调谐分辨率(标准模式下32位、可编程模数模式下64位)而设计。实现了快速相位与幅度跳频功能。频率调谐和控制字通过串行或并行i/o端口载入ad9914。支持在用户定义线性扫描模式下工作,可产生频率、相位或幅度的高度线性扫描波形。另外集成了一个高速并行数据输入端口,可支持极性调制方案的高数据率以及相位、频率和幅度调谐字的快速编程。

39.进一步地,话音模块采用pcm3070芯片,pcm3070是一款灵活的立体声音频编解码器,配有可编程输入和输出、完全可编程minidsp、固定式预定义和可参数化信号处理块、集成式pll、集成式ldo以及灵活的数字接口。

40.还包括与第二fpga连接的lvttl接口、lvds接口、串行/解串器接口、以太网接口、光纤接口、gps接口和jtag调试接口。

41.如图6所示,信号处理板的lvds接口包含了两部分,一部分是到vpx的lvds信号线,一部分通过lvds专用收发器件引出到面板的总线;lvds分成两部分输出,输出到vpx的两组lvds信号从fpga的io管脚直接引出,每组10对,其中两对连接到fpga的全局时钟管脚上;40对lvds收发数据接口,需要外接lvds收发器,从fpga的io引出信号到发射芯片sn65lvds31d和接收芯片sn65lvds32d,然后从收发器将lvds引出到面板连接器。

42.如图7所示,信号处理板上的lvttl分为两部分引出,一部分引出到vpx座子与背板互联,另外一部分引出到前面板,lvttl引出到vpx连接器,3.3v与1.8v电平各8路,采用txs0108e芯片隔离,该芯片支持双向io模式,无需配置运行方向,此外,该芯片输入输出可接不同的电压,能够作为电平转换芯片使用;输出到面板的20路lvttl,由于要引线到板外,因此需要具备较强的驱动能力,采用sn74avch8t245作为驱动器,同时具有隔离的作用,该芯片需要配置输入输出方向。

43.本实用新型需要3路千兆以太网,其中两路引出到前面板,剩余1路引到vpx背板,在fpga上直接挂在3片以太网phy,型号选择mavell的88e1111,通过88e1111引出3路千兆以太网。光纤接口采用qsfp+接口,直接从fpga2的serdes引出一组serdes x4到qsfp+,每路

serdes运行速率10gbps,4路serdes即可满足传输速率40gbps的要求。serdes接口除去ad和da使用之外,还有前面板的光口和vpx后出线口,以及fpga1和fpga2之间的互联。gps接口为1路串口收发和1路pps的lvttl电平接口,串口和pps接口均为+3.3v的lvttl电平接口,gps的收发和1pps均为+3.3v的lvttl电平,而fgpa的io为1.8v电平,因此采用了电平转换驱动器sn74avch2t45和sn74avch1t45进行电平转换,同时这两款芯片也具备驱动能力。

44.本实用新型的工作过程如下:fpga1挂载8路高速ad,从外部输入8路高速大带宽的信号经过adc模数转换,数据传输给fpga1用于信号解调,并将数据传递给fpga2;fpga2挂载8路高速da和多种对外总线,fpga2从fpga1中获取ad数据,经过处理并以调制信号输出给da,从da进行发射。fpga2挂载的对外接口,可以将基带数据通过光纤或者lvds传出板外,rs422和千兆以太网可用于远程控制等功能。

45.以上所述仅是本实用新型的优选实施方式,应当理解本实用新型并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本实用新型的精神和范围,则都应在本实用新型所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1