显示屏变频方法、DDIC芯片、显示屏模组及终端与流程

显示屏变频方法、ddic芯片、显示屏模组及终端

技术领域

[0001]

本申请实施例涉及显示技术领域,特别涉及一种显示屏变频方法、显示驱动电路(display driver integrated circuit,ddic)、显示屏模组及终端。

背景技术:

[0002]

随着显示屏技术的不断发展,越来越多的高刷新率显示屏应运而生,在运行高帧率应用程序或在滑动操作过程中,通过将显示屏设置为高刷新率模式能够提高画面的流畅度。

[0003]

在一些应用场景下,高刷新率能够提高画面流畅度,优化用户体验,比如运行高帧率游戏时,高刷新率能够提高游戏画面流畅度;在一些无需用到高频刷新的场景中,依然采用高刷新率会带来功耗过高的问题。比如,在播放30fps的视频时,使用120hz的刷新率会造成过高功耗。

技术实现要素:

[0004]

本申请实施例提供了一种显示屏变频方法、ddic芯片、显示屏模组及终端。所述技术方案如下:

[0005]

一方面,本申请实施例提供了一种显示屏变频方法,所述方法用于显示屏的ddic芯片,所述方法包括:

[0006]

按照第一基础刷新率向应用处理器(application processor,ap)输出撕裂效应(tearing effect,te)信号,并按照所述第一基础刷新率进行图像扫描和帧补偿;

[0007]

接收所述ap下发的降频指令,所述降频指令用于指示下调所述显示屏的基础刷新率;

[0008]

根据所述降频指令,按照第二基础刷新率向所述ap输出te信号,并继续按照所述第一基础刷新率进行图像扫描和帧补偿,所述第二基础刷新率小于所述第一基础刷新率。

[0009]

另一方面,本申请实施例提供了一种ddic芯片,所述ddic芯片应用于显示屏,所述ddic芯片用于:

[0010]

按照第一基础刷新率向ap输出te信号,并按照所述第一基础刷新率进行图像扫描和帧补偿;

[0011]

接收所述ap下发的降频指令,所述降频指令用于指示下调所述显示屏的基础刷新率;

[0012]

根据所述降频指令,按照第二基础刷新率向所述ap输出te信号,并继续按照所述第一基础刷新率进行图像扫描和帧补偿,所述第二基础刷新率小于所述第一基础刷新率。

[0013]

另一方面,本申请实施例提供了一种显示屏模组,所述显示屏模组包括显示屏和ddic芯片,所述ddic芯片用于驱动所述显示屏,所述ddic芯片用于实现如上述方面所述的显示屏变频方法。

[0014]

另一方面,本申请实施例提供了一种终端,所述终端包括ap、显示屏和ddic芯片,

所述ap与所述ddic芯片之间通过移动产业处理器接口(mobile industry processor interface,mipi)相连,所述ddic芯片用于实现如上述方面所述的显示屏变频方法。

[0015]

本申请实施例中,ddic芯片按照第一基础刷新率向ap输出te信号的过程中,若接收到ap下发的降频指令,则仍旧按照第一基础刷新率对应的扫描频率以及补偿频率进行图像扫描和帧补偿,并降低向ap输出te信号的频率(以第二基础刷新率输出te信号),使ap能够根据第二基础刷新率的te信号降低图像绘制频率的同时,通过保持原有扫描频率以及补偿频率能够降低显示屏变频的实现复杂度和成本,并避免变频过程中造成的画面闪烁问题,提高了变频过程中的画面显示质量。

附图说明

[0016]

图1是相关技术中ddic芯片根据变频指令进行变频过程的实施示意图;

[0017]

图2示出了本申请一个示例性实施例示出的显示屏变频方法的流程图;

[0018]

图3是本申请一个示例性实施例示出的显示屏变频过程的实施示意图;

[0019]

图4示出了本申请另一个示例性实施例示出的显示屏变频方法的流程图;

[0020]

图5是本申请一个示例性实施例示出的通过跳过te信号实现显示屏变频过程的实施示意图;

[0021]

图6是本申请另一个示例性实施例示出的通过跳过te信号实现显示屏变频过程的实施示意图;

[0022]

图7是本申请一个示例性实施例示出的通过合并te信号实现显示屏变频过程的实施示意图;

[0023]

图8是本申请另一个示例性实施例示出的通过合并te信号实现显示屏变频过程的实施示意图;

[0024]

图9示出了本申请一个示例性实施例提供的终端的结构方框图。

具体实施方式

[0025]

为使本申请的目的、技术方案和优点更加清楚,下面将结合附图对本申请实施方式作进一步地详细描述。

[0026]

在本文中提及的“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。

[0027]

撕裂效应(tearing effect,te)信号是一种由ddic芯片产生的信号,用于防止图像显示过程中画面刷新时的撕裂问题。当准备好刷新下一帧图像时,ddic芯片即产生te信号,可选的,ap在监听到te信号上升沿,或,检测到te信号处于高电平状态后,向ddic芯片发送下一帧图像数据。

[0028]

相关技术中,由ddic芯片在变频范围内自动实现的显示变频技术被称为自适应动态变频(adaptive dynamic frame rate,adfr)。比如,当显示屏的基础刷新率(base frame rate)为120hz(即最高刷新率),最低刷新率为1hz时,ddic芯片可以在1-120hz变频范围内实现动态变频。

[0029]

在一些实施例中,ddic芯片以帧为单位在实现adfr,ddic芯片产生的te信号与显

示屏的基础刷新率保持一致,相应的,ap根据te信号的频率进行图像绘制,并将绘制完成的图像帧数据传输至ddic芯片,由ddic芯片根据图像帧数据进行图像扫描(或称为图像更新(updating)),并且,ddic芯片在相邻两次图像扫描之间,还会进行帧补偿(compensating)。其中,帧补偿是一种根据伽马(gamma)参数对显示画面进行光学补偿的过程,用于避免非图像扫描期间画面亮度发生突变。

[0030]

示意性的,如图1所示,当ddic芯片按照120hz的频率输出te信号时,ap按照120hz的频率进行图像绘制,并在检测到te信号上升沿时,将绘制完成的图像帧数据传输至ddic芯片(图1中示出了传输b帧和c帧的图像帧数据的过程)。ddic芯片接收到传输的图像帧数据后,即进行图像扫描(图1中示出了b帧和c帧的图像扫描过程),并在相邻两次图像扫描之间进行帧补偿(图1中示出了a帧、b帧和c帧的帧补偿过程)。

[0031]

然而在某些场景下,出于功耗方面的考虑,系统需要降低显示屏的基础刷新率,以便在较低刷新率区间内实现动态变频,从而降低终端功耗,这种场景下,ap即向ddic芯片下发降频指令。ddic芯片接收到降频指令后,必须改变te信号、图像扫描以及帧补偿的频率,相应的,ddic芯片需要使用新的ddic时序和显示屏参数(比如gamma参数)。

[0032]

示意性的,如图1所示,当ap检测到处于视频播放场景时,由于视频帧率通常小于60fps,因此ap通过下发降频指令,指示将基础刷新率由120hz降低至60hz。ddic芯片接收到ap下发的降频指令后,将te信号的输出频率由120hz降低至60hz,并调整图像帧的图像扫描以及帧补偿频率。ap识别出ddic芯片输出te信号的频率下降后,即可按照60hz的频率进行图像绘制。由于图像扫描和帧补偿的频率发生变化,因此ddic芯片无法继续使用120hz对应的ddic时序和gamma参数,而是采用60hz对应的ddic时序和gamma参数。

[0033]

显然,采用上述变频方案,变频过程中ddic芯片需要调整te信号、图像扫描和帧扫描的频率,进而需要对ddic时序和显示屏参数进行调整,一方面增加了变频过程的实现复杂度,另一方面,显示屏参数变化会造成画面闪烁,影响画面显示质量。

[0034]

为了解决上述变频方案存在的问题,本申请实施例中,打破了每帧一个te信号的驱动规则,通过对te信号进行优化,使显示屏能够兼容多种基础刷新率。采用本申请实施例提供的方案,当接收到的ap下发的降频指令时,ddic芯片降低向ap输出te信号的频率,并保持当前图像扫描和帧补偿频率,从而无需调整ddic时序和显示屏参数,一方面简化了变频过程的实现复杂度,另一方面,由于显示屏参数并未发生变化,因此变频过程中不会出现画面闪烁,保证了画面显示质量。下面采用示意性的实施例进行说明。

[0035]

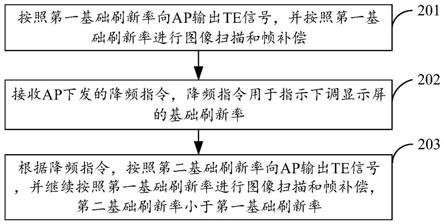

请参考图2,其示出了本申请一个示例性实施例示出的显示屏变频方法的流程图。本实施例以该方法应用于显示屏的ddic芯片来举例说明。该方法包括:

[0036]

步骤201,按照第一基础刷新率向ap输出te信号,并按照第一基础刷新率进行图像扫描和帧补偿。

[0037]

在一种可能的实施方式中,未接收到降频指令时,ddic芯片按照第一基础刷新率向ap输出te信号,ap根据接收到的te信号的频率,按照第一基础刷新率进行图像绘制,并在检测到te信号上升沿时,将绘制得到的图像帧数据发送至ddic芯片。ddic芯片接收到ap发送的图像帧数据后,即根据第一基础刷新率对应的扫描频率以及补偿频率,进行图像扫描以及帧补偿(在两帧图像扫描之间)。此时,ddic芯片采用第一基础刷新率对应的ddic时序和显示屏参数。

[0038]

示意性的,如图3所示,当显示屏的基础刷新率为120hz时,ddic芯片按照120hz的频率输出te信号,ap按照120hz的频率进行图像绘制,并在检测到te信号上升沿时,将绘制完成的图像帧数据传输至ddic芯片。ddic芯片接收到传输的图像帧数据后,即进行图像扫描,并在相邻两次图像扫描之间进行帧补偿。

[0039]

步骤202,接收ap下发的降频指令,降频指令用于指示下调显示屏的基础刷新率。

[0040]

在一些实施例中,当检测到前台应用对基础刷新率的需求低于显示屏当前的基础刷新率时,由于整个系统的刷新率与te信号的频率相关,因此ap需要向ddic芯片发送降频指令,使ddic芯片降低te信号的频率,以此降低ap自身的图像绘制频率,从而降低整个系统的刷新率。

[0041]

在一种可能的实施方式中,ap获取前台应用的应用类型,并根据应用类型确定前台应用的基础刷新率需求。比如,若当前te信号的频率为120hz,当前台应用为视频应用时,由于视频帧率通常小于60帧/秒(一般是24帧/秒或30帧/秒),因此ap向ddic芯片下发降频指令。

[0042]

可选的,该降频指令用于指示下调一级频率等级(预先设置有不同的频率级别),相应的,ddic芯片根据降频指令逐级下调频率。比如,当设置有四级频率等级,由高到低分别为120hz、60hz、40hz和30hz时,若当前基础刷新率为120hz,则在接收到ap下发的降频指令后,确定需要将基础刷新率降低至60hz;若再次接收到ap下发的降频指令,则确定需要将基础刷新率降低至40hz。

[0043]

可选的,该降频指令用于指示下调至指定基础刷新率。比如,该降频指令用于指示将当前基础刷新率由120hz降低至60hz,或者,指示将当前基础刷新率由120hz降低至30hz。

[0044]

步骤203,根据降频指令,按照第二基础刷新率向ap输出te信号,并继续按照第一基础刷新率进行图像扫描和帧补偿,第二基础刷新率小于第一基础刷新率。

[0045]

在一种可能的实施方式中,ddic芯片根据降频指令确定出第二基础刷新率后,按照第二基础刷新率向ap输出te信号,以便ap根据第二基础刷新率的te信号,将图像绘制频率由第一基础刷新率降低至第二基础刷新率。

[0046]

并且,为了降低实现变频过程的复杂度,并避免变频过程中出现画面闪烁的问题,本申请实施例中,ddic芯片仍旧按照第一基础刷新率对应的扫描频率和补偿频率进行图像扫描和帧补偿。由于图像扫描和帧补偿频率并未发生改变,因此,ddic芯片可以沿用原先的ddic时序以及显示屏参数,既简化了变频实现流程,又能够避免因显示屏参数变化造成的画面闪烁问题。

[0047]

示意性的,如图3所示,ddic芯片根据接收到的降频指令,按照60hz的频率输出te信号,ap识别出te信号的频率为60hz后,即按照60hz的频率进行图像绘制,并在检测到te信号上升沿时,将绘制完成的图像帧数据传输至ddic芯片。ddic芯片接收到传输的图像帧数据后,仍旧按照120hz对应的ddic时序进行图像扫描和帧补偿,且由于图像扫描和帧补偿频率并未变化,因此ddic芯片无需调整显示屏参数。

[0048]

综上所述,本申请实施例中,ddic芯片按照第一基础刷新率向ap输出te信号的过程中,若接收到ap下发的降频指令,则仍旧按照第一基础刷新率对应的扫描频率以及补偿频率进行图像扫描和帧补偿,并降低向ap输出te信号的频率(以第二基础刷新率输出te信号),使ap能够根据第二基础刷新率的te信号降低图像绘制频率的同时,通过保持原有扫描

频率以及补偿频率能够降低显示屏变频的实现复杂度和成本,并避免变频过程中造成的画面闪烁问题,提高了变频过程中的画面显示质量。

[0049]

并且,降低显示屏的基础刷新率后,ddic芯片在较低刷新率区间进行动态变频,确保刷新率保持在较低水平,在不影响有画面显示质量的情况下,有助于降低终端的显示功耗。

[0050]

请参考图4,其示出了本申请另一个示例性实施例示出的显示屏变频方法的流程图。本实施例以该方法应用于显示屏的ddic芯片来举例说明。该方法包括:

[0051]

步骤401,按照第一基础刷新率向ap输出te信号,并按照第一基础刷新率进行图像扫描和帧补偿。

[0052]

在一种可能的实施方式中,ddic芯片默认按照显示屏的基础刷新率产生te信号,相应的,ddic芯片按照基础刷新率向ap输出te信号,从而按照基础刷新率对应的ddic时序和显示屏参数进行图像扫描和帧补偿。

[0053]

示意性的,显示屏的基础刷新率为120hz时,ddic芯片则按照120hz的频率向ap输出te信号。

[0054]

步骤402,接收ap下发的降频指令,降频指令用于指示下调显示屏的基础刷新率。

[0055]

在一种可能的实施方式中,ddic芯片下发的降频指令用于指示降频比例。其中,该降频比例可以显式指示,即每条降频指令中包含当前所需降频的比例,或者,该降频比例可以根据降频指令的下发次数确定,即每下发一次降频指令用于指示下调一级基础刷新率。

[0056]

在一些实施例中,该降频指令所指示的降频比例为1/n,用于指示将基础刷新率由原始基础刷新率降低为1/n,n为大于等于2的整数。

[0057]

在一个示意性的例子中,当采用显式方式指示降频比例时,ddic芯片可以直接根据单条降频指令将第一基础刷新率降低至1/2、1/3或1/4;当采用逐级下调时,ddic芯片可以根据接收到的多条降频指令将第一基础刷新率逐级降低至1/2、1/3、1/4。

[0058]

步骤403,根据降频指令所指示的降频比例和第一基础刷新率确定第二基础刷新率,降频比例为1/n,第二基础刷新率为第一基础刷新率的1/n,n为大于等于2的整数。

[0059]

进一步的,ddic芯片根据第一基础刷新率和降频比例,确定第二基础刷新率。

[0060]

示意性的,当降频指令所指示的降频比例为1/2,且第一基础刷新率为120hz时,ddic芯片确定第二基础刷新率为60hz;当降频指令所指示的降频比例为1/4,且第一基础刷新率为120hz时,ddic芯片确定第二基础刷新率为30hz。

[0061]

步骤404,按照第二基础刷新率向ap输出te信号,并继续按照第一基础刷新率对应的ddic时序和显示屏参数进行图像扫描和帧扫描。

[0062]

本申请实施例中,ddic芯片在保持ddic时序的情况下,继续按照第一基础刷新率对应的ddic时序和显示屏参数进行图像扫描和帧扫描,无需准备多套ddic时序和显示屏参数;并且,ddic芯片可以通过跳过或合并te信号的方式,实现向ap输出第二基础刷新率的te信号,下面分别采用示意性的实施例进行说明。

[0063]

在一种可能的实施方式中,ddic芯片可以通过跳过te信号的方式,通过如下步骤向ap输出第二基础刷新率的te信号。

[0064]

一、根据第二基础刷新率确定信号输出间隔。

[0065]

在一种可能的实施方式中,当第二基础刷新率为第一基础刷新率的1/n时,ddic芯

片确定信号输出间隔为n-1帧,即ddic芯片根据第一基础刷新率对应的ddic时序,每隔一帧向ap输出一个te信号。

[0066]

示意性的,当第二基础刷新率为第一基础刷新率的1/2时,ddic芯片根据第一基础刷新率对应的ddic时序,每隔一帧向ap输出一个te信号;当第二基础刷新率为第一基础刷新率的1/3时,ddic芯片根据第一基础刷新率对应的ddic时序,每隔两帧向ap输出一个te信号,以此类推。

[0067]

二、按照信号输出间隔向ap输出te信号,ap接收到te信号的频率为第二基础刷新率。

[0068]

进一步的,ddic芯片根据确定出的信号输出间隔,向ap间隔输出te信号。相应的,ap侧接收到调整输出间隔的te信号后,识别出te信号的频率降低为第二基础刷新率。

[0069]

示意性的,如图5所示,当第一基础刷新率为120hz,第二基础刷新率为60hz,即降频比例为1/2时,ddic芯片输出一个te信号后,跳过下一个te信号,即向ap输出的te信号的间隔由8.3ms提升至16.6ms,相应的,ap识别出te信号的间隔由8.3ms提升至16.6ms后,将图像绘制频率由120hz降至60hz。

[0070]

如图6所示,当第一基础刷新率为120hz,第二基础刷新率为40hz,即降频比例为1/3时,ddic芯片输出一个te信号后,跳过下两个te信号,即向ap输出的te信号的间隔由8.3ms提升至24.9ms,相应的,ap识别出te信号的间隔由8.3ms提升至24.9ms后,将图像绘制频率由120hz降至40hz。

[0071]

在另一种可能的实施方式中,ddic芯片可以通过延长te信号高电平的方式向ap输出第二基础刷新率的te信号。

[0072]

可选的,ddic芯片根据第二基础刷新率向ap输出持续高电平te信号,其中,持续高电平te信号的高电平持续时长为第一基础刷新率下n个连续te信号的时长。比如,当第二基础刷新率为第一基础刷新率为1/2时,持续高电平te信号的高电平持续时长为第一基础刷新率下2个连续te信号的时长;当第二基础刷新率为第一基础刷新率为1/3时,持续高电平te信号的高电平持续时长为第一基础刷新率下3个连续te信号的时长

[0073]

在一些实施例中,ddic芯片可以通过合并te信号的方式产生持续高电平te信号。该过程可以包括如下步骤。

[0074]

一、根据第二基础刷新率确定te信号的信号合并数量。

[0075]

在一种可能的实施方式中,当第二基础刷新率为第一基础刷新率的1/n时,ddic芯片确定信号合并数量为n,即ddic芯片根据第一基础刷新率对应的ddic时序,将连续n个te信号进行信号合并。

[0076]

示意性的,当第二基础刷新率为第一基础刷新率的1/2时,ddic芯片根据第一基础刷新率对应的ddic时序,对连续的2个te信号进行合并;当第二基础刷新率为第一基础刷新率的1/3时,ddic芯片根据第一基础刷新率对应的ddic时序,对连续的3个te信号进行合并,以此类推。

[0077]

二、按照信号合并数量对te信号进行高电平合并,并向ap输出高电平合并后的te信号,ap接收到te信号的频率为第二基础刷新率。

[0078]

在一种可能的实施方式中,在进行te信号合并时,ddic芯片对te信号进行高电平合并,从而延长向ap输出的te信号的高电平持续时长,相应的,ap侧通过识别te信号的上升

沿,确定te信号的频率降低为第二基础刷新率。

[0079]

可选的,当降频比例为1/n时,ddic芯片对第kn+1至第kn+n个te信号进行高电平合并,k为自然数。比如,当降频比例为1/2时,ddic芯片对第1和第2个te信号进行高电平合并,对第3和第4个te信号进行高电平合并,以此类推;当降频比例为1/3时,ddic芯片对第1、第2和第3个te信号进行高电平合并,对第4、第5和第6个te信号进行高电平合并,以此类推。

[0080]

示意性的,如图7所示,当第一基础刷新率为120hz,第二基础刷新率为60hz,即降频比例为1/2时,ddic芯片对第1和第2个te信号进行高电平合并后输出,对第3和第4个te信号进行高电平合并后输出,对第5和第6个te信号进行高电平合并后输出,即向ap输出的te信号的上升沿间隔由8.3ms提升至16.6ms,相应的,ap通过识别te信号上升沿,将图像绘制频率由120hz降至60hz。

[0081]

如图8所示,当第一基础刷新率为120hz,第二基础刷新率为40hz,即降频比例为1/3时,ddic芯片对第1、第2和第3个te信号进行高电平合并后输出,对第4、第5和第6个te信号进行高电平合并后输出,对第7、第8和第9个te信号进行高电平合并后输出,即向ap输出的te信号的上升沿间隔由8.3ms提升至24.9ms,相应的,ap通过识别te信号上升沿,将图像绘制频率由120hz降至40hz。

[0082]

当然,除了通过上述合并te信号的方式产生持续高电平te信号外,ddic芯片还可以采用其他方式产生持续高电平te信号,本申请实施例对此并不构成限定。

[0083]

需要说明的是,相较于跳过te信号这种方式,采用输出持续高电平te信号这种方式时,由于te信号的高电平持续时长更长,因此ap通过检测te信号高电平能够尽快将绘制完成图像帧数据发送至ddic芯片,以便ddic芯片尽快进行图像更新,有助于降低了图像帧的显示延迟。

[0084]

在一种可能的实施方式中,不论采用跳过te信号还是输出持续高电平te信号的方式,ddic芯片均以图像扫描时刻为起点,按照第二基础刷新率向ap输出te信号,避免从帧补偿时刻开始执行造成的图像显示异常。

[0085]

步骤405,接收ap下发的升频指令,升频指令用于指示上调显示屏的基础刷新率。

[0086]

当应用场景发生变化时,显示屏当前的基础刷新率可能无法满足前台应用对基础刷新率的需求,此时,ap向ddic芯片下发升频指令,以便提高显示屏的基础刷新率。

[0087]

其中,升频指令指示升频比例的方式与降频指令指示降频比例的方式类似,本实施例在此不再赘述。

[0088]

步骤406,根据升频指令,按照第三基础刷新率向ap输出te信号,并继续按照第一基础刷新率进行图像扫描和帧补偿,第三基础刷新率大于第二基础刷新率,且第三基础刷新率小于等于第一基础刷新率。

[0089]

在一些可能的实施方式中,该升频指令指示将当前基础刷新率恢复为原始基础刷新率,或者,该升频指令指示将当前基础刷新率提升至与原始基础刷新率之间的其他基础刷新率。比如,若原始基础刷新率为120hz,当前基础刷新率为40hz时,ap可以通过下发升频指令,指示将基础刷新率上调为120hz,相应的,ddic芯片将te信号的频率恢复至120hz;也可以指示将基础刷新率上调为60hz,相应的,ddic芯片将te信号的频率提升至60hz。

[0090]

可选的,ddic信号可以通过跳过te信号或者输出持续高电平te信号的方式(当第一基础刷新率与第三基础刷新率不同时),向ap输出第三基础刷新率的te信号,其过程可以

参考上述降频过程,本实施例在此不再赘述。

[0091]

本实施例中,ddic芯片通过输出持续高电平te信号或跳过te信号的方式,在保持当前ddic时序和显示屏参数的前提下,降低向ap输出的te信号的频率,在降低变频流程的实现复杂度的同时,避免变频过程中因显示屏参数变化导致的画面闪烁问题。

[0092]

此外,本实施例中,通过输出持续高电平te信号的方式降低te信号的频率,能够提高ap检测到te信号高电平的概率,使ap能够及时将绘制完成的图像帧数据发送至ddic芯片,从而降低图像绘制到上屏显示之间的延迟。

[0093]

在完成基础刷新率调整前后,ddic芯片可以通过adfr方案实现自动变频。在一种可能的实施方式中,ddic芯片根据第一刷新频率(可以为当前的基础刷新率)初始化显示屏参数,当接收到ap发送的第一图像数据时,根据第一刷新频率进行图像扫描;若在第一刷新频率对应的列向前延间隔(vertical front porch,vfp)的预设延迟时长内未接收到ap发送的第二图像数据,则将第一刷新频率调整为第二刷新频率,第二刷新频率小于第一刷新频率,从而根据第二刷新频率调整显示屏参数。

[0094]

总的来说,如表一所示,本申请实施例相较于相关技术提供的显示屏变频方案存在如下区别点和优点。

[0095]

表一

[0096][0097]

在一些实施例中,本申请实施例提供的方法应用于移动终端,即由移动终端中显示屏的ddic芯片执行上述显示屏变频方法,且该显示屏可以为有机发光二极体(organiclight-emitting diode,oled)显示屏。由于移动终端通常由电池进行供电,且电池的电量有限(对功耗较为敏感),因此将本申请实施例提供的方法用于移动终端后,能够避免在低刷新率场景下仍旧采用高刷新率造成的功耗浪费。其中,该移动终端可以包括智能手机、平板电脑、可穿戴式设备(比如智能手表)、便携式个人计算机等等,本申请实施例并不对移动终端的具体类型进行限定。

[0098]

当然,本申请实施例提供的方法还可以用于其他非电池供电的终端,比如电视、显示器或个人计算机等等,本申请实施例对此不作限定。

[0099]

本申请实施例还提供了一种ddic芯片,所述ddic芯片应用于显示屏,所述ddic芯片用于:

[0100]

按照第一基础刷新率向应用处理器ap输出撕裂效应te信号,并按照所述第一基础刷新率进行图像扫描和帧补偿;

[0101]

接收所述ap下发的降频指令,所述降频指令用于指示下调所述显示屏的基础刷新率;

array,pla)中的至少一种硬件形式来实现。处理器910可集成中央处理器(central processing unit,cpu)、图像处理器(graphics processing unit,gpu)、神经网络处理器(neural-network processing unit,npu)和调制解调器等中的一种或几种的组合。其中,cpu主要处理操作系统、用户界面和应用程序等;gpu用于负责触摸显示屏模组930所需要显示的内容的渲染和绘制;npu用于实现人工智能(artificial intelligence,ai)功能;调制解调器用于处理无线通信。可以理解的是,上述调制解调器也可以不集成到处理器910中,单独通过一块芯片进行实现。

[0124]

存储器920可以包括随机存储器(random access memory,ram),也可以包括只读存储器(read-only memory,rom)。可选地,该存储器920包括非瞬时性计算机可读介质(non-transitory computer-readable storage medium)。存储器920可用于存储指令、程序、代码、代码集或指令集。存储器920可包括存储程序区和存储数据区,其中,存储程序区可存储用于实现操作系统的指令、用于至少一个功能的指令(比如触控功能、声音播放功能、图像播放功能等)、用于实现本申请各个方法实施例的指令等;存储数据区可存储根据终端900的使用所创建的数据(比如音频数据、电话本)等。

[0125]

显示屏模组930是用于进行图像显示的显示组件,通常设置在终端900的前面板。显示屏模组930可被设计成为全面屏、曲面屏、异型屏、双面屏或折叠屏。显示屏模组930还可被设计成为全面屏与曲面屏的结合,异型屏与曲面屏的结合,本实施例对此不加以限定。

[0126]

本申请实施例中,显示屏模组930包括ddic芯片931和显示屏932(面板)。其中,显示屏932为oled显示屏,其可以是低温多晶硅(low temperature poly-silicon,ltps)amoled显示屏或低温多晶氧化物(low temperature polycrystalline oxide,ltpo)amoled显示屏。

[0127]

ddic芯片931用于驱动显示屏932进行图像显示,且ddic芯片931用于实现上述各个实施例提供的显示屏变频方法。此外,ddic芯片931与处理器910之间通过mipi接口相连,用于接收处理器910下发的图像数据以及指令。

[0128]

在一种可能的实现方式中,该显示屏模组930还具有触控功能,通过触控功能,用户可以使用手指、触摸笔等任何适合的物体在显示屏模组930上进行触控操作。

[0129]

除此之外,本领域技术人员可以理解,上述附图所示出的终端900的结构并不构成对终端900的限定,终端可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。比如,终端900中还包括麦克风、扬声器、射频电路、输入单元、传感器、音频电路、无线保真(wireless fidelity,wifi)模块、电源、蓝牙模块等部件,在此不再赘述。

[0130]

本领域技术人员应该可以意识到,在上述一个或多个示例中,本申请实施例所描述的功能可以用硬件、软件、固件或它们的任意组合来实现。当使用软件实现时,可以将这些功能存储在计算机可读介质中或者作为计算机可读介质上的一个或多个指令或代码进行传输。计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。

[0131]

以上所述仅为本申请的可选实施例,并不用以限制本申请,凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1