点矩阵型显示装置以及计时装置的制作方法

1.本公开涉及点矩阵型显示装置以及使用了该点矩阵型显示装置的计时装置。

背景技术:

2.以往,例如已知有专利文献1所记载的点矩阵型显示装置。

3.在先技术文献

4.专利文献

5.专利文献1:日本特开2015-87437号公报

技术实现要素:

6.本公开的点矩阵型显示装置,具备:

7.显示部,具有:多条栅极信号线,在第一方向上延伸;多条源极信号线,在与所述第一方向交叉的第二方向上延伸;以及多个像素电路,与所述多条栅极信号线和所述多条源极信号线的交叉部对应地配置;

8.变换电路,将经由串行接口从外部输入的串行信号与从外部输入的第一时钟信号同步地获取,并将获取到的所述串行信号变换为并行信号,该串行信号包括用于确定进行图像数据的改写的像素电路的地址数据和向所述像素电路供给的所述图像数据;以及

9.控制电路,基于频率比所述第一时钟信号的频率低的第二时钟信号,生成对所述变换电路的串行并行变换的定时进行控制的控制信号。

10.本公开的计时装置是具备本公开的点矩阵型显示装置的计时装置,是具备控制经过时间的最小单位的经时控制部的结构。

附图说明

11.根据下述的详细的说明和附图,本发明的目的、特色以及优点将变得更加明确。

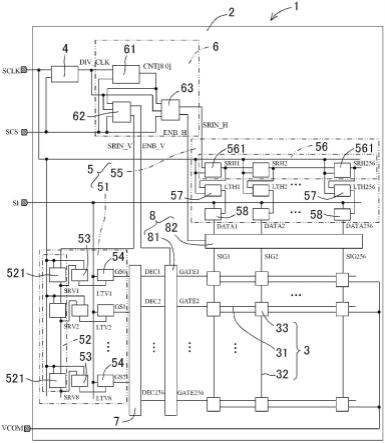

12.图1是表示本公开所涉及的点矩阵型显示装置的结构的一例的电路框图。

13.图2是用于说明图1的点矩阵型显示装置的整体动作的时序图的一部分。

14.图3是表示图1的点矩阵型显示装置中的像素电路的结构的一例的电路图。

15.图4是表示图1的点矩阵型显示装置中的分频电路的结构的一例的电路图。

16.图5a是表示图1的点矩阵型显示装置中的控制电路的结构的一例的电路图。

17.图5b是表示图1的点矩阵型显示装置中的控制电路的结构的一例的电路图。

18.图5c是表示图1的点矩阵型显示装置中的控制电路的结构的一例的电路图。

19.图6a是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

20.图6b是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

21.图6c是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

22.图7a是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

23.图7b是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

24.图7c是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图。

25.图8是表示图1的点矩阵型显示装置中的解码器电路的结构的一例的电路图。

26.图9a是表示图1的点矩阵型显示装置中的驱动器电路的结构的一例的电路图。

27.图9b是表示图1的点矩阵型显示装置中的驱动器电路的结构的一例的电路图。

28.图10是用于说明图1的点矩阵型显示装置中的计数器电路的动作的时序图的一部分。

29.图11是具备图1的点矩阵型显示装置的计时装置的示意性的主视图。

具体实施方式

30.对本公开的实施方式所涉及的点矩阵型显示装置为基础的结构进行说明。专利文献1所记载的点矩阵型显示装置具备多个像素部,该多个像素部与多条栅极信号线、多条源极信号线、以及多条栅极信号线和多条源极信号线的交叉部对应地配置,且各自具有存储电路。这样的点矩阵型显示装置针对基于栅极信号线和源极信号线而选择的像素部,执行改写图像数据的改写驱动,针对非选择的像素部,执行使用保持于存储电路的图像数据的静止图像驱动。

31.在以往的点矩阵型显示装置中,用于选择执行改写驱动的像素部的地址数据以及供给到所选择的像素部的图像数据被串联(串行)地输入。因此,地址数据以及图像数据的传输时间变长,有时动作变慢。此外,在以往的点矩阵型显示装置中,在为了缩短传输时间而提高了时钟频率的情况下,控制改写驱动的控制电路难以追随高速化后的时钟频率,因此有时无法正常地动作。

32.以下,参照附图,本公开的点矩阵型显示装置的实施方式进行说明。以下参照的各图表示本公开的实施方式所涉及的点矩阵型显示装置的主要的构成构件等。因此,本公开的实施方式所涉及的点矩阵型显示装置也可以具备未图示的电路基板、布线导体、控制ic、lsi等公知的结构。

33.图1是表示本公开所涉及的点矩阵型显示装置的结构的一例的电路框图,图2是用于说明图1的点矩阵型显示装置的整体动作的时序图的一部分。图3是表示图1的点矩阵型显示装置中的像素电路的结构的一例的电路图,图4是表示图1的点矩阵型显示装置中的分频电路的结构的一例的电路图。图5a~5c是表示图1的点矩阵型显示装置中的控制电路的结构的一例的电路图,图6a~6c、7a~7c是表示图1的点矩阵型显示装置中的变换电路的结构的一例的电路图,图8是表示图1的点矩阵型显示装置中的解码器电路的结构的一例的电路图,图9a、9b是表示图1的点矩阵型显示装置中的驱动器电路的结构的一例的电路图。图10是用于说明图1的点矩阵型显示装置中的计数器电路的动作的时序图的一部分。以下,对点矩阵型显示装置具有65536点(256

×

256点)的像素数的情况进行说明,但点矩阵型显示装置的像素数是任意的。此外,以下,对构成为进行白黑显示的像素电路进行说明,但像素电路能够构成为进行灰度显示或者全彩显示。

34.本实施方式的点矩阵型显示装置1也可以具备显示部3、分频电路4、变换电路5以及控制电路6。

35.显示部3配置在基板2的一个主面上。基板2例如是透明或者不透明的玻璃基板、塑料基板、陶瓷基板等。基板2例如可以具有矩形板状等多边形板状、圆形板状、椭圆形板状等

形状,也可以具有其他形状。

36.显示部3具有多条栅极信号线31、多条源极信号线32以及多个像素电路33。多条栅极信号线31配置于第一方向(例如,行方向),多条源极信号线32配置于与第一方向交叉的第二方向(例如,列方向)。多个像素电路33与多条栅极信号线31和多条源极信号线32的交叉部对应地配置成矩阵状。

37.进行多个像素电路33中的图像数据的改写、即被改写驱动的一个以上的像素电路33基于从外部的信号供给装置(未图示)输入的地址数据而被选择。对所选择的一个以上的像素电路33进行图像数据的改写。改写所使用的新的图像数据从信号供给装置输入。对于未被选择的像素电路33,执行使用保持在该像素电路33中的图像数据的静止图像驱动。

38.各像素电路33例如如图3所示,具有写入开关电路331、锁存电路332、像素电位生成电路333以及液晶元件334。液晶元件334具有像素电极334a、液晶334b以及对置电极334c。

39.写入开关电路331具有薄膜晶体管(thin film transistor:tft)元件。tft元件例如具有由非晶硅(a-si)、低温多晶硅(low-temperature poly silicon:ltps)等构成的半导体膜、栅电极、源电极以及漏电极。栅电极与多条栅极信号线31中的1条连接,源电极与多条源极信号线32中的1条连接。漏电极与锁存电路332的输入端子连接。

40.锁存电路332例如如图3所示,由将第一cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)反相器332a以及第二cmos反相器332b连接成环状而成的静态随机存取存储器(static random access memory:sram)等构成。锁存电路332将第一cmos反相器332a和第二cmos反相器332b串联连接,使来自第二cmos反相器332b的漏极公共连接点的输出反馈输入到第一cmos反相器332a的栅极公共连接点。由此,当向第一cmos反相器332a的栅极公共连接点输入高电平的信号(以下,也简称为h信号)时,从第一cmos反相器332a的漏极公共连接点输出低电平的信号(以下,也简称为l信号)。当来自第一cmos反相器332a的l信号被输入到第二cmos反相器332b的栅极公共连接点时,从第二cmos反相器332b的漏极公共连接点输出h信号,该h信号被反馈输入到第一cmos反相器332a的栅极公共连接点。其结果,“h、l、h”的信号始终在环状的传输线上被保持。

41.例如,如图3所示,像素电位生成电路333由异或(exor)的逻辑门电路构成。像素电位生成电路333具有两个输入端子,在一个输入端子中输入保持在锁存电路332中的写入数据信号sig,在另一个输入端子中输入从外部装置供给的公共电压vcom。公共电压vcom也可以使h(高)电平的电压(例如,3v)和l(低)电平的电压(例如,0v)周期性地反相。例如,在保持在锁存电路332中的写入数据信号sig是l信号的情况下,在对置电极334c的电压与像素电极334a之间产生电位差,如果是常白模式则成为黑显示,如果是常黑模式,则成为白显示。此外,在保持在锁存电路332中的写入数据信号sig是h信号的情况下,在对置电极334c的电压与像素电极334a之间不产生电位差,如果是常白模式则成为白显示,如果是常黑模式,则成为黑显示。在像素电路33的这样的驱动中,即使在使公共电压vcom反相驱动的情况下,也能够保持对置电极334c的电压与像素电极334a之间的电位差,因此能够在保持像素电路33中的图像显示的状态下,对像素电路33进行交流驱动。由此,恩能够抑制像素电路33的液晶334b的劣化。

42.在改写像素电路33中的图像显示的情况下,使写入开关电路331接通。即,向栅极

信号线31供给h信号,向源极信号线32供给图像数据信号。将供给至源极信号线32的图像数据信号向锁存电路332传输,并保持于锁存电路332。由此,对置电极334c的电压与像素电极334a之间的电位差根据图像数据信号而变化,例如在图像数据信号为l信号的情况下,如果是常白模式,则成为黑显示,如果是常黑模式,则成为白显示,在图像数据信号为h信号的情况下,如果是常白模式,则成为白显示,如果是常黑模式,则成为黑显示。

43.像素电路33也可以构成为锁存电路332保持多个比特,在这种情况下,像素电路33能够进行灰度显示。此外,像素电路33也可以构成为包含进行红色的灰度显示的副像素电路、进行绿色的灰度显示的副像素电路、进行蓝色的灰度显示的副像素电路。在这种情况下,像素电路33能够进行全彩显示。

44.在点矩阵型显示装置1中,能够按与一个栅极信号线31连接的每个像素电路33进行显示部3中的改写驱动,能够对除此以外的像素电路33进行静止图像驱动。因此,点矩阵型显示装置1的功耗低。

45.例如,如图4所示,分频电路4对从信号供给装置输入的移位时钟信号sclk(以下,也称为第一时钟信号)进行分频,生成频率比第一时钟信号sclk低的时钟信号(以下,也称为第二时钟信号)div_clk。信号供给装置基于从tv接收机、个人计算机等外部装置输入的影像信号、同步信号、时钟信号等,生成第一时钟信号sclk,并输出到点矩阵型显示装置1。此外,信号供给装置生成后述的串行信号si以及芯片选择信号scs,并将这些信号输出到点矩阵型显示装置1。

46.本实施方式的点矩阵型显示装置1也可以具备控制第一时钟信号sclk的频率的时钟频率控制部。在这种情况下,容易使第一时钟信号sclk的频率高速化。时钟频率控制部也可以包含在上述的信号供给装置中,也可以与信号供给装置分开设置。此外,时钟频率控制部也可以是保存在ic(integrated circuit)、lsi(large scale integrated circuit)等驱动元件的ram(random access memory)、rom(read only memory)中的程序软件,还可以是形成在电路基板上的频率控制电路等。

47.此外,本实施方式的点矩阵型显示装置1通过分频电路4对第一时钟信号sclk进行分频,生成频率比第一时钟信号sclk低的第二时钟信号div_clk,但不限于该结构。例如,也可以具备:第一时钟信号产生部,生成第一时钟信号sclk;第二时钟信号产生部,其与该第一时钟信号产生部分开设置,生成第二时钟信号div_clk。在这种情况下,能够更精确地控制第一时钟信号sclk的频率和第二时钟信号div_clk的频率。

48.例如,如图4所示,分频电路4包括触发器电路41和反相器电路42。触发器电路41具有d端子、ck端子、q端子以及xrst端子。向ck端子供给第一时钟信号sclk。反相器电路42的输入端子与q端子连接,反相器电路42的输出端子与d端子连接。此外,向xrst端子供给芯片选择信号scs。芯片选择信号scs是在对显示部3进行改写驱动时成为h(高)电平的信号。根据分频电路4,从q端子输出的第二时钟信号divclk的频率成为第一时钟信号sclk的频率的二分之一。另外,分频电路4的分频数是任意的,分频电路例如可以对第一时钟信号sclk进行3分频、4分频,也可以进行n分频(n为2以上的整数)。也可以使第一时钟信号sclk的频率越高,则越增大n的值。

49.变换电路5将从信号供给装置输入的串行信号si与第一时钟信号sclk同步地获取。串行信号si经由串行接口从信号供给装置输入至变换电路5。变换电路5将获取的串行

信号si变换为并行信号。

50.在本实施方式中,例如如图2所示,串行信号si包括地址数据a0~a7(在统称的情况下,仅记载为“a”)以及图像数据do~d255(在统称的情况下,仅记载为“d”)。地址数据a0~a7是用于确定(即,选择)多个像素电路33中的、进行图像数据的改写的一个以上的像素电路33的数据。图像数据d0~d255是表示向所选择的一个以上的像素电路33供给的、应该显示该一个以上的像素电路33的图像的数据。

51.串行信号si也可以包括不用于改写驱动的虚拟数据dm。在本实施方式中,例如如图2所示,串行信号si包括虚拟数据dm0~dm31(在统称的情况下,仅记载为“dm”)。

52.串行信号si与第一时钟信号sclk同步地被传输到变换电路5。串行信号si例如如图2所示,也可以以前端的8个时钟传输地址数据a0~a7,以接下来的256个时钟传输图像数据d0~d255,接下来以32个时钟传输虚拟数据dm0~dm31。

53.在这种情况下,能够将虚拟数据dm的传输期间利用于执行改写驱动的改写执行期间等,从而有利于高速化。即,虚拟数据dm的传输期间也可以是基于地址数据a的栅极信号gate被供给到栅极信号线31的栅极信号gate的激活期间,并且是基于图像数据d的源极信号被供给到源极信号线32的源极信号的激活期间。

54.虚拟数据dm的传输期间也可以为地址数据a的传输期间以及图像数据d的传输期间的合计的同等以下。在这种情况下,有利于高速化。虚拟数据dm的传输期间可以为地址数据a的传输期间以及图像数据d的传输期间的合计的0.5倍以上且1倍以下,但不限于该范围。

55.此外,虚拟数据dm的传输期间也可以为与地址数据a的传输期间以及图像数据d的传输期间的至少一方同等以下。在这种情况下,有利于高速化。虚拟数据dm的传输期间可以为地址数据a的传输期间以及图像数据d的传输期间中的至少一方的0.7倍以上且1倍以下,但不限于该范围。

56.此外,虚拟数据dm的传输期间也可以为与地址数据a的传输期间以及图像数据d的传输期间的任一短的一方同等以下。在这种情况下,有利于高速化。虚拟数据dm的传输期间可以是地址数据a的传输期间以及图像数据d的传输期间中的任一短的一方的0.7倍以上且1倍以下,但不限于该范围。

57.控制电路6控制对显示部3的改写驱动。控制电路6与第二时钟信号div_clk同步地进行动作。控制电路6生成用于对变换电路5中的串行_并行(串行到并行)变换进行控制的控制信号、特别是用于对变换电路5中的串行_并行变换的定时进行控制的控制信号。

58.控制电路6包括计数器电路(计数电路)61、垂直控制电路62以及水平控制电路63。

59.计数器电路61与第二时钟信号div_clk同步地进行动作,生成计数器信号(计数信号)cnt[8:0]。计数器信号cnt[8:0]是对作为脉冲信号的第二时钟信号div_clk的上升沿的数量进行计数而得到的信号。计数器信号cnt[8:0]用于生成控制由变换电路5进行的串行-并行变换的控制信号。

[0060]

计数器电路61例如在图5a所示的同步式计数器电路的情况下,包括多个组合逻辑电路611和多个触发器电路612。

[0061]

组合逻辑电路611包括多个逻辑门电路而构成。此外,各触发器电路612具有d端子、q端子、ck端子以及xrst端子。各触发器电路612从q端子输出计数器信号cnt[8:0]的各

比特(图5a所示的cnt0~cnt8)。向d端子输入组合逻辑电路611基于计数器信号cnt[8:0]生成的下一个计数器信号next_cnt[8:0]的各比特(图5a所示的next_cnt0~next_cnt8)。向ck端子输入第二时钟信号div_clk,向xrst端子输入芯片选择信号scs。

[0062]

通常,组合逻辑电路是不具有由计算not、and、or等基本的逻辑函数的逻辑门和连接它们的布线构成的反馈环的电路。组合逻辑电路具有几个输入和输出(通常为一个),各输入值以及输出值取0或者1的值。各输出值仅通过输入值的组合而唯一地决定。即,组合逻辑电路计算逻辑函数。任意的逻辑函数能够用乘积和公式表示。因此,能够使用not、and、or的各逻辑门并通过not-and-or的组合电路来实现任意的逻辑函数。将这样的电路通常称为and-or二级组合逻辑电路,但逻辑电路的级数一多,动作速度就会变慢,因此组合逻辑电路611容易成为第一时钟信号sclk的上限频率(以往,1.5mhz左右)的限速部。

[0063]

垂直控制电路62基于从计数器电路61输出的计数器信号cnt[8:0]来生成垂直开始脉冲信号srin_v以及栅极激活信号enb_v。垂直开始脉冲信号srin_v是生成地址数据a0~a7的获取定时信号的移位寄存器的开始信号。垂直开始脉冲信号srin_v与地址数据a的前端相对应地进行激活。另外,在本说明书中,“信号激活”时意味着信号成为接通状态(即,h(高)的状态),“信号非激活”时意味着信号成为截止状态(即,l(低)的状态)。栅极激活信号enb_v是决定向栅极信号线31供给的栅极信号gate的激活期间的信号。栅极激活信号enb_v在传输地址数据a以及图像数据d之后,在传输虚拟数据dm时激活。

[0064]

例如,如图5b所示,垂直控制电路62包括组合逻辑电路621、触发器电路622、第一单发脉冲电路623、第二单发脉冲电路624、第三单发脉冲电路625、或(or)的逻辑门电路(以下,也称为or电路)626以及rs锁存电路627。

[0065]

组合逻辑电路621构成为包括多个逻辑门电路。组合逻辑电路621基于由计数器电路61生成的计数器信号cnt[8:0]生成第一控制信号cs1并将其输出到触发器电路622。

[0066]

触发器电路622具有d端子、q端子、ck端子以及xrst端子。向d端子输入由组合逻辑电路621生成的第一控制信号cs1。向ck端子输入第二时钟信号div_clk。向xrst端子输入芯片选择信号scs。q端子与第一单发脉冲电路623连接。触发器电路622将第一控制信号cs1保持在第二时钟信号div_clk的上升沿,将第一控制信号cs1输出到第一单发脉冲电路623。

[0067]

第一单发脉冲电路623包括延迟电路及与(and)的逻辑门电路。第一单发脉冲电路623与从触发器电路622输出的第一控制信号cs1的上升相应地生成第一触发信号ts1,并输出到or电路626。

[0068]

第二单发脉冲电路624包括延迟电路及与(and)的逻辑门电路。第二单发脉冲电路624与芯片选择信号scs的上升相应地生成第二触发信号ts2,并输出到or电路626。

[0069]

第三单发脉冲电路625包括延迟电路及或非(nor)的逻辑门电路。第三单发脉冲电路625与第二时钟信号div_clk的下降相应地生成第三触发信号ts3,并输出至rs锁存电路627。

[0070]

or电路626对从第一单发脉冲电路623输出的第一触发信号ts1以及从第二单发脉冲电路624输出的第二触发信号ts2的或进行运算,并输出至rs锁存电路627。

[0071]

rs锁存电路627具有s端子、r端子以及q端子。从or电路626输出的第一触发信号ts1以及第二触发信号ts2的或被输入至s端子。从第三单发脉冲电路625输出的第三触发信号ts3被输入至r端子。rs锁存电路627从q端子输出垂直开始脉冲信号srin_v。rs锁存电路

627的动作是公知。例如,rs锁存电路627在向s端子输入l信号、向r端子输入h信号的情况下,只要从q端子输出作为垂直开始脉冲信号srin_v的l信号,并且向s端子或者r端子输入的信号不产生迁移,或者s端子或者r端子均为l信号输入,就维持其输出状态。此外,rs锁存电路向s端子输入h信号、向r端子输入l信号的情况下,只要从q端子输出作为垂直开始脉冲信号srin_v的h信号,并且输入至s端子或者r端子的信号不会产生迁移,或者s端子或者r端子均为l信号输入,就维持其输出状态。

[0072]

例如,如图5b所示,垂直控制电路62包括组合逻辑电路628和触发器电路629。

[0073]

组合逻辑电路628包括多个逻辑门电路而构成。组合逻辑电路628基于由计数器电路61生成的计数器信号cnt[8:0]生成第二控制信号cs2,并将其输出至触发器电路629。

[0074]

触发器电路629具有d端子、q端子、ck端子以及xrst端子。向d端子输入由组合逻辑电路628生成的第二控制信号cs2。向ck端子输入第二时钟信号div_clk。向xrst端子输入芯片选择信号scs。触发器电路629从q端子输出栅极激活信号enb_v。触发器电路629将第二控制信号cs2保持在第二时钟信号div_clk的上升沿,并且输出作为栅极激活信号enb_v的第二控制信号cs2。

[0075]

例如,如图5c所示,水平控制电路63包括组合逻辑电路631、触发器电路632、第四单发脉冲电路633、第五单发脉冲电路634以及rs锁存电路635。

[0076]

组合逻辑电路631包括多个逻辑门电路而构成。组合逻辑电路631基于由计数器电路61生成的计数器信号cnt[8:0]生成第三控制信号cs3,并将其输出至触发器电路632。

[0077]

触发器电路632具有d端子、q端子、ck端子以及xrst端子。向d端子输入由组合逻辑电路631生成的第三控制信号cs3。向ck端子输入第二时钟信号div_clk。向xrst端子输入芯片选择信号scs。q端子与第四单发脉冲电路633连接。触发器电路632将第三控制信号cs3保持在第二时钟信号div_clk的上升沿,将第三控制信号cs3输入至第四单发脉冲电路633。

[0078]

第四单发脉冲电路633包括延迟电路及与(and)的逻辑门电路。第四单发脉冲电路633与从触发器电路632输出的第三控制信号cs3的上升相应地生成第四触发信号ts4,并输出至rs锁存电路635。

[0079]

第五单发脉冲电路634包括延迟电路及或非(nor)的逻辑门电路。第五单发脉冲电路634与芯片选择信号scs的下降相应地生成第五触发信号ts5,并输出至rs锁存电路635。

[0080]

rs锁存电路635具有s端子、r端子以及q端子。从第四单发脉冲电路633输出的第四触发信号ts4被输入至s端子。从第五单发脉冲电路634输出的第五触发信号ts5被输入至r端子。rs锁存电路635从q端子输出水平开始脉冲信号srin_h。rs锁存电路635的动作是公知的。例如,rs锁存电路635在向s端子输入l信号,向r端子输入了h信号的情况下,只要从q端子输出作为水平开始脉冲信号srin_h的l信号,并且向s端子或者r端子输入的信号不产生迁移,或者s端子或者r端子均为l信号输入,就维持其输出状态。此外,rs锁存电路在向s端子输入了h信号、向r端子输入了l信号的情况下,只要从q端子输出作为水平开始脉冲信号srin_h的h信号,并且输入至s端子或者r端子的信号不产生迁移,或者s端子或者r端子均为l信号输入,就维持其输出状态。

[0081]

例如,如图5c所示,水平控制电路63包括组合逻辑电路636和触发器电路637。

[0082]

组合逻辑电路636包括多个逻辑门电路而构成。组合逻辑电路636基于由计数器电路61生成的计数器信号cnt[8:0]生成第四控制信号cs4,并输出至触发器电路637。

[0083]

触发器电路637具有d端子、q端子、ck端子以及xrst端子。向d端子输入由组合逻辑电路636生成的第四控制信号cs4。向ck端子输入第二时钟信号div_clk。向xrst端子输入芯片选择信号scs。触发器电路637从q端子输出数据激活信号enb_h。触发器电路637将第四控制信号cs4保持在第二时钟信号div_clk的上升沿,输出作为数据激活信号enb_h的第四控制信号cs4。

[0084]

接下来,本实施方式的点矩阵型显示装置1中的变换电路5的电路结构的一例进行说明。变换电路5包括垂直变换电路51和水平变换电路55。

[0085]

垂直变换电路51基于从垂直控制电路62输出的垂直开始脉冲信号srin_v,对串行信号si中包括的地址数据a0~a7进行并行变换。例如,如图1所示,垂直变换电路51包括移位寄存器电路52、多个锁存激活信号电路53以及多个锁存电路54。

[0086]

移位寄存器电路52与第一时钟信号sclk同步地进行动作。从垂直控制电路62输出的垂直开始脉冲信号srin_v被输入至移位寄存器电路52。

[0087]

例如,如图6a所示,移位寄存器电路52包括串联连接的多级的触发器电路521。多级触发器电路521分别具有d端子、ck端子以及q端子。向ck端子输入第一时钟信号sclk。从垂直控制电路62输出的垂直开始脉冲信号srin_v被输入至第一级的触发器电路521的d端子。多级触发器电路521分别输出垂直移位信号srv1~srvn(在统称的情况下,仅记载为“srv”)。在此,n是根据栅极信号线31的条数决定的正整数,在本实施方式中,n=8。前级的触发器电路521的q端子与第二级以后的触发器电路521的d端子连接。多级触发器电路521的q端子分别与多个锁存激活信号电路53连接。

[0088]

例如,如图1所示,多级触发器电路521与多个锁存激活信号电路53分别连接,多个锁存激活信号电路53分别与多个锁存电路54连接。

[0089]

例如,如图6b所示,多个锁存激活信号电路53分别包括反相器电路531及与非(nand)的逻辑门电路(以下,也称为nand电路)532。nand电路532具有两个输入端子,从触发器电路521输出的垂直移位信号srv被输入至一方的输入端子,由反相器电路531反相的第一时钟信号sclk被输入至另一方的输入端子。多个锁存激活信号电路53分别向多个锁存电路54输出垂直锁存激活信号ltv1~ltvn(在统称的情况下,仅记载为“ltv”)。

[0090]

多个锁存电路54分别具有d端子、ck端子以及q端子,向ck端子输入从与该锁存电路54连接的锁存激活信号电路53输出的垂直锁存激活信号ltv。此外,从信号供给装置供给的串行信号si被输入至d端子。多个锁存电路54在锁存激活信号ltv为h信号的期间,分别获取串行信号si中包括的地址数据a0~a7,保持锁存激活信号ltv为l信号的期间。例如,如图2所示,多个锁存电路54分别从q端子输出作为地址信号gs0~gs7的地址数据a0~a7。另外,在图2中,仅示出作为gs0输出的地址数据a0以及作为gs7输出的地址数据a7。在图2所示的gs0、gs7中,标注了阴影线的区域表示可以是高电平或者低电平中的任一个的状态。

[0091]

点矩阵型显示装置1具备解码器电路7和驱动器电路8。驱动器电路8包括垂直驱动器电路81和水平驱动器电路82。

[0092]

解码器电路7基于从控制电路6输出的栅极激活信号enb_v,对从垂直变换电路51输出的地址信号gs0~gs7进行解码(decode),生成用于选择多条栅极信号线31中的任一个的地址解码信号dec1~dec256(在统称的情况下,仅记载为“dec”)。从解码器电路7输出的地址解码信号dec被输入至垂直驱动器电路81。

[0093]

例如,如图8所示,解码器电路7具有多个或非(nor)的逻辑门电路(以下,也称为nor电路)71。在本实施方式中,解码器电路7具有与栅极信号线31的条数(256条)相等数量的nor电路71,各nor电路71具有8个输入端子。各nor电路71在所输入的信号的全部为l信号的情况下输出h信号,在所输入的信号中的至少一个为h信号的情况下输出l信号。

[0094]

向各nor电路71输入从垂直变换电路51输出的地址信号gs0~gs7以及地址信号gs0~gs7各自的反相信号xgs0~xgs7所构成的16个信号中的8个信号。对多个nor电路71分别输入不同组合的8个信号。从地址信号gs0~gs7以及反相信号xgs0~xgs7的16个信号选出不同的8个信号的组合为28=256种,因此能够通过输入至解码器电路7的8个信号,从多个nor电路71中的一个nor电路71输出h信号,从其他nor电路71使l信号输出。在本实施方式中,例如,如图8所示,通过在各nor电路71的8个输入端子的前级配置k个(k为0以上且8以下的整数)反相器电路72,从而使地址信号gs反相。对于多个nor电路71中的一个nor电路71,不配置反相器电路72,直接输入地址信号gs。

[0095]

垂直驱动器电路81配置在解码器电路7的后级。例如,如图9a所示,垂直驱动器电路81包括多个与(and)的逻辑门电路(以下,也称为and电路)811,多个and电路811分别配置在解码器电路7的多个nor电路71的后级。

[0096]

各and电路811具有两个输入端子,从与该and电路811连接的nor电路71输出的地址解码信号dec被输入至一方的输入端子,从控制电路6输出的栅极激活信号enb v被输入至另一方的输入端子。多个and电路811的输出端子分别与多条栅极信号线31连接。

[0097]

例如,如图9a所示,在多个and电路811和多条栅极信号线31之间可以配置缓冲电路812。各and电路811在地址解码信号dec以及栅极激活信号enb_v双方为h信号的情况下输出h信号,在地址解码信号dec以及栅极激活信号enb_v中的至少一方为l信号的情况下输出l信号。例如,如图2所示,在栅极激活信号enb_v正在激活(为h信号)的情况下,垂直驱动器电路81能够输出对多条栅极信号线31中的1条进行激活的栅极信号gate。

[0098]

在图9a所示的垂直驱动器电路81中,通过由与非(nand)的逻辑门电路和使该逻辑门电路的输出反相的反相器电路构成and电路811,来抑制电路规模的增大。

[0099]

水平变换电路55基于从水平控制电路63输出的水平开始脉冲信号srin_h,对串行信号si中包括的图像数据d0~d255进行并行变换。例如,如图7a所示,水平变换电路55包括移位寄存器电路56、多个锁存激活信号电路57和多个锁存电路58。

[0100]

移位寄存器电路56与第一时钟信号sclk同步地进行动作。从水平控制电路63输出的水平开始脉冲信号srin_h被输入至移位寄存器电路56。

[0101]

例如,如图7a所示,移位寄存器电路56包括串联连接的多级触发器电路561。此外,例如,如图1所示,多级触发器电路561分别与多个锁存激活信号电路57连接,多个锁存激活信号电路57分别与多个锁存电路58连接。

[0102]

移位寄存器电路56的多级触发器电路561分别具有d端子、ck端子以及q端子。向ck端子输入第一时钟信号sclk。从水平控制电路63输出的水平开始脉冲信号srin_h被输入至第一级的触发器电路561的d端子。多级触发器电路561分别输出水平移位信号srh1~srhm(在统称的情况下,仅记载为“srh”)。在此,m是与源极信号线32的条数相等的正整数,在本实施方式中,m=256。前级的触发器电路561的q端子与第二级以后的触发器电路561的d端子连接。多级触发器电路561的q端子分别与多个锁存激活信号电路57连接。

[0103]

例如,如图7b所示,多个锁存激活信号电路57分别包括反相器电路571、与非(nand)的逻辑门电路(以下,也称为nand电路)572。nand电路572具有两个输入端子,从触发器电路561输出的水平移位信号srh被输入至一方的输入端子,由反相器电路571反相的第一时钟信号sclk被输入至另一方的输入端子。多个锁存激活信号电路57分别向多个锁存电路58输出水平锁存激活信号lth1~lthm(在统称的情况下,仅记载为“lth”)。

[0104]

多个锁存电路58分别具有d端子、ck端子以及q端子,向ck端子输入从与该锁存电路58连接的锁存激活信号电路57输出的水平锁存激活信号lth。此外,向d端子输入从信号供给装置供给的串行信号si。多个锁存电路58在锁存激活信号lth为h信号的期间,分别获取串行信号si中包括的图像数据d0~d255,保持锁存激活信号lth为l信号的期间。例如,如图2所示,多个锁存电路58分别从q端子输出作为数据信号data1~data256的图像数据d0~d255。另外,在图2中,仅表示作为data1输出的图像数据d0以及作为data256输出的图像数据d255。在图2所示的data1、data256中,标注了阴影线的区域表示可以是高电平或者低电平中的任一个的状态。

[0105]

水平驱动器电路82配置在水平变换电路55的后级。例如,如图9b所示,水平驱动器电路82包括多个与(and)的逻辑门电路(以下,也称为and电路)821,多个and电路821分别配置在水平变换电路55的多个锁存电路58的后级。

[0106]

各and电路821具有两个输入端子,从与该and电路821连接的锁存电路58输出的数据信号data被输入至一方的输入端子,从控制电路6输出的数据激活信号enb_h被输入至另一方的输入端子。多个and电路821的输出端子分别与多条源极信号线32连接。

[0107]

例如,如图9b所示,也可以在多个and电路821与多条源极信号线32之间配置缓冲电路822。各and电路821在数据信号data以及数据激活信号enb_h双方为h信号的情况下输出h信号,在数据信号data以及数据激活信号enb_h中的至少一方为l信号的情况下输出l信号。例如,如图2所示,在数据激活信号enb_h正在激活(为h信号)的情况下,水平驱动器电路82能够向多条源极信号线32分别输出写入数据信号sig1~sig256(在统称的情况下,仅记载为“sig”)。

[0108]

在图9b所示的水平驱动器电路中,通过由与非(nand)的逻辑门电路和使该逻辑门电路的输出反相的反相器电路构成and电路821,来抑制电路规模的增大。

[0109]

在本实施方式的点矩阵型显示装置1中,控制电路6特别是计数器电路61与对第一时钟信号sclk进行2分频而得到的第二时钟信号div_clk同步地进行动作。计数器电路61包括规定其动作速度的组合逻辑电路611(图5a中记载)。因此,计数器电路61中的延迟时间t_delay不依赖于第二时钟信号div_clk的时钟周期t2,而仅由计数器电路61的电路结构决定。即,以往,计数器电路61中的组合逻辑电路611成为第一时钟信号sclk的上限频率的限速部。例如,以往,第一时钟信号sclk的上限频率为1.5mhz左右,难以使第一时钟信号sclk的频率比1.5mhz左右高速化。因此,本发明人想到即使使第一时钟信号sclk的频率高速化,只要使计数器电路61以与以往相同程度的频率进行动作即可。为了使计数器电路61与第二时钟信号div_clk同步地正常进行动作,需要满足组合逻辑电路611从接收计数器信号cnt[8:0]到生成下一个计数器信号next_cnt[8:0]为止的延迟时间t_delay为时钟周期t2以下的条件,根据该条件,决定时钟周期t2的最小值t2_min即可。在本实施方式的点矩阵型显示装置1中,例如如图10所示,能够设为tdelay≤t2_min。由于第二时钟信号div_clk是对第一

时钟信号sclk进行2分频而得到的信号,因此第一时钟信号sclk能够使该时钟周期t1的最小值t1_min高速化至t_delay/2。例如,能够将第一时钟信号sclk的频率设为3.0mhz左右,将第二时钟信号div_clk的频率设为1.5mhz左右。

[0110]

在以往的点矩阵型显示装置中,计数器电路与从外部装置供给的外部时钟信号(相当于第一时钟信号sclk)同步地进行动作,因此为了使计数器电路正常地动作,外部时钟信号的周期的最小值与计数器电路的延迟时间相等。

[0111]

由此可知,在本实施方式的点矩阵型显示装置1中,与以往的点矩阵型显示装置相比,能够使第一时钟信号sclk的频率为2倍。根据本实施方式的点矩阵型显示装置1,能够提高第一时钟信号sclk的频率,因此能够缩短串行信号si的传输时间等,使显示控制高速化。

[0112]

此外,在本实施方式的点矩阵型显示装置1中,垂直变换电路51基于垂直开始脉冲信号srin_v和串行输入的串行信号si中包括的地址数据a,生成作为并行信号的地址信号gs。因此,能够简化用于从外部输入地址数据a的布线构造。此外,由于垂直变换电路51将串行输入的地址数据a变换为作为并行信号的地址信号gs并输出,因此能够将地址信号gs的传输时间维持得较短。

[0113]

解码器电路7基于地址信号gs0~gs7生成被供给至多条(256条)栅极信号线31的地址解码信号dec1~dec256。由此,能够通过数量少于栅极信号线31的条数的地址信号gs0~gs7来驱动多条栅极信号线31。因此,能够简化用于从外部输入地址数据a的布线构造,减少垂直变换电路51的电路规模。

[0114]

本公开的计时装置是具备本公开的点矩阵型显示装置1的计时装置,是具备控制经过时间的最小单位的经时控制部的结构。根据该结构,由于具备能够进行高速驱动的本公开的点矩阵型显示装置1,因此能够以1秒单位、0.1秒单位、0.01秒单位、0.001秒单位等那样对经过时间的最小单位进行广泛地控制。因此,本公开的计时装置能够应用于体育运动等运动竞技、汽车赛车以及飞机比赛等速度比赛中使用的秒表、高速摄影设备中使用的时间显示部等。

[0115]

经时控制部也可以是保存在点矩阵型显示装置1的内部或者外部所具备的ic、lsi等驱动元件的ram、rom等存储部中的程序软件。此外,经时控制部也可以是在点矩阵型显示装置1的内部或者外部所具备的电路基板上形成的经时控制电路等。

[0116]

图11是具备本公开的点矩阵型显示装置1的计时装置200的示意性的主视图。点矩阵型显示装置1被组装于计时装置200的显示部201。显示部201具有显示区域202、203、204。计时装置200可以是秒表、具有秒表功能的数字手表、具有秒表功能的智能手表等,图11的例子是具有秒表功能的数字手表。计时装置200在周边部具备计时开始按钮205、计时停止按钮206以及经过时间的最小单位变更按钮207。每当按压按钮207时,经过时间的最小单位经由经时控制部208以1秒单位、0.1秒单位、0.01秒单位、0.001秒单位循环地变更。经时控制部208内置于计时装置200。计时定时由计时开始按钮205以及计时停止按钮206控制,但也可以使用光传感器、红外线传感器等人体感应传感器,电气地控制计时定时。在这种情况下,能够以更高的精度进行计时。

[0117]

根据本公开的点矩阵型显示装置,能够缩短地址数据以及图像数据的传输时间,并且能够使控制改写驱动的控制电路正常地动作。即,即使为了缩短图像数据的传输时间而提高第一时钟信号的时钟频率,控制电路也能够基于频率比第一时钟信号的频率低的第

二时钟信号、例如与以往相同程度的时钟频率的第二时钟信号,控制由变换电路进行的串行并行变换的定时。其结果,能够使控制电路正常地动作。

[0118]

根据本公开的计时装置,由于具备能够高速驱动的本公开的点矩阵型显示装置,因此能够以1秒单位、0.1秒单位、0.01秒单位、0.001秒单位等那样对经过时间的最小单位进行广泛的控制。

[0119]

以上,对本公开的各实施方式进行了详细说明,此外,本公开并不限定于上述的实施方式,在不脱离本公开的主旨的范围内,能够进行各种变更、改良等。当然能够将分别构成上述各实施方式的全部或者一部分适当地在不矛盾的范围内组合。

[0120]-工业可用性-[0121]

本公开的点矩阵型显示装置能够应用于各种电子设备。作为该电子设备,例如有汽车路径引导系统(汽车导航系统)、船舶路径引导系统、飞机路径引导系统、汽车等交通工具的仪表用指示器、隔离面板、智能手机终端、移动电话、平板终端、个人数字助理(pda)、摄影机、数码相机、电子手册、电子书、电子词典、个人计算机、复印机、游戏设备的终端装置、电视、商品显示标签、价格显示标签、产业用的可编程显示装置、汽车音响、数字音频播放器、传真机、打印机、现金自动存取款机(atm)、自动售货机、医疗用显示装置、数字显示式手表、智能手表、车站以及设置于机场等的引导显示装置等。

[0122]-符号说明-[0123]

1 点矩阵型显示装置

[0124]

2 基板

[0125]

3 显示部

[0126]

31 栅极信号线

[0127]

32 源极信号线

[0128]

33 像素电路

[0129]

331 写入开关电路

[0130]

332 锁存电路

[0131]

332a,332b cmos反相器

[0132]

333 像素电位生成电路

[0133]

334 液晶元件

[0134]

334a 像素电极

[0135]

334b 液晶

[0136]

334c 对置电极

[0137]

4 分频电路

[0138]

41 触发器电路

[0139]

42 反相器电路

[0140]

5 变换电路

[0141]

51 垂直变换电路

[0142]

52 移位寄存器电路

[0143]

521 触发器电路

[0144]

53 锁存激活信号电路

[0145]

531 反相器电路

[0146]

532 逻辑门电路(nand电路)

[0147]

54 锁存电路

[0148]

55 水平变换电路

[0149]

56 移位寄存器电路

[0150]

561 触发器电路

[0151]

57 锁存激活信号电路

[0152]

571 反相器电路

[0153]

572 逻辑门电路(nand电路)

[0154]

58 锁存电路

[0155]

6 控制电路

[0156]

61 计数器电路

[0157]

611 组合逻辑电路

[0158]

612 触发器电路

[0159]

62 垂直控制电路

[0160]

621 组合逻辑电路

[0161]

622 触发器电路

[0162]

623 第一单发脉冲电路

[0163]

624 第二单发脉冲电路

[0164]

625 第三单发脉冲电路

[0165]

626 逻辑门电路(or电路)

[0166]

627 rs锁存电路

[0167]

628 组合逻辑电路

[0168]

629 触发器电路

[0169]

63 水平控制电路

[0170]

631 组合逻辑电路

[0171]

632 触发器电路

[0172]

633 第四单发脉冲电路

[0173]

634 第五单发脉冲电路

[0174]

635 rs锁存电路

[0175]

636 组合逻辑电路

[0176]

637 触发器电路

[0177]

7 解码器电路

[0178]

71 逻辑门电路(nor电路)

[0179]

72 反相器电路

[0180]

8 驱动器电路

[0181]

81 垂直驱动器电路

[0182]

811 逻辑门电路(and电路)

[0183]

812 缓冲电路

[0184]

82 水平驱动器电路

[0185]

821 逻辑门电路(and电路)

[0186]

822 缓冲电路

[0187]

200 计时装置

[0188]

201 显示部

[0189]

202、203、204 显示区域

[0190]

205 计时开始按钮

[0191]

206 计时停止按钮

[0192]

207 最小单位变更按钮

[0193]

208 计时控制部。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1