发光二极管显示系统及其运作方法与流程

1.本发明是与显示装置有关,尤其是关于一种发光二极管显示系统及其运作方法。

背景技术:

2.一般而言,传统的微发光二极管集成电路(μic)在实际应用中仍存在着诸多缺点/问题,例如:(1)高耗能(power consumption);(2)低帧率(frame rate);(3)发光二极管在低灰阶的显示效果不佳;(4)所需接脚(pin)的数目难以减少;以及(5)所需行/列驱动器(row/column driver)的数目难以减少,故仍需进一步加以解决及改善。

技术实现要素:

3.有鉴于此,本发明提出一种发光二极管显示系统及其运作方法,以有效解决现有技术所遭遇到的上述问题。

4.依据本发明的一具体实施例为一种发光二极管显示系统。发光二极管显示系统包括传输线及多个发光二极管显示驱动装置。传输线用以传输至少一特定信号。该多个发光二极管显示驱动装置用以于发光二极管导通期间内驱动多个发光二极管单元发光。该多个发光二极管显示驱动装置彼此串接且均耦接传输线,以共用该至少一特定信号。该多个发光二极管显示驱动装置中的第一发光二极管显示驱动装置包括第一数据输入接脚及第一数据输出接脚。第一数据输入接脚用以接收数据信号。第一数据输出接脚用以输出数据信号。

5.于一实施例中,该多个发光二极管显示驱动装置为主动矩阵式微型发光二极管(amμled)显示驱动装置。

6.于一实施例中,该多个发光二极管单元为微型发光二极管(μled)单元。

7.于一实施例中,该至少一特定信号为锁存信号及/或时脉信号。

8.于一实施例中,该多个发光二极管显示驱动装置中的第二发光二极管显示驱动装置包括:第二数据输入接脚,耦接第一数据输出接脚,用以接收第一数据输出接脚所输出的数据信号;以及第二数据输出接脚,用以输出数据信号。

9.于一实施例中,该第一发光二极管显示驱动装置还包括:脉宽调变控制器,用以产生脉宽调变信号;以及驱动电流源,耦接脉宽调变控制器,用以根据脉宽调变信号产生多个驱动电流,以于发光二极管导通期间(led on-time)内驱动该多个发光二极管单元发光。

10.于一实施例中,脉宽调变控制器具有位元选择(bit select)电路架构。

11.于一实施例中,该多个发光二极管显示驱动装置传输数据信号的期间具有传输起始时间与传输结束时间,脉宽调变信号关闭(turn-off)于传输起始时间之前且开启(turn-on)于传输结束时间之后。

12.于一实施例中,该至少一特定信号为锁存信号且其下降沿同步于传输结束时间。

13.于一实施例中,发光二极管显示系统还包括多列彼此串接的发光二极管显示驱动装置。该多列彼此串接的发光二极管显示驱动装置分别传输数据信号的不同期间分别具有

不同的传输起始时间与不同的传输结束时间,该至少一特定信号为锁存信号且其多个下降沿分别同步于该些不同的传输结束时间,且数据输入接脚为单一根或多根。

14.于一实施例中,第一发光二极管显示驱动装置还包括:串列协定界面解码器,耦接第一数据输入接脚,用以对数据信号进行解码;以及移位暂存器(shift register),耦接于串列协定界面解码器与第一数据输出接脚之间,用以传送数据信号至第一数据输出接脚。

15.依据本发明的另一具体实施例为一种发光二极管显示系统运作方法。于此实施例中,发光二极管显示系统运作方法用以运作发光二极管显示系统。发光二极管显示系统包括传输线及彼此串接(cascade)的多个发光二极管显示驱动装置,用以于发光二极管导通期间(led on-time)内驱动多个发光二极管单元发光。该多个发光二极管显示驱动装置中的第一发光二极管显示驱动装置包括第一数据输入接脚及第一数据输出接脚。发光二极管显示系统运作方法包括下列步骤:(a)通过传输线传输至少一特定信号;(b)将该多个发光二极管显示驱动装置均耦接至传输线,以共用该至少一特定信号;以及(c)第一发光二极管显示驱动装置通过第一数据输入接脚接收数据信号并通过第一数据输出接脚输出数据信号。

16.于一实施例中,该多个发光二极管显示驱动装置为主动矩阵式微型发光二极管显示驱动装置。

17.于一实施例中,该多个发光二极管单元为微型发光二极管单元。

18.于一实施例中,该至少一特定信号为锁存信号及/或时脉信号。

19.于一实施例中,该多个发光二极管显示驱动装置中的第二发光二极管显示驱动装置包括第二数据输入接脚及第二数据输出接脚,发光二极管显示系统运作方法还包括下列步骤:通过第二数据输入接脚接收第一数据输出接脚所输出的数据信号;以及通过第二数据输出接脚输出数据信号。

20.于一实施例中,第一发光二极管显示驱动装置还包括脉宽调变控制器及驱动电流源,发光二极管显示系统运作方法还包括:通过脉宽调变控制器产生脉宽调变信号;以及驱动电流源根据脉宽调变信号产生多个驱动电流,以于发光二极管导通期间内驱动该多个发光二极管单元发光。

21.于一实施例中,脉宽调变控制器具有位元选择(bit select)电路架构。

22.于一实施例中,该多个发光二极管显示驱动装置传输数据信号的期间具有传输起始时间与传输结束时间,脉宽调变信号是于传输起始时间之前关闭(turn-off)且于传输结束时间之后开启(turn-on)。

23.于一实施例中,该至少一特定信号为锁存信号且其下降沿(falling edge)同步于该传输结束时间。

24.于一实施例中,发光二极管显示系统还包括多列彼此串接的发光二极管显示驱动装置,该多列彼此串接的发光二极管显示驱动装置分别传输数据信号的不同期间分别具有不同的传输起始时间与不同的传输结束时间,该至少一特定信号为锁存信号且其多个下降沿分别同步于该些不同的传输结束时间,且数据输入接脚为单一根或多根。

25.于一实施例中,第一发光二极管显示驱动装置还包括串列协定界面解码器及移位暂存器。串列协定界面解码器耦接第一数据输入接脚且移位暂存器耦接于串列协定界面解码器与第一数据输出接脚之间。发光二极管显示系统运作方法还包括:通过串列协定界面

解码器对数据信号进行解码;以及通过移位暂存器传送数据信号至第一数据输出接脚。

26.相较于现有技术,本发明的发光二极管显示系统及其运作方法可达到下列优点/功效:(1)低耗能(power consumption);(2)高帧率(frame rate);(3)发光二极管在低灰阶的显示效果佳;(4)有效减少其所需接脚(pin)的数目;以及(5)有效减少其所需行/列驱动器(row/column driver)的数目,故能有效解决现有技术所遭遇到的问题。

27.关于本发明的优点与精神可以通过以下的具体实施方式及所附附图得到进一步的了解。

附图说明

28.图1为依据本发明的一具体实施例的发光二极管显示系统包括传输线及彼此串接(cascade)的多个发光二极管显示驱动装置的示意图。

29.图2为第一发光二极管显示驱动装置的功能方块图。

30.图3为图2中的脉宽调变控制器(pwm controller)具有位元选择(bit select)电路架构的示意图。

31.图4为脉宽调变信号于传输起始时间之前关闭(turn-off)且于传输结束时间之后开启(turn-on)的时序图。

32.图5为锁存信号的下降沿(falling edge)同步于传输结束时间的时序图。

33.图6为不同列的发光二极管显示驱动装置循序地进行数据传输(tx)的时序图。

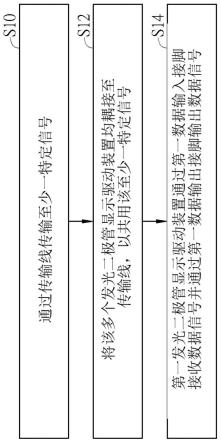

34.图7为依据本发明的一具体实施例的发光二极管显示系统运作方法的流程图。

35.主要元件符号说明:

36.1...发光二极管显示系统

37.μic0~μic3...第一发光二极管显示驱动装置~第四发光二极管显示驱动装置

38.tl...传输线

39.px...像素

40.led...发光二极管

41.pi0~pi3...输入接脚

42.po0~po3...输出接脚

43.vdd...工作电压

44.sdi[3:0]...输入串列数据信号

[0045]

sdo[3:0]...输出串列数据信号

[0046]

lat...锁存信号

[0047]

sclk...串列时脉信号

[0048]

10...时脉与重设产生器

[0049]

11...串列协定界面解码器

[0050]

12...移位暂存器

[0051]

13...储存单元

[0052]

14...暂存设定单元

[0053]

15...脉宽侦测单元

[0054]

16...脉宽调变计数器

[0055]

17...脉宽调变控制器

[0056]

18...偏压单元

[0057]

19...led电流源

[0058]

rst...重设信号

[0059]

sclk_i...输入串列时脉信号

[0060]

sclk_o...输出串列时脉信号

[0061]

rstn...输入重设信号

[0062]

lat_i...输入锁存信号

[0063]

lat_o...输出锁存信号

[0064]

wh...脉宽侦测结果

[0065]

gsd_i...输入数据信号

[0066]

ct_i...输入计数值

[0067]

pwm...脉宽调变信号

[0068]

reg...暂存设定

[0069]

bias...偏压

[0070]

i1~in...驱动电流

[0071]

c1~cn...电流输出端

[0072]

d[n-1:0]、d0~d[n-1]、dl、d[l+1:0]...数据信号

[0073]

a[n-1:0]、a0~a[n-1]、al、a[l+1:0]...控制信号

[0074]

mux0~mux(n-1)、muxl...多工器

[0075]

dff...d型正反器

[0076]

ton...led导通期间

[0077]

pwm0~pwm11...脉宽调变信号

[0078]

ts...传输起始时间

[0079]

te...传输结束时间

[0080]

vsync...垂直同步信号

[0081]

st...控制起始脉波信号

[0082]

tx...数据信号传输期间

[0083]

tx(0)~tx(n-1)...数据信号传输期间

[0084]

w...脉宽调变致能信号

[0085]

sclk[0]~sclk[29]...串列时脉信号

[0086]

dr0~dr29...数据信号

[0087]

dummy...虚设区间

[0088]

sdi...数据输入接脚

[0089]

row0~row29...第一列~第三十列

[0090]

t0~t5...时间

[0091]

s10~s14...步骤

具体实施方式

[0092]

现在将详细参考本发明的示范性实施例,并在附图中说明所述示范性实施例的实例。在附图及实施方式中所使用相同或类似标号的元件/构件是用来代表相同或类似部分。

[0093]

依据本发明的一具体实施例为一种发光二极管显示系统。于此实施例中,发光二极管显示系统包括多个发光二极管显示驱动装置,并且该多个发光二极管显示驱动装置可以是主动矩阵式微型发光二极管(amμled)显示驱动装置(μic)且该多个发光二极管单元可以是微型发光二极管(μled)单元,但不以此为限。

[0094]

如图1所示,图1为此实施例中的发光二极管显示系统1的示意图。如图1所示,发光二极管显示系统1包括传输线tl及彼此串接(cascade)的多个发光二极管显示驱动装置μic0~μic3,但不以此为限。传输线tl是用以传输至少一特定信号(例如锁存信号lat及/或串列时脉信号sclk)。该多个发光二极管显示驱动装置μic0~μic3是用以于发光二极管导通期间内驱动多个发光二极管单元led发光。该多个发光二极管单元led均耦接工作电压vdd。彼此串接(cascade)的该多个发光二极管显示驱动装置μic0~μic3均耦接传输线tl,以共用传输线tl上所传输的该至少一特定信号(例如锁存信号lat及/或串列时脉信号sclk)。

[0095]

若以该多个发光二极管显示驱动装置μic0~μic3中的第一发光二极管显示驱动装置μic0为例进行说明,第一发光二极管显示驱动装置μic0包括第一数据输入接脚pi0及第一数据输出接脚po0。第一数据输入接脚pi0用以接收数据信号(例如输入串列数据信号sdi[3:0])。第一数据输出接脚po0用以输出数据信号(例如输出串列数据信号sdo[3:0])。第一发光二极管显示驱动装置μic0是用以驱动(4x4)像素px的多个发光二极管led,但不以此为限。

[0096]

同理,第二发光二极管显示驱动装置μic1包括第二数据输入接脚pi1及第二数据输出接脚po1。第二数据输入接脚pi1用以接收数据信号sdo[3:0]。第二数据输出接脚po1用以输出数据信号sdo[3:0]。第二发光二极管显示驱动装置μic1是用以驱动(4x4)像素px的多个发光二极管led,但不以此为限。第三发光二极管显示驱动装置μic2包括第三数据输入接脚pi2及第三数据输出接脚po2。第三数据输入接脚pi2用以接收数据信号sdo[3:0]。第三数据输出接脚po2用以输出数据信号sdo[3:0]。第三发光二极管显示驱动装置μic2是用以驱动(4x4)像素px的多个发光二极管led,但不以此为限。第四发光二极管显示驱动装置μic3包括第四数据输入接脚pi3及第四数据输出接脚po3。第四数据输入接脚pi3用以接收数据信号sdo[3:0]。第四数据输出接脚po3用以输出数据信号sdo[3:0]。第四发光二极管显示驱动装置μic3是用以驱动(4x4)像素px的多个发光二极管led,但不以此为限。

[0097]

图2为本发明的第一发光二极管显示驱动装置μic0的功能方块图。如图2所示,第一发光二极管显示驱动装置μic0可包括时脉与重设产生器10、串列协定界面解码器11、移位暂存器12、储存单元13、暂存设定单元14、脉宽侦测单元15、脉宽调变计数器16、脉宽调变控制器17、偏压单元18及led电流源19。串列协定界面解码器11耦接至移位暂存器12。移位暂存器12分别耦接至储存单元13及暂存设定单元14。储存单元13及暂存设定单元14均耦接至脉宽调变控制器17。脉宽侦测单元15耦接至时脉与重设产生器10。脉宽调变计数器16耦接至脉宽调变控制器17。脉宽调变控制器17耦接至led电流源19。偏压单元18耦接至led电流源19。led电流源19分别耦接至n个电流输出端c1~cn,n为正整数。

[0098]

第一发光二极管显示驱动装置μic0分别接收了输入串列时脉信号sclk_i、输入重设信号rstn、输入串列数据信号sdi[3:0]及输入锁存信号lat_i,且第一发光二极管显示驱动装置μic0分别输出了输出串列时脉信号sclk_o、输出串列数据信号sdo[3:0]及输出锁存信号lat_o至第二发光二极管显示驱动装置μic1。

[0099]

当第一发光二极管显示驱动装置μic0接收到输入串列时脉信号sclk_i及输入重设信号rstn时,脉宽侦测单元15侦测输入串列时脉信号sclk_i的脉宽并将脉宽侦测结果wh提供给时脉与重设产生器10,再由时脉与重设产生器10根据输入串列时脉信号sclk_i产生重设信号rst及输出串列时脉信号sclk_o至第一发光二极管显示驱动装置μic0中的各个单元。

[0100]

当第一发光二极管显示驱动装置μic0接收到输入串列数据信号sdi[3:0]及输入锁存信号lat_i时,由串列协定界面解码器11进行解码以产生输出锁存信号lat_o及输出串列数据信号sdo[3:0]后传送至移位暂存器12,再传送至储存单元13及暂存设定单元14。脉宽调变控制器17接收脉宽调变计数器16提供的输入计数值ct_i与储存单元13及暂存设定单元14提供的输入数据信号gsd_i并产生脉宽调变信号pwm至led电流源19。偏压单元18产生偏压bias至led电流源19。led电流源19接收到偏压bias及脉宽调变信号pwm并通过n个电流输出端c1~cn输出n个驱动电流i1~in以驱动发光二极管led发光。同理,第二发光二极管显示驱动装置μic1~第四发光二极管显示驱动装置μic3亦可依此类推,于此不另行赘述。

[0101]

图3为图2中的脉宽调变控制器17具有位元选择(bitselect)电路架构的示意图。如图3所示,脉宽调变控制器17可包括数据排列电路170、位元选择电路bs及d型正反器dff。位元选择电路bs包括彼此串接的n个多工器mux0~mux(n-1)。数据排列电路170接收输入计数值ct_i及输入数据信号gsd_i并分别产生n个数据信号d[n-1:0]及n个控制信号a[n-1:0]。多工器mux0的两输入端分别接收数据信号d0及0并受控于控制信号a0。多工器mux1的两输入端分别接收数据信号d1及多工器mux0的输出信号并受控于控制信号a1。

[0102]

依此类推,多工器mux(n-2)的两输入端分别接收数据信号d(n-2)及多工器mux(n-3)的输出信号并受控于控制信号a(n-2),多工器mux(n-1)的两输入端分别接收数据信号d(n-1)及多工器mux(n-2)的输出信号并受控于控制信号a(n-1)。d型正反器dff的输入端d接收多工器mux(n-1)的输出信号且d型正反器dff的输出端q输出脉宽调变信号pwm。于实际应用中,脉宽调变控制器17中的d型正反器dff所输出的脉宽调变信号pwm可以是打散式脉宽调变(scrambled pwm)信号或分布式脉宽调变(distributed pwm)信号,端视实际需求而定。

[0103]

如图4所示,若以第一发光二极管显示驱动装置μic0为例,第一发光二极管显示驱动装置μic0的数据信号传输期间tx具有传输起始时间ts与传输结束时间te,其脉宽调变信号pwm0是于传输起始时间ts之前关闭(turn-off)且于传输结束时间te之后开启(turn-on),但不以此为限。至于其他发光二极管显示驱动装置亦可依此类推,于此不另行赘述。

[0104]

如图5所示,tx(n-1)至tx(0)分别为第n发光二极管显示驱动装置μic(n-1)至第一发光二极管显示驱动装置μic0的数据信号传输期间,而锁存信号lat的下降沿(falling edge)会同步于传输结束时间t2,但不以此为限。

[0105]

于实际应用中,发光二极管显示系统可包括多列彼此串接的发光二极管显示驱动

装置,分别传输数据信号的不同期间分别具有不同的传输起始时间与不同的传输结束时间,并且锁存信号的多个下降沿可分别同步于该些不同的传输结束时间,且数据输入接脚sdi可以是单一根或多根,但不以此为限。

[0106]

举例而言,如图6所示,假设发光二极管显示系统包括第一列发光二极管显示驱动装置row0~第三十列发光二极管显示驱动装置row30,若以第一列发光二极管显示驱动装置row0来看,其数据信号传输期间tx为时间t0~t1,亦即其传输起始时间为t0且传输结束时间为t1,锁存信号lat的下降沿同步于传输结束时间t1。同理,若以第二列发光二极管显示驱动装置row1来看,其数据信号传输期间tx为时间t1~t2,亦即其传输起始时间为t1且传输结束时间为t2,锁存信号lat的下降沿同步于传输结束时间t2。

[0107]

其余可依此类推,若以第二十九列发光二极管显示驱动装置row28来看,其数据信号传输期间tx为时间t3~t4,亦即其传输起始时间为t3且传输结束时间为t4,锁存信号lat的下降沿同步于传输结束时间t4。同理,若以第三十列发光二极管显示驱动装置row29来看,其数据信号传输期间tx为时间t4~t5,亦即其传输起始时间为t4且传输结束时间为t5,锁存信号lat的下降沿同步于传输结束时间t5。

[0108]

换言之,发光二极管显示系统中的第一列发光二极管显示驱动装置row0至第三十列发光二极管显示驱动装置row29循序地各自进行其数据信号的传输,且锁存信号lat的多个下降沿会分别同步于每一列发光二极管显示驱动装置row0~row29的数据信号传输期间tx的传输结束时间,但不以此为限。

[0109]

依据本发明的另一具体实施例为一种发光二极管显示系统运作方法。于此实施例中,发光二极管显示系统运作方法用以运作发光二极管显示系统。发光二极管显示系统包括传输线及彼此串接(cascade)的多个发光二极管显示驱动装置,用以于发光二极管导通期间(led on-time)内驱动多个发光二极管单元发光。该多个发光二极管显示驱动装置中的第一发光二极管显示驱动装置包括第一数据输入接脚及第一数据输出接脚。实际上,该多个发光二极管显示驱动装置可以是主动矩阵式微型发光二极管(amμled)显示驱动装置且该多个发光二极管单元可以是微型发光二极管(μled)单元,但不以此为限。

[0110]

图7为此实施例中的发光二极管显示系统运作方法的流程图。如图7所示,发光二极管显示系统运作方法可包括下列步骤:

[0111]

步骤s10:通过传输线传输至少一特定信号;

[0112]

步骤s12:将该多个发光二极管显示驱动装置均耦接至传输线,以共用该至少一特定信号;以及

[0113]

步骤s14:第一发光二极管显示驱动装置通过第一数据输入接脚接收数据信号并通过第一数据输出接脚输出数据信号。

[0114]

于实际应用中,脉宽调变控制器可具有位元选择(bit select)电路架构。该至少一特定信号可以是锁存信号及/或时脉信号。该多个发光二极管显示驱动装置中的第二发光二极管显示驱动装置包括第二数据输入接脚及第二数据输出接脚。发光二极管显示系统运作方法还可包括下列步骤:通过第二数据输入接脚接收第一数据输出接脚所输出的数据信号;以及通过第二数据输出接脚输出数据信号。

[0115]

于一实施例中,第一发光二极管显示驱动装置还可包括脉宽调变控制器及驱动电流源。发光二极管显示系统运作方法还可包括:通过脉宽调变控制器产生脉宽调变信号;以

及驱动电流源根据脉宽调变信号产生多个驱动电流,以于发光二极管导通期间内驱动该多个发光二极管单元发光。

[0116]

于一实施例中,该多个发光二极管显示驱动装置传输数据信号的期间具有传输起始时间与传输结束时间。脉宽调变信号是于传输起始时间之前关闭(turn-off)且于传输结束时间之后开启(turn-on)。该至少一特定信号为锁存信号且其下降沿(falling edge)同步于该传输结束时间。

[0117]

于一实施例中,发光二极管显示系统还包括多列彼此串接的发光二极管显示驱动装置,该多列彼此串接的发光二极管显示驱动装置分别传输数据信号的不同期间分别具有不同的传输起始时间与不同的传输结束时间,该至少一特定信号为锁存信号且其多个下降沿分别同步于该些不同的传输结束时间,且数据输入接脚为单一根或多根。

[0118]

于一实施例中,第一发光二极管显示驱动装置还包括串列协定界面解码器及移位暂存器。串列协定界面解码器耦接第一数据输入接脚且移位暂存器耦接于串列协定界面解码器与第一数据输出接脚之间。发光二极管显示系统运作方法还包括:通过串列协定界面解码器对数据信号进行解码;以及通过移位暂存器传送数据信号至第一数据输出接脚。

[0119]

相较于现有技术,本发明的发光二极管显示驱动装置及其运作方法可达到下列优点/功效:(1)低耗能(power consumption);(2)高帧率(frame rate);(3)发光二极管在低灰阶的显示效果佳;(4)有效减少其所需接脚(pin)的数目;以及(5)有效减少其所需行/列驱动器(row/column driver)的数目,故能有效解决现有技术所遭遇到的问题。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1