电压输出控制方法及其系统、显示控制系统和显示装置与流程

1.本发明涉及显示领域,特别涉及一种电压输出控制方法电压输出控制系统、显示控制系统、显示装置、电子设备和计算机可读介质。

背景技术:

2.显示装置一般包括显示控制系统和显示面板(包含源极驱动电路和栅极驱动电路),显示控制系统包括供电模块,其核心组件为电荷泵(charge pump,也称为升压电路),供电模块用于为显示面板提供所需工作电压,该工作电压包括但不限于高电平工作电压vgh、低电平工作电压vgl、参考电压vref、初始化电压vinit、公共电压vcom等。

3.供电模块是按照预先设定的某个工作频率(也称为供电模块的输出频率)来向显示面板提供工作电压,当前供电模块的工作频率是基于对供电模块功耗考量来进行设定。在实际应用中发现,当前供电模块在向显示面板输出工作电压的过程会对显示画面造成一定影响,从而导致显示画面中出现明显云纹(mura)。

技术实现要素:

4.本发明旨在至少解决现有技术中存在的技术问题之一,提出了一种电压输出控制方法电压输出控制系统、显示控制系统、显示装置、电子设备和计算机可读介质。

5.第一方面,本公开实施例提供了一种电压输出控制方法,用于控制供电模块向显示面板提供所需工作电压,所述显示面板显示一帧画面的过程包括依次进行的多个行驱动周期,所述行驱动周期包括:充电时段和非充电时段;在所述充电时段,数据线与对应行的亚像素之间导通以将数据电压写入至对应的亚像素;在所述非充电时段,数据线与所述亚像素之间断路;

6.所述电压输出控制方法,包括:

7.控制所述供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且所述供电模块向显示面板输出工作电压的时间与所述充电时段不存在交叠。

8.在一些实施例中,还包括:检测所述待显示画面是否为第一画面;

9.其中,在检测出所述待显示画面为第一画面时,执行控制所述供电模块在显示待显示画面过程中以预设的第一工作频率进行输出的步骤。

10.在一些实施例中,所述第一画面为重载画面。

11.在一些实施例中,还包括:

12.在检测出所述待显示画面不为第一画面时,控制所述供电模块在显示所述待显示画面中以预设的第二工作频率进行输出;

13.所述第二工作频率小于所述第一工作频率。

14.在一些实施例中,所述控制所述供电模块在显示所述待显示画面过程中以预设的第一工作频率进行输出的步骤包括:

15.在显示所述待显示画面过程中,向所述供电模块发送具有第一时钟频率的第一时

钟信号,以使得所述供电模块以所述第一工作频率进行输出;

16.所述控制所述供电模块在显示所述待显示画面中以预设的第二工作频率进行输出的步骤包括:

17.在显示所述待显示画面过程中,向所述供电模块发送具有第二时钟频率的第二时钟信号,以使得所述供电模块以所述第二工作频率进行输出;

18.所述第二时钟频率小于所述第一时钟频率。

19.在一些实施例中,所述显示面板包括:多列亚像素,每列亚像素配置有对应的一条数据线,位于同一列中的所述亚像素均与对应的所述数据线相连;

20.所述检测待显示画面是否为第一画面的步骤包括:

21.根据所述待显示画面中各列亚像素内不同亚像素的数据电压的变化,确定所述待显示画面的重载程度;

22.根据所述重载程度和预设程度阈值来判断所述待显示画面是否为第一画面;

23.其中,若所述重载程度大于所述预设程度阈值,则判断出所述待显示画面为第一画面;

24.若所述重载程度小于或等于所述预设程度阈值,则判断出所述待显示画面不为第一画面。

25.在一些实施例中,所述显示面板包括呈n行、m列的阵列排布的m*n个亚像素;

26.所述根据所述待显示画面中各列亚像素内不同亚像素的数据电压的变化,确定所述待显示画面的重载程度的步骤包括:

27.计算任意位于同一列且在行方向上相邻的两个亚像素之间的数据电压变化程度,并分别与预设变化程度阈值进行比较,且统计出大于所述预设变化程度阈值的所述数据电压变化程度的频数;

[0028][0029]s(n_m,n+1_m)

表示位于第n行、第m列的亚像素与位于第n+1行、第m列的亚像素之间的数据电压变化程度,v

n_m

表示位于第n行、第m列的亚像素的数据电压,v

n+1_m

表示位于第n+1行、第m列的亚像素的数据电压,n为整数且1≤n≤n-1,m为整数且1≤m≤m;

[0030]

根据大于所述预设变化程度阈值的所述数据电压变化程度的频数确定出所述待显示画面的重载程度;

[0031][0032]

p表示待显示画面的重载程度,k表示大于所述预设变化程度阈值的所述数据电压变化程度的频数。

[0033]

在一些实施例中,所述第一工作频率f1满足:

[0034][0035]

q为整数且1≤n≤5,t0为1个所述行驱动周期所对应的时长。

[0036]

第二方面,本公开实施例还提供了一种电压输出控制系统,用于控制供电模块向

显示面板提供所需工作电压,所述显示面板显示一帧画面的过程包括依次进行的多个行驱动周期,所述行驱动周期包括:充电时段和非充电时段;在所述充电时段,数据线与对应行的亚像素之间导通以将数据电压写入至对应的亚像素;在所述非充电时段,数据线与所述亚像素之间断路。

[0037]

所述电压输出控制系统,包括:

[0038]

第一控制模块,控制所述供电模块在显示所述待显示画面过程中以预设的第一工作频率进行输出,且所述供电模块向显示面板输出工作电压的时间与所述充电时段不存在交叠。

[0039]

在一些实施例中,还包括:

[0040]

检测模块,用于检测待显示画面是否为第一画面;

[0041]

所述第一控制模块具体用于在所述检测模块检测出待显示画面为第一画面时,控制所述供电模块在显示所述待显示画面过程中以预设的第一工作频率进行输出,且所述供电模块向显示面板输出工作电压的时间与所述充电时段不存在交叠。

[0042]

在一些实施例中,所述第一画面为重载画面。

[0043]

在一些实施例中,还包括:

[0044]

第二控制模块,用于在所述检测模块在检测出所述待显示画面不为第一画面时,控制所述供电模块在显示所述待显示画面中以预设的第二工作频率进行输出;所述第二工作频率小于所述第一工作频率。

[0045]

在一些实施例中,所述第一控制模块具体包括:

[0046]

第一时钟输出单元,用于在显示所述待显示画面过程中,向所述供电模块发送具有第一时钟频率的第一时钟信号,以使得所述供电模块以所述第一工作频率进行输出;

[0047]

所述第二控制模块具体包括:

[0048]

第二时钟输出单元,用于在显示所述待显示画面过程中,向所述供电模块发送具有第二时钟频率的第二时钟信号,以使得所述供电模块以所述第二工作频率进行输出;所述第二时钟频率小于所述第一时钟频率。

[0049]

在一些实施例中,所述显示面板包括:多列亚像素,每列亚像素配置有对应的一条数据线,位于同一列中的所述亚像素均与对应的所述数据线相连;

[0050]

所述检测模块包括:

[0051]

确定单元,用于根据所述待显示画面中各列亚像素内不同亚像素的数据电压的变化,确定所述待显示画面的重载程度;

[0052]

判断单元,用于根据所述重载程度和预设程度阈值来判断所述待显示画面是否为第一画面;

[0053]

若所述重载程度大于所述预设程度阈值,则判断出所述待显示画面为第一画面;

[0054]

若所述重载程度小于或等于所述预设程度阈值,则判断出所述待显示画面不为第一画面。

[0055]

在一些实施例中,所述显示面板包括呈n行、m列的阵列排布的m*n个亚像素;

[0056]

所述确定单元包括:

[0057]

第一运算子单元,用于计算任意位于同一列且在行方向上相邻的两个亚像素之间的数据电压变化程度,并分别与预设变化程度阈值进行比较,且统计出大于所述预设变化

程度阈值的所述数据电压变化程度的频数;

[0058][0059]s(n_m,n+1_m)

表示位于第n行、第m列的亚像素与位于第n+1行、第m列的亚像素之间的数据电压变化程度,v

n_m

表示位于第n行、第m列的亚像素的数据电压,v

n+1_m

表示位于第n+1行、第m列的亚像素的数据电压,n为整数且1≤n≤n-1,m为整数且1≤m≤m;

[0060]

第二运算子单元,用于根据大于所述预设变化程度阈值的所述数据电压变化程度的频数确定出所述待显示画面的重载程度;

[0061][0062]

p表示待显示画面的重载程度,k表示大于所述预设变化程度阈值的所述数据电压变化程度的频数。

[0063]

在一些实施例中,所述第一工作频率f1满足:

[0064][0065]

q为整数且1≤n≤5,t0为1个所述行驱动周期所对应的时长。

[0066]

第三方面,本公开实施例还提供了一种显示控制系统,包括:供电模块和如上述第二方面中提供的所述电压输出控制系统。

[0067]

第四方面,本公开实施例还提供了一种显示装置,包括:显示面板和如上述第三方面中通过的所述显示控制系统。

[0068]

第五方面,本公开实施例还提供了一种电子设备,包括:

[0069]

一个或多个处理器;

[0070]

存储器,用于存储一个或多个程序;

[0071]

当所述一个或多个程序被所述一个或多个处理器执行,使得所述一个或多个处理器实现如第一方面中提供的所述电压输出控制方法。

[0072]

在一些实施例中,所述处理器包括现场可编程门阵列。

[0073]

第六方面,本公开实施例还提供了一种计算机可读介质,其上存储有计算机程序,其中,所述计算机程序在被处理器执行时实现如第一方面中提供的所述电压输出控制方法中的步骤。

附图说明

[0074]

图1为本公开技术方案所涉及显示装置的一种系统化结构框图;

[0075]

图2为本公开实施例中一个亚像素的一种电路结构示意图;

[0076]

图3为本公开实施例中一个亚像素的另一种电路结构示意图;

[0077]

图4为本公开实施例中供电模块的一种电路结构示意图;

[0078]

图5为供电模块内部的待输出电压vpph的一种时序示意图;

[0079]

图6为本公开实施例中显示一帧画面的一种时段分布示意图;

[0080]

图7为相关技术中供电模块内部的待输出电压vpph与显示一帧画面的一种时序示

意图;

[0081]

图8为本公开实施例提供的一种电压输出控制方法的流程图;

[0082]

图9a为本公开实施例提供的另一种电压输出控制方法的流程图;

[0083]

图9b为本公开实施例提供的又一种电压输出控制方法的流程图;

[0084]

图10为本公开中供电模块内部的待输出电压vpph与显示一帧画面的一种时序示意图;

[0085]

图11为本公开实施例中步骤s1的一种可选实现方法的流程图;

[0086]

图12为本公开实施例提供的一种电压输出控制系统的结构框图;

[0087]

图13为本公开实施例的一种电子设备的结构示意图。

具体实施方式

[0088]

为使本领域的技术人员更好地理解本发明的技术方案,下面结合附图对本发明提供的一种电压输出控制方法电压输出控制系统、显示控制系统、显示装置、电子设备和计算机可读介质进行详细描述。

[0089]

图1为本公开技术方案所涉及显示装置的一种系统化结构框图,如图1所示,显示面板1和显示控制系统2。

[0090]

其中,按照显示维度来划分,显示面板1可以为2d显示面板或3d显示面板;按照发光类型来划分,显示面板1可以为液晶显示面板(lcd)、发光二极管(led)显示面板、有机发光二极管(oled)显示面板或量子点发光二极管(qled)显示面板。本公开的技术方案对于显示面板的类型和结构不作限定。在本公开实施例中,显示面板包括沿行方向和列方向呈阵列排布的多个亚像素,每个亚像素与对应行栅线和对应列数据线相连;其中,位于同一行的亚像素连接同一条栅线,位于同一列的亚像素连接同一条数据线。

[0091]

显示面板1配置有栅极驱动电路(未示出)和源极驱动电路(未示出);栅极驱动电路用于给栅线提供栅极驱动信号,以对栅线进行扫描驱动;源极驱动电路用于向数据线提供数据电压,以通过数据线将数据电压写入至对应的亚像素,以控制亚像素显示灰阶。

[0092]

图2为本公开实施例中一个亚像素的一种电路结构示意图,如图2所示,该亚像素为液晶显示面板1中的亚像素,包括开关晶体管t0和像素电极,开关晶体管t0的控制极与对应行栅线gate相连,开关晶体管t0的第一极与数据线data相连,开关晶体管t0的第二极与像素电极相连。在栅线gate所提供的驱动信号处于有效电平状态时,开关晶体管t0导通,数据线data中的数据电压写入至像素电极。

[0093]

图3为本公开实施例中一个亚像素的另一种电路结构示意图,如图3所示,该亚像素为led/oled/qled显示面板1中的亚像素,包括:数据写入晶体管t1、驱动晶体管dtft和发光元件el(具体可以为led、oled或qled);数据写入晶体管t1的控制极与对应行栅线gate相连,数据写入晶体管t1的第一极与数据线data相连,数据写入晶体管t1的第二极与驱动晶体管dtft的控制极相连,驱动晶体管dtft的第一极与电源端vdd相连,驱动晶体管dtft的第二极与发光元件el相连。在栅线gate所提供的驱动信号处于有效电平状态时,数据写入晶体管t1导通,数据线data中的数据电压写入至驱动晶体管dtft的控制,驱动晶体管dtft输出相应驱动电路。

[0094]

需要说明的是,本公开实施例中亚像素的电路结构不限于图2和图3中所示,还可

以采用其他电路结构,此处不再一一举例说明。

[0095]

在本公开实施例中,栅极驱动电路具体形式可以为具有栅极驱动功能的芯片(一般称为gate ic),也可以为基于阵列基板工艺直接形成于显示面板的周边区域的电路结构(gate on array,简称为goa)。源极驱动电路具体形式可以为具有源极驱动功能的芯片(一般称为source ic),源极驱动芯片可通过柔性电路版(flexible printed circuit,简称fpc)与显示面板上的连接焊盘绑定(bonding)。本公开的技术方案,对于栅极驱动电路和源极驱动电路的具体结构不作限定。

[0096]

显示控制系统包括电压输出控制系统和供电模块,电压输出控制系统可用于接收待显示画面的显示数据(包括各亚像素的数据电压)以及控制供电模块进行工作。

[0097]

图4为本公开实施例中供电模块的一种电路结构示意图,图5为供电模块内部的待输出电压vpph的一种时序示意图,如图4和图5所示,供电模块4的核心组件为电荷泵,电荷泵包括升压电路401和电压钳位电路402。升压电路401响应于时钟信号clk的控制进行升压工作,将待输出电压vpph逐渐抬升,当待输出电压vpph达到电压钳位电路402的钳位高电压时,也即电荷泵启动完成时,升压电路401使能信号pump_en就从高电平变为低电平,从而将升压电路401关闭,电荷泵将该待输出电压vpph作为工作电压向外输出(输出时长相对较短),即供电模块4向显示面板供电;后续,当待输出电压vpph由于放电等原因降到低于电压钳位电路402的钳位低电压时,升压电路401使能信号pump_en从低电平变成高电平,升压电路401再次启动;如此循环,可以将电荷泵实际所输出的工作电压维持在一个比较稳定的高压上。

[0098]

在实际应用中,为实现供电模块4能够提供不同的工作电压(例如,高电平工作电压vgh、低电平工作电压vgl、参考电压vref、初始化电压vinit、公共电压vcom),则在供电模块4内部可设置多个升压电路401和对应的多个电压钳位电路402(即设置有多个电荷泵),每个升压电路401和对应的电压钳位电路402用于实现一种工作电压的输出。对于供电模块4的具体电路结构,本公开不作限定。

[0099]

图6为本公开实施例中显示一帧画面的一种时段分布示意图,如图6所示,显示面板显示一帧画面的过程包括:像素驱动阶段;在一些实施例中,在像素驱动阶段之后还包括稳定显示阶段(图中未示出)。像素驱动阶段包括:与亚像素行一一对应的多个行驱动周期p0(图6中仅示例性画出了9个行驱动周期p0),多个行驱动周期p0依次进行,每个行驱动周期p0包括:充电时段s2和非充电时段s1。

[0100]

各行驱动周期的起始和结束是由水平同步信号hsync来进行控制。例如,参见图6所示,在水平同步信号hsync由低电平切换至高电平时,表征前一行驱动周期p0的结束以及当前行驱动周期p0的开始。

[0101]

以对某行亚像素进行驱动为例。在该行亚像素所对应的充电时段s2,栅极驱动电路提供有效电平信号,以使得该行亚像素内用于进行数据写入的晶体管(例如,图2中的开关晶体管t0、图3中的数据写入晶体管t1)处于导通状态,各条数据线将相应数据电压vd写入至该行亚像素的各亚像素中(一般也称为数据电压充电写入过程)。在该行亚像素所对应的非充电时段s1,数据线与亚像素之间断路。

[0102]

在一些实施例中,参见图6所示,在一个行驱动周期p0内,在行驱动周期p0的起始时刻至充电时段s2的起始时刻之间会设置一个非充电时段s1(一般也称为充电准备时段);

当前行驱动周期内的充电准备时段,作为当前行驱动周期内充电时段s2与前一行驱动周内充电时段s2之间的行缓冲时段(line buffer)。

[0103]

在另一些实施例中,不仅会在行驱动周期p0的起始时刻至充电时段的起始时刻之间会设置一个非充电时段s1,还会在至充电时段的结束时刻至行驱动周期的结束时刻设置一个非充电时段(一般也称为充电结束稳定时段)。当前行驱动周期p0内的充电准备时段与前一行驱动周期内的充电结束稳定时段,共同作为当前行驱动周期内充电时段s2与前一行驱动周内充电时段s2之间的行缓冲时段(line buffer)。此处情况未给出相应附图。

[0104]

需要说明的是,图6中gn+1~gn+9分别表示第n+1条栅线~第n+9条栅线,也即图6中示意出了行驱动周期p0内第n+1个~第n+9个行驱动周期p0的时序情况。另外,图6中vd_n+1~vd_n+0分别表示某条数据线data提供给位于第n+1行~第n+9行的亚像素的数据电压。

[0105]

图7为相关技术中供电模块内部的待输出电压vpph与显示一帧画面的一种时序示意图,如图7所示,在相关技术中对供电模块的工作频率的设计仅考虑到了功耗因素,一般是在满足阻容延迟要求和供电需求的情况下,将工作频率设置的尽可能小,以达到降低功效的目的。

[0106]

参见图7所示,相关技术所涉及的供电模块输出工作电压的时间,会位于某些行驱动周期内的充电时段,且在不同充电时段内所对应的位置是不同的。例如,图7中供电模块输出工作电压的时间t1是位于第n+4个行驱动周期中充电时段偏后的位置,供电模块输出工作电压的时间t2是位于第n+8个行驱动周期中充电时段偏中间的位置。

[0107]

另外,针对不同帧画面,供电模块输出工作电压的时间所处行驱动周期也不同;例如,在显示当前帧画面中,供电模块输出工作电压的时间是如图7中位于第n+4个行驱动周期和第n+8个行驱动周期;然而,在显示下一帧画面中,供电模块输出工作电压的时间可能是位于第n+3个行驱动周期和第n+7个行驱动周期(未给出相应附图)。

[0108]

供电模块在向显示面板输出工作电压,会对数据线向亚像素写入数据电压的过程产生一定干扰。尤其是当数据线上电压需要发生较大变化(即位于相同列且位于相邻行的两个像素单元所加载数据电压存在较大差异,此时该数据线处于重载状态)时,会将显示面板输出工作电压对亚像素充电的干扰放大,从而导致数据电压无法准确写入至亚像素,进而导致亚像素异常显示,从而最终导致显示面板中产生mura。

[0109]

为有效解决上述技术问题,本公开提供了相应的解决方案。下面将结合具体实施例进行详细描述。

[0110]

图8为本公开实施例提供的一种电压输出控制方法的流程图,如图8所示,该电压输出控制方法应用于电压输出控制系统,该电压输出控制方法用于控制供电模块向显示面板提供所需工作电压,显示面板显示一帧画面的过程包括依次进行的多个行驱动周期,行驱动周期包括:充电时段和非充电时段;在充电时段,数据线与对应行的亚像素之间导通以将数据电压写入至对应的亚像素;在非充电时段,数据线与亚像素之间断路。该电压输出控制方法,包括:

[0111]

步骤s2、控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠。

[0112]

在本公开实施例中,对供电模块的工作频率进行控制,并使得供电模块向显示面板输出工作电压的时间不位于充电时段;也就是说,供电模块输出工作电压的时间(是一段

极短的时间)与亚像素充电时段错开,因此供电模块输出工作电压的过程不会对任意一行亚像素的充电过程产生干扰,能有效避免mura的出现。

[0113]

图9a为本公开实施例提供的另一种电压输出控制方法的流程图,如图9a所示,该电压输出控制方法包括:

[0114]

步骤s1、检测待显示画面是否为第一画面。

[0115]

其中,在步骤s1检测出在检测出待显示画面为第一画面时,则执行下述步骤s2。

[0116]

步骤s2、控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠。

[0117]

在本公开实施例中,“第一画面”为根据需要满足预先所设定一定条件的画面。也就是说,在本公开实施例中,可对满足预先所设定条件的画面,采用步骤s2中的方式进行供电。

[0118]

在一些实施例中,第一画面可以为重载画面;其中,重载画面是指各列亚像素内不同亚像素的数据电压的变化的频率和/或幅度较大的画面;其反映出在显示过程中源极驱动芯片上同一信号通道所输出数据电压的变化频率和幅度较大,这会使得源极驱动芯片的输出难度较大,源极驱动芯片处于高负载状态。

[0119]

在本公开实施例中,在对待检测显示画面进行显示之前,可先检测待显示画面是否为重载画面,并在检测出待显示画面为重载画面时,可对供电模块的工作频率进行控制,并使得供电模块向显示面板输出工作电压的时间不位于充电时段。也就是说,在显示重载画面过程中,供电模块输出工作电压的时间(是一段极短的时间)与亚像素充电时段错开,因此供电模块输出工作电压的过程不会对任意一行亚像素的充电过程产生干扰,能有效避免mura的出现,从而能够保证重载画面的正常显示。

[0120]

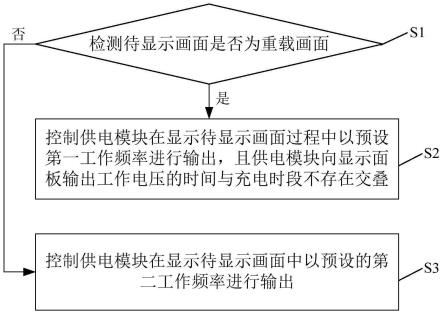

图9b为本公开实施例提供的又一种电压输出控制方法的流程图,如图9b所示,与前面实施例中不同的,在图9a所示实施例中,不仅包括步骤s1和步骤s2,还包括步骤s3。其中,可选地,步骤s1中的第一画面为重载画面。在步骤s1判断出待显示画面为重载画面时,执行步骤s2;在步骤s1判断出待显示画面不为重载画面时,执行步骤s3。下面仅对步骤s3进行详细描述。

[0121]

步骤s3、控制供电模块在显示待显示画面中以预设的第二工作频率进行输出。

[0122]

其中,第二工作频率小于第一工作频率。

[0123]

作为一种具体实施方式,第一工作频率为72khz,第二工作频率为33khz。第一工作频率和第二工作频率的具体取值可根据实际需要来进行设定。

[0124]

在本公开实施例中,当步骤s1检测出待显示画面为重载画面时,控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠,以避免供电模块输出工作电压的过程对亚像素的充电过程产生干扰,保证重载画面的正常显示。当步骤s1检测出待显示画面不为重载画面(即,待显示画面为轻载画面)时,控制供电模块在显示待显示画面中以一个低于第一工作频率的第二工作频率进行输出,由于供电模块的工作频率降低,因此供电模块的功耗相应降低。

[0125]

其中,第二工作频率可以为现有技术中在满足阻容延迟要求和供电需求的情况下将工作频率设置的尽可能小时所采用的工作频率。

[0126]

在步骤s3中,虽然会出现供电模块输出工作电压的时间与充电时段存在交叠的情

况(供电模块输出工作电压的过程对亚像素的充电过程产生干扰),但是由于待显示画面为轻负载画面,故供电模块输出工作电压的过程对亚像素的充电过程所产生干扰相对较小,显示画面出现mura的风险较小且不会出现明显mura。

[0127]

由此可见,本公开的技术方案可以有效避免显示重载画面时出现mura,以及在显示轻载画面时降低功耗。

[0128]

需要说明的是,在检测出待显示画面不为重载画面时,采用步骤s3来控制供电模块在显示待显示画面中以预设的第二工作频率进行输出的情况,仅为本公开实施例中的一种优选实施方案,其能够有效降低功耗。本领域技术人员应该知晓的是,在本公开实施例中,也可以在检测出待显示画面不为重载画面时采用如步骤s2中控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠的方式进行输出(避免供电模块输出工作电压的过程对亚像素的充电过程产生干扰);或者,是控制供电模块采用一个高于第一工作频率的第三工作频率进行输出(提升供电模块的输出能力)。这些情况也均应属于本公开的保护范围。

[0129]

在一些实施例中,步骤s2具体包括:步骤s201。

[0130]

步骤s201在显示待显示画面过程中,向供电模块发送具有第一时钟频率的第一时钟信号,以使得供电模块以第一工作频率进行输出。

[0131]

步骤s3具体包括:步骤s301。

[0132]

步骤s301、在显示待显示画面过程中,向供电模块发送具有第二时钟频率的第二时钟信号,以使得供电模块以第二工作频率进行输出;第二时钟频率小于第一时钟频率。

[0133]

基于前面内容可见,供电模块的工作频率(输出频率)与其内部升压电压所接收到的时钟信号的时钟频率呈正相关。即,供电模块所接收到的时钟信号的时钟频率越高,则供电模块的输出频率越高(时钟频率与供电模块的输出频率的具体映射关系,有供电模块内部结构来决定)。通过控制输出给供电模块的时钟信号的频率,可实现对供电模块的工作频率进行控制。

[0134]

在一些实施例中,第一工作频率f1满足:q为整数且1≤n≤5,t0为1个行驱动周期所对应的时长。

[0135]

图10为本公开中供电模块内部的待输出电压vpph与显示一帧画面的一种时序示意图,如图10所示,在显示重载画面时,供电模块输出工作电压的周期为q*t0,即为1个行驱动周期的整数倍。也就是说,仅需要在显示重载画面过程中供电模块第一次输出工作电压的时间是位于某个行驱动周期内的非充电时段,即可保证供电模块在后续输出工作电压的时间也是一定是位于行驱动周期内的非充电时段。

[0136]

作为一个示例,q取值为2。在图10中,在显示重载画面时,供电模块输出工作电压的时间t1位于第n+3个行驱动周期内的非充电时段,供电模块输出工作电压的时间t2位于第n+5个行驱动周期内的非充电时段,供电模块输出工作电压的时间t3位于第n+7个行驱动周期内的非充电时段,供电模块输出工作电压的时间t4位于第n+9个行驱动周期内的非充电时段。

[0137]

在显示非重载画面时,供电模块采用第二工作频率进行工作。具体内容可参见前面对图7的描述,此处不再赘述。

[0138]

图11为本公开实施例中步骤s1的一种可选实现方法的流程图,如图9a、图9b和图11所示,在一些实施例中,步骤s1包括:

[0139]

步骤s101、根据待显示画面中各列亚像素内不同亚像素的数据电压的变化,确定待显示画面的重载程度。

[0140]

在一些实施例中,显示面板包括呈n行、m列的阵列排布的m*n个亚像素;步骤s101包括:

[0141]

步骤s1011、计算任意位于同一列且在行方向上相邻的两个亚像素之间的数据电压变化程度,并分别与预设变化程度阈值进行比较,且统计出大于预设变化程度阈值的数据电压变化程度的频数。

[0142][0143]s(n_m,n+1_m)

表示位于第n行、第m列的亚像素与位于第n+1行、第m列的亚像素之间的数据电压变化程度,v

n_m

表示位于第n行、第m列的亚像素的数据电压,v

n+1_m

表示位于第n+1行、第m列的亚像素的数据电压,n为整数且1≤n≤n-1,m为整数且1≤m≤m。

[0144]

作为一个示例,预设变化程度阈值的取值一般大于或等于50%,例如55%,60%,65%,70%,80%,85%,90%,95%等,可以根据实际需要进行预先设计和调整。

[0145]

步骤s1012、根据大于预设变化程度阈值的数据电压变化程度的频数确定出待显示画面的重载程度。

[0146][0147]

p表示待显示画面的重载程度,k表示大于预设变化程度阈值的数据电压变化程度的频数。

[0148]

步骤s102、根据重载程度和预设程度阈值来判断待显示画面是否为重载画面。

[0149]

若重载程度大于预设程度阈值,则判断出待显示画面为重载画面;若重载程度小于或等于预设程度阈值,则判断出待显示画面不为重载画面(即为轻载画面)。

[0150]

作为一个示例,预设程度阈值的取值一般大于或等于50%,例如55%,60%,65%,70%,80%,85%,90%,95%等,可以根据实际需要进行预先设计和调整。

[0151]

需要说明的是,上述基于步骤s101和步骤s102来判断显示画面是否为重载画面的情况,仅为本公开实施例中的一种可选实施方式,其不会对本公开的技术方案产生限制。在本领域中“重载画面”属于本领域中的公知词汇,在本公开中还可以采用相关技术中其他算法来判断某个画面是否为重载画面,此处不再赘述。

[0152]

基于同一发明构思,本公开实施例还提供了一种电压输出控制系统,该电压输出控制系统用于控制供电模块向显示面板提供所需工作电压,显示面板显示一帧画面的过程包括依次进行的多个行驱动周期,行驱动周期包括:充电时段和非充电时段;在充电时段,数据线与对应行的亚像素之间导通以将数据电压写入至对应的亚像素;在非充电时段,数据线与亚像素之间断路。

[0153]

图12为本公开实施例提供的一种电压输出控制系统的结构框图,如图12所示,该电压输出控制系统包括:第一控制模块32。

[0154]

第一控制模块32,用于控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠。

[0155]

在一些实施例中,电压输出控制系统还包括:检测模块31;检测模块31用于检测待显示画面是否为第一画面。

[0156]

此时,第一控制模块32具体用于在检测模块检测出待显示画面为第一画面时,控制供电模块在显示待显示画面过程中以预设的第一工作频率进行输出,且供电模块向显示面板输出工作电压的时间与充电时段不存在交叠。

[0157]

在一些实施例中,第一画面为重载画面。

[0158]

进一步地,在一些实施例中,电压输出控制系统还包括:第二控制模块33。其中,第二控制模块33用于在检测模块31在检测出待显示画面不为第一画面时,控制供电模块在显示待显示画面中以预设的第二工作频率进行输出;第二工作频率小于第一工作频率。

[0159]

在一些实施例中,第一控制模块32具体包括:第一时钟输出单元。其中,第一时钟输出单元用于在显示待显示画面过程中,向供电模块发送具有第一时钟频率的第一时钟信号,以使得供电模块以第一工作频率进行输出。

[0160]

第二控制模块33具体包括:第二时钟输出单元。其中,第二时钟输出单元用于在显示待显示画面过程中,向供电模块发送具有第二时钟频率的第二时钟信号,以使得供电模块以第二工作频率进行输出;第二时钟频率小于第一时钟频率。

[0161]

在一些实施例中,第一工作频率f1满足:

[0162][0163]

q为整数且1≤n≤5,t0为1个行驱动周期所对应的时长。在一些实施例中,q取值为2。

[0164]

在一些实施例中,显示面板包括:多列亚像素,每列亚像素配置有对应的一条数据线,位于同一列中的亚像素均与对应的数据线相连;

[0165]

检测模块31包括:确定单元311和判断单元312。其中,确定单元311用于根据待显示画面中各列亚像素内不同亚像素的数据电压的变化,确定待显示画面的重载程度;判断单元312用于根据重载程度和预设程度阈值来判断待显示画面是否为第一画面;若重载程度大于预设程度阈值,则判断出待显示画面为第一画面;若重载程度小于或等于预设程度阈值,则判断出待显示画面不为第一画面。

[0166]

在一些实施例中,显示面板包括呈n行、m列的阵列排布的m*n个亚像素;

[0167]

确定单元311包括:第一运算子单元和第二运算子单元。

[0168]

其中,第一运算子单元用于计算任意位于同一列且在行方向上相邻的两个亚像素之间的数据电压变化程度,并分别与预设变化程度阈值进行比较,且统计出大于预设变化程度阈值的数据电压变化程度的频数;

[0169][0170]s(n_m,n+1_m)

表示位于第n行、第m列的亚像素与位于第n+1行、第m列的亚像素之间的数据电压变化程度,v

n_m

表示位于第n行、第m列的亚像素的数据电压,v

n+1_m

表示位于第n+1

行、第m列的亚像素的数据电压,n为整数且1≤n≤n-1,m为整数且1≤m≤m;。

[0171]

第二运算子单元用于根据大于预设变化程度阈值的数据电压变化程度的频数确定出待显示画面的重载程度;

[0172][0173]

p表示待显示画面的重载程度,k表示大于预设变化程度阈值的数据电压变化程度的频数。

[0174]

对于上述各模块、单元、子单元的具体描述,可参见前面对方法实施例进行描述的相关内容,此处不再赘述。

[0175]

基于同一发明构思,本公开实施例还提供了一种显示控制系统。参见图1所示,该显示控制系统包括:供电模块和电压输出控制系统。其中,电压输出控制系统采用前面实施例所提供的电压输出控制系统,具体内容可参见前面实施例中的内容,此处不再赘述。

[0176]

基于同一发明构思,本公开实施例还提供了一种显示装置。参见图1所示,该显示装置包括:显示面板和显示控制系统。其中,显示控制系统采用前面实施例所提供的显示控制系统,具体内容可参见前面实施例中的内容,此处不再赘述。

[0177]

基于同一发明构思,本公开实施例还提供了一种电子设备。图13为本公开实施例的一种电子设备的结构示意图,如图13所示,本公开实施例提供一种电子设备包括:一个或多个处理器101、存储器102、一个或多个i/o接口103。存储器102上存储有一个或多个程序,当该一个或多个程序被该一个或多个处理器执行,使得该一个或多个处理器实现如上述实施例中任一的电压输出控制方法;一个或多个i/o接口103连接在处理器与存储器之间,配置为实现处理器与存储器的信息交互。

[0178]

其中,处理器101为具有数据处理能力的器件,包括但不限于中央处理器(cpu)等;存储器102为具有数据存储能力的器件,包括但不限于随机存取存储器(ram,更具体如sdram、ddr等)、只读存储器(rom)、带电可擦可编程只读存储器(eeprom)、闪存(flash);i/o接口(读写接口)103连接在处理器101与存储器102间,能实现处理器101与存储器102的信息交互,包括但不限于数据总线(bus)等。

[0179]

在一些实施例中,处理器101、存储器102和i/o接口103通过总线104相互连接,进而与计算设备的其它组件连接。

[0180]

在一些实施例中,该一个或多个处理器101包括现场可编程门阵列。

[0181]

根据本公开的实施例,还提供一种计算机可读介质。该计算机可读介质上存储有计算机程序,其中,该程序被处理器执行时实现如上述实施例中任一的电压输出控制方法中的步骤。

[0182]

特别地,根据本公开实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本公开的实施例包括一种计算机程序产品,包括承载在机器可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信部分从网络上被下载和安装,和/或从可拆卸介质被安装。在该计算机程序被中央处理单元(cpu)执行时,执行本公开的系统中限定的上述功能。

[0183]

需要说明的是,本公开所示的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是——但不

限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本公开中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。而在本公开中,计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于:无线、电线、光缆、rf等等,或者上述的任意合适的组合。

[0184]

附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,前述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

[0185]

描述于本公开实施例中所涉及到的电路或子电路可以通过软件的方式实现,也可以通过硬件的方式来实现。所描述的电路或子电路也可以设置在处理器中,例如,可以描述为:一种处理器,包括:接收电路和处理电路,该处理模块包括写入子电路和读取子电路。其中,这些电路或子电路的名称在某种情况下并不构成对该电路或子电路本身的限定,例如,接收电路还可以被描述为“接收视频信号”。

[0186]

可以理解的是,以上实施方式仅仅是为了说明本公开的原理而采用的示例性实施方式,然而本公开并不局限于此。对于本领域内的普通技术人员而言,在不脱离本公开的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本公开的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1