栅极驱动电路和显示装置的制作方法

本发明涉及显示,尤其涉及一种栅极驱动电路和显示装置。

背景技术:

1、显示行业中,为了降低显示面板材料成本,实现面板的窄边框设计,更多的栅极驱动电路采用goa技术(英文:gate on array,即),这种技术是把栅极驱动电路集成在阵列基板上。在采用goa技术的栅极驱动电路中,其包括的移位寄存器称之为goa单元。

2、goa单元结构较为复杂,占用边缘空间仍然较多,为了进一步优化边缘设计,多级输出的goa单元显得尤为重要,然而相关技术中多级输出的栅极驱动信号的下降时间(falltime)不一致。

技术实现思路

1、本发明的目的在于提供一种栅极驱动电路和显示装置,用于解决采用goa技术的栅极驱动电路中,多级输出的栅极驱动信号的下降时间不一致的问题。

2、为了实现上述目的,本发明提供如下技术方案:

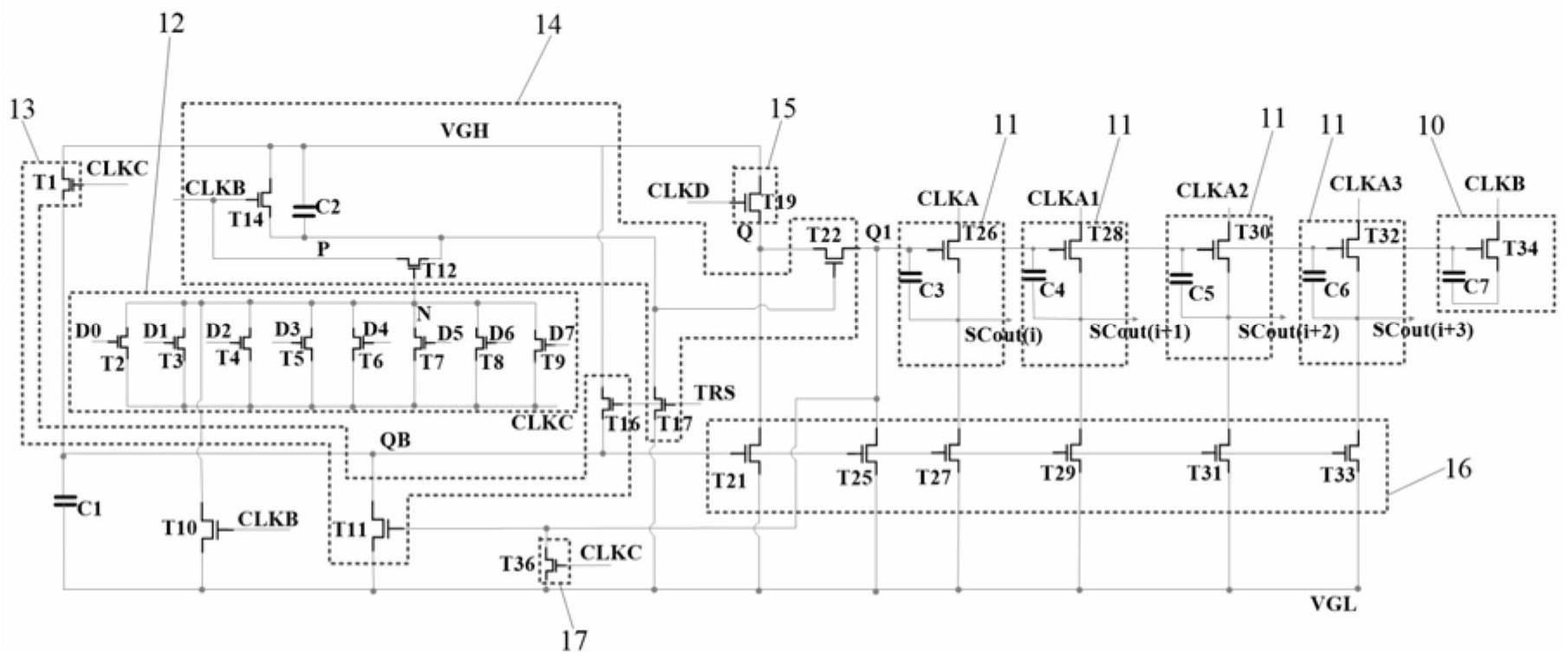

3、本发明的第一方面提供一种栅极驱动电路,包括移位寄存器单元,所述移位寄存器单元包括:上拉节点,补偿模块和至少两个输出模块;

4、各所述输出模块分别与所述上拉节点,对应的第一时钟信号线和对应的栅极驱动信号输出端耦接,用于在所述上拉节点的控制下,控制导通或断开对应的所述第一时钟信号线和所述栅极驱动信号输出端之间的电连接;所述至少两个输出模块对应耦接的栅极驱动信号输出端依次输出栅极驱动信号;

5、所述补偿模块分别与第二时钟信号线和所述上拉节点耦接,用于在所述上拉节点的控制下,控制所述补偿模块是否接入所述第二时钟信号线传输的第二时钟信号;所述补偿模块与所述输出模块结构相同,所述至少两个输出模块耦接的各第一时钟信号线传输的第一时钟信号和所述第二时钟信号线传输的第二时钟信号依次处于有效电平。

6、可选的,所述输出模块包括输出晶体管和输出控制电容,所述输出晶体管的栅极与所述上拉节点耦接,所述输出晶体管的第一极与对应的第一时钟信号线耦接,所述输出晶体管的第二极与对应的栅极驱动信号输出端耦接;所述输出控制电容的第一端与所述输出晶体管的栅极耦接,所述输出控制电容的第二端与所述输出晶体管的第二极耦接;所述输出晶体管与所述上拉节点之间的电容为a*ctft+m1,a为所述输出晶体管的沟道宽度,ctft1为所述输出晶体管的寄生电容的电容值,m1为所述输出控制电容的电容值;

7、所述补偿模块包括补偿晶体管和补偿电容,所述补偿晶体管的栅极与所述上拉节点耦接,所述补偿晶体管的第一极与所述第二时钟信号线耦接,所述补偿晶体管的第二极与所述补偿电容的第二端耦接,所述补偿电容的第一端与所述补偿晶体管的栅极耦接;所述补偿晶体管与所述上拉节点之间的电容为b*ctft2+m2,b为所述补偿晶体管的沟道宽度,ctft2为所述补偿晶体管的寄生电容的电容值,m2为所述补偿电容的电容值;a*ctft+m1=b*ctft2+m2。

8、可选的,所述移位寄存器单元包括:译码器模块,节点置位模块,预控制模块,节点控制模块和复位模块;所述移位寄存器单元还包括:控制节点和下拉节点;

9、所述节点置位模块分别与第一电平信号线,第三时钟信号线,复位信号线,上拉节点,第二电平信号线和所述下拉节点耦接,用于在所述第三时钟信号线和所述复位信号线的控制下,控制导通或断开所述第一电平信号线与所述下拉节点之间的电连接;还用于在所述上拉节点的控制下,控制导通或断开所述下拉节点与所述第二电平信号线之间的电连接;

10、所述预控制模块分别与所述第二时钟信号线,所述第一电平信号线,所述译码器模块的输出端,所述复位信号线,所述第二电平信号线,所述控制节点和所述上拉节点耦接,用于在所述第二时钟信号线,所述译码器模块的输出端和所述复位信号线的控制下,控制导通或断开所述控制节点和所述上拉节点之间的电连接;

11、所述节点控制模块分别与第四时钟信号线,所述第一电平信号线和所述控制节点耦接,用于在所述第四时钟信号线的控制下,控制导通或断开所述第一电平信号线与所述控制节点之间的电连接;

12、所述复位模块分别与所述控制节点,所述上拉节点,所述下拉节点,所述多个栅极驱动信号输出端和所述第二电平信号线耦接,用于在所述下拉节点的控制下,控制导通或断开所述控制节点,所述上拉节点,所述多个栅极驱动信号输出端中的任一个与所述第二电平信号线之间的电连接,还用于在所述上拉节点的控制下,控制导通或断开所述下拉节点与所述第二电平信号线之间的电连接。

13、可选的,所述补偿模块还分别与所述下拉节点和所述第二电平信号线耦接,还用于控制所述补偿模块是否接入所述第二电平信号线传输的第二电平信号。

14、可选的,所述移位寄存器单元还包括:

15、第一辅助下拉模块,所述第一辅助下拉模块分别与所述第三时钟信号线,所述上拉节点和所述第二电平信号线耦接,用于在所述第三时钟信号线的控制下,控制导通或断开所述上拉节点与所述第二电平信号线之间的电连接。

16、可选的,所述预控制模块包括:第二电容,第十二晶体管,第十四晶体管,第十七晶体管和第二十二晶体管;

17、所述第二电容的第一端与所述第一电平信号线耦接;

18、所述第十二晶体管的栅极与所述译码器模块的输出端耦接,所述第十二晶体管的第一极与所述第二时钟信号线耦接,所述第十二晶体管的第二极与所述第二电容的第二端耦接;

19、所述第十四晶体管的栅极与所述第二时钟信号线耦接,所述第十四晶体管的第一极与所述第一电平信号线耦接,所述第十四晶体管的第二极与所述第二电容的第二端耦接;

20、所述第十七晶体管的栅极与所述复位信号线耦接,所述第十七晶体管的第一极与所述第二电容的第二端耦接,所述第十七晶体管的第二极与所述第二电平信号线耦接;

21、所述第二十二晶体管的栅极与所述第二电容的第二端耦接,所述第二十二晶体管的第一极与所述控制节点耦接,所述第二十二晶体管的第二极与所述上拉节点耦接。

22、可选的,所述移位寄存器单元还包括:

23、第一防漏电模块,所述第一防漏电模块分别与所述第一电平信号线,所述第二电容的第二端,所述译码器模块的输出端,所述第十二晶体管的第二极耦接,用于在所述第二电容的第二端的控制下,控制导通或断开所述第一电平信号线与所述第十二晶体管的第二极之间的电连接,还用于在所述译码器模块的输出端的控制下,控制导通或断开所述第十二晶体管的第二极与所述第二电容的第二端之间的电连接。

24、可选的,所述第一防漏电模块包括:第十三晶体管和第十五晶体管;

25、所述第十三晶体管的栅极与所述译码器模块的输出端耦接,所述第十三晶体管的第一极与所述第十二晶体管的第二极耦接,所述第十三晶体管的第二极与所述第二电容的第二端耦接;

26、所述第十五晶体管的栅极与所述第二电容的第二端耦接,所述第十五晶体管的第一极与所述第一电平信号线耦接,所述第十五晶体管的第二极与所述第十二晶体管的第二极耦接。

27、可选的,所述移位寄存器单元还包括:

28、第二防漏电模块,所述第二防漏电模块分别与所述复位信号线,所述第十七晶体管的第一极和所述第二电容的第二端耦接,用于在所述复位信号线的控制下,控制导通或断开所述第十七晶体管的第一极与所述第二电容的第二端之间的电连接;所述第十五晶体管的第二极还与所述第十七晶体管的第一极耦接。

29、可选的,所述复位模块包括:第二十一晶体管,第二十五晶体管,以及多个输出复位晶体管;

30、所述第二十一晶体管的栅极与所述下拉节点耦接,所述第二十一晶体管的第一极与所述控制节点耦接,所述第二十一晶体管的第二极与所述第二电平信号线耦接;

31、所述第二十五晶体管的栅极与所述下拉节点耦接,所述第二十五晶体管的第一极与所述上拉节点耦接,所述第二十五晶体管的第二极与所述第二电平信号线耦接;

32、所述输出复位晶体管的栅极与所述下拉节点耦接,所述输出复位晶体管的第二极与所述第二电平信号线耦接,所述输出复位晶体管的第一极与对应的栅极驱动信号输出端耦接。

33、可选的,所述移位寄存器单元还包括:第三防漏电模块;所述第三防漏电模块分别与所述上拉节点,所述第一电平信号线和所述下拉节点耦接;

34、所述第三防漏电模块还分别与所述控制节点和所述第二十一晶体管的第一极耦接;和/或,所述第三防漏电模块还与所述第二十五晶体管的第一极耦接;

35、所述第三防漏电模块用于在所述上拉节点的控制下,控制导通或断开所述第一电平信号线与所述第二十一晶体管的第一极之间的电连接;还用于在所述下拉节点的控制下,控制导通或断开所述控制节点与所述第二十一晶体管的第一极之间的电连接;和/或,

36、所述第三防漏电模块用于在所述上拉节点的控制下,控制导通或断开所述第一电平信号线与所述第二十五晶体管的第一极之间的电连接;还用于在所述下拉节点的控制下,控制导通或断开所述上拉节点与所述第二十五晶体管的第一极之间的电连接。

37、可选的,所述第三防漏电模块包括第二十三晶体管,所述第三防漏电模块还包括第二十晶体管和/或第二十四晶体管;

38、所述第二十三晶体管的栅极与所述上拉节点耦接,所述第二十三晶体管的第一极与所述第一电平信号线耦接,所述第二十三晶体管的第二极与所述第二十一晶体管的第一极和/或所述第二十五晶体管的第一极耦接;

39、所述第二十晶体管的栅极与所述下拉节点耦接,所述第二十晶体管的第一极与所述控制节点耦接,所述第二十晶体管的第二极与所述第二十一晶体管的第一极耦接;

40、所述第二十四晶体管的栅极与所述下拉节点耦接,所述第二十四晶体管的第一极与所述上拉节点耦接,所述第二十四晶体管的第二极与所述第二十五晶体管的第一极耦接。

41、可选的,所述译码器模块包括多个译码器晶体管,所述译码器晶体管的栅极与所述译码器模块的输入端耦接,所述译码器晶体管的第一极与所述第三时钟信号线耦接,所述译码器晶体管的第二极与所述译码器模块的输出端耦接;

42、所述节点置位模块包括第一晶体管,第十一晶体管和第十六晶体管,所述第一晶体管的栅极与所述第三时钟信号线耦接,所述第一晶体管的第一极与所述第一电平信号线耦接,所述第一晶体管的第二极与所述下拉节点耦接;所述第十一晶体管的栅极与所述上拉节点耦接,所述第十一晶体管的第一极与所述下拉节点耦接,所述第十一晶体管的第二极与所述第二电平信号线耦接;所述第十六晶体管的栅极与所述复位信号线耦接,所述第十六晶体管的第一极与所述第一电平信号线耦接,所述第十六晶体管的第二极与所述下拉节点耦接。

43、所述节点控制模块包括第十九晶体管,所述第十九晶体管的栅极与所述第四时钟信号线耦接,所述第十九晶体管的第一极与所述第一电平信号线耦接,所述第十九晶体管的第二极与所述控制节点耦接。

44、可选的,所述移位寄存器单元还包括:第二辅助下拉模块,所述第二辅助下拉模块分别与所述第二时钟信号线,所述译码器模块的输出端和所述第二电平信号线耦接,用于在所述第二时钟信号线的控制下,控制导通或断开所述译码器模块的输出端与所述第二电平信号线之间的电连接。

45、基于所述栅极驱动电路的技术方案,本发明的第二方面提供一种显示装置,包括上述栅极驱动电路

46、本发明提供的技术方案中,设置移位寄存器单元包括补偿模块和至少两个输出模块。通过设置所述补偿模块与所述输出模块结构相同,使得所述补偿模块与所述输出模块相对于所述上拉节点产生的负载相同;通过设置所述至少两个输出模块耦接的各第一时钟信号线传输的第一时钟信号和所述第二时钟信号线传输的第二时钟信号依次处于有效电平,能够实现在倒数第二个所述第一时钟信号线输出的第一时钟信号的下降沿到来时,所述第二时钟信号的上升沿到来;这样由倒数第二个所述第一时钟信号线输出的第一时钟信号的下降沿对所述上拉节点产生的影响,能够被所述第二时钟信号的上升沿抵消,从而保证了各个输出模块耦接的栅极驱动信号输出端输出的栅极驱动信号的下降时间一致。

47、本发明实施例提供的技术方案中,通过所述上拉节点同时控制各所述输出模块和所述补偿模块,不仅保证了各栅极驱动信号输出端输出的栅极驱动信号的下降时间一致,还保证了所述移位寄存器单元具有精简的结构,有利于显示产品的高分辨率和窄边框化发展。

- 还没有人留言评论。精彩留言会获得点赞!