阵列基板及其检测方法、显示装置与流程

1.本文涉及但不限于显示技术领域,具体涉及一种阵列基板及其检测方法、显示装置。

背景技术:

2.随着显示技术的飞速发展,触摸面板(touch screen panel)已经逐渐遍及人们的生活中。触摸面板按照组成结构可以分为外挂式(add on mode)、覆盖表面式(on cell)、内嵌式(in cell)等。其中,外挂式触摸面板是将触摸模组与显示模组分开生产,然后贴合到一起成为具有触摸功能的触摸面板,存在制作成本较高、光透过率较低、模组较厚等缺点。而内嵌式触摸面板是将触摸模组的触控电极内嵌在显示模组内部,不仅大大减小了模组整体厚度,而且大大降低了制作成本,逐渐成为电容式触摸面板的主流。

3.目前,内嵌式触控显示装置存在像素开口率低等问题。

技术实现要素:

4.以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

5.本公开所要解决的技术问题是,提供一种阵列基板及其检测方法、显示装置,以解决现有内嵌式触控显示装置存在像素开口率低等问题。

6.一方面,本公开提供了一种阵列基板,包括显示区域,所述显示区域至少包括:构成多个触控行和多个触控列的多个触控电极,以及构成多个像素行和多个像素列的多个像素单元,所述触控单元在所述阵列基板上的正投影与多个像素单元在所述阵列基板上的正投影至少部分交叠,所述像素单元包括多个子像素;至少一个相邻的像素列之间设置有触控引线组,所述触控引线组至少包括并列设置的第一引线和第二引线,所述第一引线与一个触控行中的一个触控电极连接,所述第二引线与相邻触控行中的另一个触控电极连接。

7.在示例性实施方式中,至少一个触控列包括沿着所述像素列方向依次设置的n个触控电极,所述触控列在所述阵列基板上的正投影与n/2个像素列在所述阵列基板上的正投影至少部分交叠,位于第i像素列和第i+1像素列之间的第一引线与第2i-1触控行中的触控电极连接,位于第i像素列和第i+1像素列之间的第二引线与第2i触控行中的触控电极连接,n为大于1的偶数,i为大于或等于1、小于或等于n/2的正整数。

8.在示例性实施方式中,至少一个像素单元包括沿着所述像素行方向依次设置的第一子像素、第二子像素和第三子像素,所述子像素包括栅线、数据线、薄膜晶体管和像素电极,所述薄膜晶体管分别与所述栅线、数据线和像素电极连接,所述触控电极复用为公共电极,所述第一引线和第二引线复用为公共电极线;所述第一引线设置在所述第三子像素远离所述第一子像素的一侧,所述第二引线设置在所述第一引线远离所述第一子像素的一侧。

9.在示例性实施方式中,至少一个像素行中,所述第一引线上设置有第一连接块,所

述第一连接块通过第一过孔与一个触控电极连接。

10.在示例性实施方式中,至少一个像素行中,所述第一引线至少包括第一直线段、第二直线段以及位于所述第一直线段和第二直线段之间的弯折段,所述弯折段的第一端与所述第一直线段连接,所述弯折段的第二端与所述第二直线段连接,所述弯折段的中部向着远离所述第二引线的方向凸起,所述第一连接块设置在所述弯折段弯折形成的区域内。

11.在示例性实施方式中,所述第一连接块在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影至少部分交叠。

12.在示例性实施方式中,所述第一过孔在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影至少部分交叠。

13.在示例性实施方式中,至少一个像素行中,所述第二引线上设置有第二连接块,所述第二连接块通过第二过孔与另一个触控电极连接。

14.在示例性实施方式中,至少一个像素行中,所述第一引线至少包括第一直线段、第二直线段以及位于所述第一直线段和第二直线段之间的弯折段,所述弯折段的第一端与所述第一直线段连接,所述弯折段的第二端与所述第二直线段连接,所述弯折段的中部向着远离所述第二引线的方向凸起,所述第二连接块设置在所述弯折段弯折形成的区域内。

15.在示例性实施方式中,所述第二连接块在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影至少部分交叠。

16.在示例性实施方式中,所述第二过孔在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影至少部分交叠。

17.在示例性实施方式中,至少一个像素单元中,所述触控电极包括电极部和连接部,所述电极部设置在所述像素单元内,所述连接部设置在相邻的像素单元之间,且与相邻的像素单元内的电极部连接。

18.在示例性实施方式中,至少一个像素单元中,所述电极部在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影没有交叠,所述电极部在所述阵列基板上的正投影与所述第一引线在所述阵列基板上的正投影没有交叠,所述电极部在所述阵列基板上的正投影与所述第二引线在所述阵列基板上的正投影没有交叠。

19.在示例性实施方式中,至少一个像素单元中,所述连接部在所述阵列基板上的正投影与所述栅线在所述阵列基板上的正投影至少部分交叠,所述连接部在所述阵列基板上的正投影与所述第一引线在所述阵列基板上的正投影至少部分交叠,所述连接部在所述阵列基板上的正投影与所述第二引线在所述阵列基板上的正投影至少部分交叠。

20.在示例性实施方式中,至少一个像素单元中,至少一个连接部通过第一过孔所述第一引线连接,或者,至少一个连接部通过第二过孔与所述第二引线连接。

21.在示例性实施方式中,所述阵列基板还包括位于所述显示区域一侧的绑定区域以及位于所述显示区域远离所述绑定区域一侧的上边框区;所述绑定区域至少包括多个引脚,所述上边框区至少包括测试电路,所述测试电路通过多条连接线与所述绑定区域的多个引脚对应连接,所述测试电路被配置为对所述阵列基板的短路不良进行检测。

22.在示例性实施方式中,所述测试电路包括多个测试单元,多个测试单元与多个触控列的位置相对应;至少一个测试单元包括第一测试线、第二测试线、开关控制线、第一开关和第二开关;所述第一测试线通过所述第一开关与所述显示区域中的第一引线连接,所

述第二测试线通过所述第二开关与所述显示区域中的第二引线连接,所述开关控制线与所述第一开关和第二开关的控制端连接;所述第一测试线被配置为在所述开关控制线的控制下向所述第一引线传输第一灰阶电压,所述第二测试线被配置为在所述开关控制线的控制下向所述第二引线传输第二灰阶电压;所述第一灰阶电压的电压值大于所述第二灰阶电压的电压值,或者,所述第一灰阶电压的电压值小于所述第二灰阶电压的电压值。

23.在示例性实施方式中,所述测试单元还包括第一数据引线、第二数据引线、第三数据引线、第三开关、第四开关和第五开关,所述第一数据引线通过所述第三开关与所述显示区域中第一子像素的数据线连接,所述第二数据引线通过所述第四开关与所述显示区域中第二子像素的数据线连接,所述第三数据引线通过所述第五开关与所述显示区域中第三子像素的数据线连接,所述开关控制线与所述第三开关、第四开关和第五开关的控制端连接;所述第一数据引线、第二数据引线和第三数据引线被配置为在所述开关控制线的控制下向所述显示区域的数据线传输公共基准电压。

24.另一方面,本公开还提供了一种显示装置,包括前述的阵列基板。

25.又一方面,本公开还提供了一种采用前述阵列基板的阵列基板的检测方法,包括:

26.向显示区域中的多条栅线提供开启电压,使得显示区域中多个子像素的薄膜晶体管导通;向所述显示区域中的多条数据线提供公共基准电压,使得所述显示区域中多个子像素的像素电极具有公共基准电压;

27.向所述显示区域中的第一引线提供第一灰阶电压,使得显示区域中与所述第一引线连接的多个触控电极具有第一灰阶电压;向所述显示区域中的第二引线提供第二灰阶电压,使得显示区域中与所述第二引线连接的多个触控电极具有第二灰阶电压;所述第一灰阶电压的电压值大于所述第二灰阶电压的电压值,或者,所述第一灰阶电压的电压值小于所述第二灰阶电压的电压值。

28.在示例性实施方式中,当所述阵列基板上无短路不良时,一个触控行中的触控电极显示第一灰阶,相邻触控行中的触控电极显示第二灰阶,显示区域呈现纵向亮暗相间的显示画面;当所述阵列基板上有短路不良时,一个触控行中的至少一个触控电极与相邻触控行中的至少一个触控电极显示相同的灰阶。

29.本公开所提供的阵列基板及其检测方法、显示装置,通过在相邻的像素单元之间设置触控引线组,触控引线组可以包括并列设置的第一引线和第二引线,减小了引线数量,增加了子像素的空间,提高了像素开口率,有利于显示装置分辨率的提高。

30.在阅读并理解了附图和详细描述后,可以明白其他方面。

附图说明

31.附图用来提供对本公开技术方案的理解,并且构成说明书的一部分,与本公开的实施例一起用于解释本公开的技术方案,并不构成对本公开技术方案的限制。

32.图1为一种液晶显示装置的剖面结构示意图;

33.图2为一种液晶显示装置的平面结构示意图;

34.图3为一种阵列基板的平面结构示意图;

35.图4为一种盒内触摸面板的结构示意图;

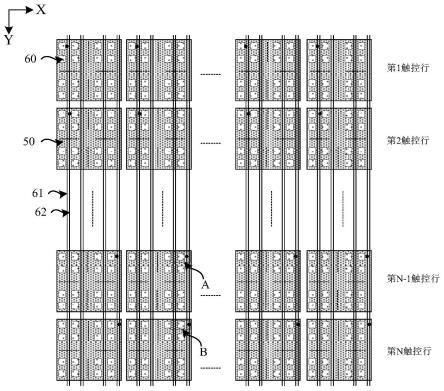

36.图5为本公开示例性实施例一种阵列基板的平面结构示意图;

37.图6为本公开示例性实施例一种显示区域的平面结构示意图;

38.图7a为图6中a区域的放大图;

39.图7b为图6中b区域的放大图;

40.图8a和图8b为本公开阵列基板形成第一导电层图案后的示意图;

41.图9a和图9b为本公开阵列基板形成半导体层图案后的示意图;

42.图10a和图10b为本公开阵列基板形成第二导电层图案后的示意图;

43.图11a和图11b为本公开阵列基板形成第二绝缘层图案后的示意图;

44.图12a和图12b为本公开阵列基板形成第三导电层图案后的示意图;

45.图13a和图13b为本公开阵列基板形成第三绝缘层图案后的示意图;

46.图14为本公开阵列基板中绑定区域和边框区域的平面结构示意图;

47.图15至图19为本公开阵列基板制备测试电路的示意图;

48.图20和图21为本公开检测电路进行短路检测的示意图;

49.图22为本公开检测电路进行短路检测时的检测时序示意图。

50.附图标记说明:

51.10—薄膜晶体管;

ꢀꢀꢀꢀꢀꢀꢀꢀ

20—栅线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21—栅电极;

52.22—有源层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23—源电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24—漏电极;

53.30—数据线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40—像素电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50—触控电极;

54.51—电极部;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

52—连接部;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

53—开口;

55.60—像素单元;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

61—第一引线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

61-1—第一连接块;

56.62—第二引线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

62-1—第二连接块;

ꢀꢀꢀꢀꢀꢀ

70—测试单元;

57.71—第一测试线;

ꢀꢀꢀꢀꢀꢀꢀꢀ

72—第二测试线;

ꢀꢀꢀꢀꢀꢀꢀꢀ

73—第一数据引线;

58.74—第二数据引线;

ꢀꢀꢀꢀꢀꢀ

75—第三数据引线;

ꢀꢀꢀꢀꢀꢀ

76—开关控制线;

59.76-1—第一控制线;

ꢀꢀꢀꢀꢀꢀ

76-2—第二控制线;

ꢀꢀꢀꢀꢀꢀ

76-3—第三控制线;

60.76-4—第四控制线;

ꢀꢀꢀꢀꢀꢀ

76-5—第五控制线;

ꢀꢀꢀꢀꢀꢀ

81—第一连接线;

61.82—第二连接线;

ꢀꢀꢀꢀꢀꢀꢀꢀ

83—第三连接线;

ꢀꢀꢀꢀꢀꢀꢀꢀ

84—第四连接线;

62.85—第五连接线;

ꢀꢀꢀꢀꢀꢀꢀꢀ

91—第一开关;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

92—第二开关;

63.93—第三开关;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

94—第四开关;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

95—第五开关;

64.100—显示区域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

111—第一栅极块;

ꢀꢀꢀꢀꢀꢀꢀ

112—第二栅极块;

65.113—第三栅极块;

ꢀꢀꢀꢀꢀꢀꢀ

114—第四栅极块;

ꢀꢀꢀꢀꢀꢀꢀ

115—第五栅极块;

66.121—第一有源层;

ꢀꢀꢀꢀꢀꢀꢀ

122—第二有源层;

ꢀꢀꢀꢀꢀꢀꢀ

123—第三有源层;

67.124—第四有源层;

ꢀꢀꢀꢀꢀꢀꢀ

125—第五有源层;

ꢀꢀꢀꢀꢀꢀꢀ

131—第一源电极;

68.132—第二源电极;

ꢀꢀꢀꢀꢀꢀꢀ

133—第三源电极;

ꢀꢀꢀꢀꢀꢀꢀ

134—第四源电极;

69.135—第五源电极;

ꢀꢀꢀꢀꢀꢀꢀ

141—第一漏电极;

ꢀꢀꢀꢀꢀꢀꢀ

142—第二漏电极;

70.143—第三漏电极;

ꢀꢀꢀꢀꢀꢀꢀ

144—第四漏电极;

ꢀꢀꢀꢀꢀꢀꢀ

145—第五漏电极;

71.151—第一搭接块;

ꢀꢀꢀꢀꢀꢀꢀ

152—第二搭接块;

ꢀꢀꢀꢀꢀꢀꢀ

153—第三搭接块;

72.154—第四搭接块;

ꢀꢀꢀꢀꢀꢀꢀ

155—第五搭接块;

ꢀꢀꢀꢀꢀꢀꢀ

161—第一搭接电极;

73.162—第二搭接电极;

ꢀꢀꢀꢀꢀ

163—第三搭接电极;

ꢀꢀꢀꢀꢀ

164—第四搭接电极;

74.165—第五搭接电极;

ꢀꢀꢀꢀꢀ

200—绑定区域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

210—第一测试引脚;

75.220—第二测试引脚;

ꢀꢀꢀꢀꢀ

230—第一数据引脚;

ꢀꢀꢀꢀꢀ

240—第二数据引脚;

76.250—第三数据引脚;

ꢀꢀꢀꢀꢀ

260—开关控制引脚;

ꢀꢀꢀꢀꢀ

270—栅线控制引脚;

77.280—驱动芯片;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

300—边框区域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

310—上边框区;

78.320—侧边框区;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

330—栅极驱动电路。

具体实施方式

79.下文中将结合附图对本公开的实施例进行详细说明。注意,实施方式可以以多个不同形式来实施。所属技术领域的普通技术人员可以很容易地理解一个事实,就是方式和内容可以在不脱离本公开的宗旨及其范围的条件下被变换为各种各样的形式。因此,本公开不应该被解释为仅限定在下面的实施方式所记载的内容中。在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互任意组合。

80.本公开中的附图比例可以作为实际工艺中的参考,但不限于此。例如:沟道的宽长比、各个膜层的厚度和间距、各个信号线的宽度和间距,可以根据实际需要进行调整。阵列基板中像素的个数和每个像素中子像素的个数也不是限定为图中所示的数量,本公开中所描述的附图仅是结构示意图,本公开的一个方式不局限于附图所示的形状或数值等。

81.本说明书中的“第一”、“第二”、“第三”等序数词是为了避免构成要素的混同而设置,而不是为了在数量方面上进行限定的。

82.在本说明书中,为了方便起见,使用“中部”、“上”、“下”、“前”、“后”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示方位或位置关系的词句以参照附图说明构成要素的位置关系,仅是为了便于描述本说明书和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。构成要素的位置关系根据描述各构成要素的方向适当地改变。因此,不局限于在说明书中说明的词句,根据情况可以适当地更换。

83.在本说明书中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解。例如,可以是固定连接,或可拆卸连接,或一体地连接;可以是机械连接,或电连接;可以是直接相连,或通过中间件间接相连,或两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本公开中的具体含义。

84.在本说明书中,晶体管是指至少包括栅电极、漏电极以及源电极这三个端子的元件。晶体管在漏电极(漏电极端子、漏区域或漏电极)与源电极(源电极端子、源区域或源电极)之间具有沟道区域,并且电流能够流过漏电极、沟道区域以及源电极。注意,在本说明书中,沟道区域是指电流主要流过的区域。

85.在本说明书中,第一极可以为漏电极、第二极可以为源电极,或者第一极可以为源电极、第二极可以为漏电极。在使用极性相反的晶体管的情况或电路工作中的电流方向变化的情况等下,“源电极”及“漏电极”的功能有时互相调换。因此,在本说明书中,“源电极”和“漏电极”可以互相调换,“源端”和“漏端”可以互相调换。

86.在本说明书中,“连接”包括构成要素通过具有某种电作用的元件连接在一起的情况。“具有某种电作用的元件”只要可以进行连接的构成要素间的电信号的授受,就对其没有特别的限制。“具有某种电作用的元件”的例子不仅包括电极和布线,而且还包括晶体管等开关元件、电阻器、电感器、电容器、其它具有各种功能的元件等。

87.在本说明书中,“平行”是指两条直线形成的角度为-10

°

以上且10

°

以下的状态,因

此,也包括该角度为-5

°

以上且5

°

以下的状态。另外,“垂直”是指两条直线形成的角度为80

°

以上且100

°

以下的状态,因此,也包括85

°

以上且95

°

以下的角度的状态。

88.在本说明书中,“膜”和“层”可以相互调换。例如,有时可以将“导电层”换成为“导电膜”。与此同样,有时可以将“绝缘膜”换成为“绝缘层”。

89.本说明书中三角形、矩形、梯形、五边形或六边形等并非严格意义上的,可以是近似三角形、矩形、梯形、五边形或六边形等,可以存在公差导致的一些小变形,可以存在导角、弧边以及变形等。

90.本公开中的“约”,是指不严格限定界限,允许工艺和测量误差范围内的数值。

91.液晶显示装置(liquid crystal display,简称lcd)具有体积小、功耗低、无辐射等特点,已得到广泛应用。液晶阵列基板包括对盒(cell)的薄膜晶体管阵列(thin film transistor,简称tft)基板和彩膜(color filter,简称cf)基板,液晶(liquid crystal,简称lc)分子设置在阵列基板和彩膜基板之间,通过控制公共电极和像素电极来形成驱动液晶偏转的电场,实现灰阶显示。

92.图1为一种液晶显示装置的剖面结构示意图。如图1所示,液晶显示装置可以包括相对设置的第一基板a1和第二基板a2,以及设置在第一基板a1与第二基板a2之间的液晶层a3,第一基板a1可以包括设置在第一基底a1-1朝向第二基板a2一侧的第一结构层a1-2,第二基板a2可以包括设置在第二基底a2-1朝向第一基板a1一侧的第二结构层a2-2。按照显示模式,液晶显示装置可以分为扭曲向列(twisted nematic,tn)显示模式、平面转换(in plane switching,ips)显示模式、边缘场开关(fringe field switching,ffs)显示模式和高级超维场转换(advanced super dimension switch,ads)显示模式等。对于ads显示模式,在示例性实施方式中,第一结构层a1-2可以包括栅线、数据线、薄膜晶体管、像素电极和公共电极,第二结构层a2-2可以包括黑矩阵和滤光单元。

93.图2为一种液晶显示装置的平面结构示意图。如图2所示,液晶显示装置可以包括以矩阵方式排布的多个像素单元60,多个像素单元60的至少一个可以包括出射第一颜色光线的第一子像素p1、出射第二颜色光线的第二子像素p2和出射第三颜色光线的第三子像素p3,三个子像素可以均包括薄膜晶体管、像素电极和公共电极。在示例性实施方式中,第一子像素p1可以是出射红色(r)光线的红色子像素,第二子像素p2可以是出射绿色(g)光线的绿色子像素,第三子像素p3可以是出射蓝色(b)光线的蓝色子像素,像素单元中子像素的形状可以是矩形状、菱形、五边形或六边形等,像素单元中子像素可以采用水平并列、竖直并列或品字方式排列。在示例性实施方式中,像素单元可以包括四个子像素,本公开在此不做限定。

94.图3为一种阵列基板的平面结构示意图。如图3所示,在示例性实施方式中,阵列基板可以包括显示区域和边框区域,显示区域可以包括多条栅线(s1到sm)和多条数据线(d1到dn),多条栅线可以沿着水平方向延伸并沿着竖直方向依次设置,多条数据线可以沿着竖直方向延伸并沿着水平方向依次设置,相互交叉的多条栅线和多条数据线限定出规则排布的多个子像素pxij,m、n、i和j可以是自然数。在示例性实施方式中,至少一个子像素pxij可以包括薄膜晶体管、像素电极和公共电极,薄膜晶体管分别与栅线、数据线和像素电极连接。

95.在示例性实施方式中,阵列基板还可以包括多条公共电极线(e1到eo),多条公共

电极线可以沿着水平方向延伸并沿着竖直方向依次设置或者多条公共电极线可以沿着竖直方向延伸并沿着水平方向依次设置,多条公共电极线与多个子像素pxij中的公共电极对应连接。

96.在示例性实施方式中,多条栅线与扫描驱动器连接,多条数据线与数据驱动器连接,扫描驱动器和数据驱动器的至少一部分可以形成在阵列基板上。

97.在示例性实施方式中,外部控制装置(如时序控制器)可以将适合于数据驱动器的规格的灰度值和控制信号提供到数据驱动器,数据驱动器可以利用接收的灰度值和控制信号来产生将提供到数据线d1、d2、d3、

……

和dn的数据电压。例如,数据驱动器可以利用时钟信号对灰度值进行采样,并且以像素行为单位将与灰度值对应的数据电压施加到数据线d1至dn。外部控制装置可以将适合于扫描驱动器的规格的时钟信号、扫描起始信号等提供到扫描驱动器,扫描驱动器可以利用时钟信号、扫描起始信号等来产生将提供到扫描信号线s1、s2、s3、

……

和sm的扫描信号。例如,扫描驱动器可以将具有导通电平脉冲的扫描信号顺序地提供到扫描信号线s1至sm。例如,扫描驱动器可以被构造为移位寄存器的形式,并且可以以在时钟信号的控制下顺序地将以导通电平脉冲形式提供的扫描起始信号传输到下一级电路的方式产生扫描信号。

98.在示例性实施方式中,集成触摸功能的液晶显示装置主要包括on cell结构和in cell结构。on cell结构通常是将触摸结构设置在彩膜基板远离阵列基板的一侧,in cell结构通常是将触摸结构设置在阵列基板的第一结构层中。与on cell结构相比,in cell结构能够实现液晶显示装置的轻薄化。

99.在示例性实施方式中,in cell结构主要分为互容式(mutual capacitance)结构和自容式(self capacitance)结构,互容式结构是由驱动电极和感应电极相互重叠或者靠近构成互电容,利用互电容的变化进行位置检测,自容式结构是由触控电极与人体构成自电容,利用自电容的变化进行位置检测。与互容式结构相比,自容式结构为单层结构,具有功耗低和结构简单等特点。

100.图4为一种盒内触摸面板的结构示意图。如图4所示,盒内触摸面板(in-cell touch lcd)可以包括规则排布的多个触控电极50和多条触控引线(也称感测信号线,tx信号线)50a,每个触控电极50通过触控引线50a与触控驱动电路连接。工作时,人手指的触摸会导致相应触控电极50的自电容发生变化,触控驱动电路根据触控电极50的电容变化来判断手指的具体位置。在示例性实施方式中,盒内触摸面板采用提供公共电压的公共电极层作为触控层,将公共电极层进行“分割”形成图4所示块状的触控电极50。在示例性实施方式中,触控电极的形状可以是矩形、菱形、三角形或多边形等,本公开在此不做限定。

101.在示例性实施方式中,图4所示的盒内触摸面板采用分时驱动的工作方式,显示时段和触控时段的驱动信号分开处理。在显示时段内,数据线由数据驱动器供给显示信号,触控电极复用为公共电极,触控信号线复用为公共电极线,触控信号线向触控电极提供公共电压,不进行触控信号扫描,确保正常显示。在触控时段内,触控驱动电路通过触控信号线进行触控信号扫描,此时一帧显示已经完成,显示状态基本不受触控信号影响,两者分时独立工作。

102.在示例性实施方式中,一个触控电极可以约为4*4mm或5*5mm的矩形,可以覆盖多个子像素,由一根触控引线控制,触控引线可以设置在相邻的子像素之间。由于一个触控电

极覆盖多个子像素,触控引线的数量远小于触控电极覆盖的子像素的数量,因而为了避免一些子像素之间设置有触控引线而另一些子像素之间没有设置触控引线,保证像素结构的一致性和刻蚀均一性,现有阵列基板通常是在每个相邻的子像素之间都设置了引线,这些引线的一部分作为控制触控电极的触控引线,其余部分均为虚设(dummy)线,虚设线无信号输入。

103.近年来,高分辨率显示装置逐渐成为行业发展趋势。显示装置的分辨率(pixels per inch,简称ppi)与阵列基板的像素开口率有关,像素开口率越高,显示装置的分辨率越高。经本技术的发明人研究发现,由于现有阵列基板的相邻子像素之间设置了触控引线或者虚设线,大量虚设线占用了子像素的空间,因而现有阵列基板存在像素开口率低等问题,影响了显示装置分辨率的提高。

104.本公开示例性实施例提供了一种阵列基板,包括显示区域,所述显示区域至少包括:构成多个触控行和多个触控列的多个触控电极,以及构成多个像素行和多个像素列的多个像素单元,所述触控单元在所述阵列基板上的正投影与多个像素单元在所述阵列基板上的正投影至少部分交叠,所述像素单元包括多个子像素;至少一个相邻的像素列之间设置有触控引线组,所述触控引线组至少包括并列设置的第一引线和第二引线,所述第一引线与一个触控行中的一个触控电极连接,所述第二引线与相邻触控行中的另一个触控电极连接。

105.在示例性实施方式中,至少一个触控列包括沿着所述像素列方向依次设置的n个触控电极,所述触控列在所述阵列基板上的正投影与n/2个像素列在所述阵列基板上的正投影至少部分交叠,位于第i像素列和第i+1像素列之间的第一引线与第2i-1触控行中的触控电极连接,位于第i像素列和第i+1像素列之间的第二引线与第2i触控行中的触控电极连接,n为大于1的偶数,i为大于或等于1、小于或等于n/2的正整数。

106.在示例性实施方式中,至少一个像素单元包括沿着所述像素行方向依次设置的第一子像素、第二子像素和第三子像素,所述子像素包括栅线、数据线、薄膜晶体管和像素电极,所述薄膜晶体管分别与所述栅线、数据线和像素电极连接,所述触控电极复用为公共电极,所述第一引线和第二引线复用为公共电极线;所述第一引线设置在所述第三子像素远离所述第一子像素的一侧,所述第二引线设置在所述第一引线远离所述第一子像素的一侧。

107.在示例性实施方式中,所述阵列基板还包括位于所述显示区域一侧的绑定区域以及位于所述显示区域远离所述绑定区域一侧的上边框区;所述绑定区域至少包括多个引脚,所述上边框区至少包括测试电路,所述测试电路通过多条连接线与所述绑定区域的多个引脚对应连接,所述测试电路被配置为对所述阵列基板的短路不良进行检测。

108.在示例性实施方式中,所述测试电路包括多个测试单元,多个测试单元与多个触控列的位置相对应;至少一个测试单元包括第一测试线、第二测试线、开关控制线、第一开关和第二开关;所述第一测试线通过所述第一开关与所述显示区域中的第一引线连接,所述第二测试线通过所述第二开关与所述显示区域中的第二引线连接,所述开关控制线与所述第一开关和第二开关的控制端连接;所述第一测试线被配置为在所述开关控制线的控制下向所述第一引线传输第一灰阶电压,所述第二测试线被配置为在所述开关控制线的控制下向所述第二引线传输第二灰阶电压;所述第一灰阶电压的电压值大于所述第二灰阶电压

的电压值,或者,所述第一灰阶电压的电压值小于所述第二灰阶电压的电压值。

109.在示例性实施方式中,所述测试单元还包括第一数据引线、第二数据引线、第三数据引线、第三开关、第四开关和第五开关,所述第一数据引线通过所述第三开关与所述显示区域中第一子像素的数据线连接,所述第二数据引线通过所述第四开关与所述显示区域中第二子像素的数据线连接,所述第三数据引线通过所述第五开关与所述显示区域中第三子像素的数据线连接,所述开关控制线与所述第三开关、第四开关和第五开关的控制端连接;所述第一数据引线、第二数据引线和第三数据引线被配置为在所述开关控制线的控制下向所述显示区域的数据线传输公共基准电压。

110.图5为本公开示例性实施例一种阵列基板的平面结构示意图。如图5所示,阵列基板可以包括显示区域100、位于显示区域100一侧的绑定区域200以及位于显示区域100其它侧的边框区域300。在示例性实施方式中,显示区域100可以是平坦的区域,包括组成像素阵列的多个像素单元和组成触控阵列的多个触控电极,多个像素单元被配置为显示动态图片或静止图像,多个触控电极被配置为实现触摸控制。在示例性实施方式中,显示区域100可以称为有效区域(aa)。

111.在示例性实施方式中,绑定区域200可以至少包括沿着远离显示区域方向依次设置的扇出区、驱动芯片区和绑定引脚区,扇出区可以连接到显示区域100,可以至少包括数据传输线和触控传输线,多条数据传输线被配置为以扇出走线方式连接显示区域的数据线,多条触控传输线被配置为连接显示区域的触控走线。驱动芯片区可以连接到扇出区,可以至少包括集成电路(integrated circuit,简称ic),集成电路被配置为与多条数据传输线和多条触控传输线连接。绑定引脚区可以连接到驱动芯片区,可以至少包括多个引脚(pin),多个引脚被配置为与外部的柔性线路板(flexible printed circuit,简称fpc)绑定连接。

112.在示例性实施方式中,边框区域300可以包括位于显示区域100远离绑定区域200一侧的上边框区310和位于显示区域100两侧的侧边框区320。上边框区310可以至少包括测试电路,测试电路与显示区域中的多条数据线和触控走线连接,测试电路被配置为对阵列基板的短路不良进行检测。侧边框区320可以包括沿着远离显示区域100的方向依次设置的电路区和引线区。电路区可以连接到显示区域100,可以至少包括多个级联的栅极驱动电路(goa),栅极驱动电路与显示区域100中的多条栅线连接。引线区可以连接到电路区,可以至少包括多条连接线,多条连接线的第一端可以与绑定区域200的多个引脚连接,多条连接线的第二端可以与上边框区310的测试电路连接,使得外部测试装置通过多条连接线将测试信号传输到测试电路。

113.图6为本公开示例性实施例一种显示区域的平面结构示意图。如图6所示,在示例性实施方式中,阵列基板的显示区域可以至少包括构成多个触控行和多个触控列的多个触控电极50以及构成多个像素行和多个像素列的多个像素单元60,多个像素单元60构成像素阵列,被配置为显示动态图片或静止图像,多个触控电极50构成触控阵列,被配置为实现触摸控制。每个触控行可以包括多个沿着第一方向x依次设置的多个触控电极50,多个触控行可以沿着第二方向y间隔设置,每个触控列可以包括多个沿着第二方向y依次设置的多个触控电极50,多个触控列可以沿着第一方向x间隔设置。每个像素行可以包括多个沿着第一方向x依次设置的多个像素单元60,多个像素行可以沿着第二方向y间隔设置,每个像素列可

以包括多个沿着第二方向y依次设置的多个像素单元60,多个像素列可以沿着第一方向x间隔设置。在示例性实施方式中,第一方向x与第二方向y交叉。

114.在示例性实施方式中,至少一个触控电极50在阵列基板上的正投影可以包含多个像素单元60在阵列基板上的正投影,即一个触控电极50可以覆盖多个像素单元60,像素单元60可以包括多个子像素。

115.在示例性实施方式中,显示区域可以包括n个触控行,即一个触控列中可以包括沿着第二方向y依次设置的n个触控电极50。至少一个触控列在阵列基板上的正投影与n/2个像素列在阵列基板上的正投影至少部分交叠,即一个触控列的n个触控电极50的位置可以与n/2个像素列的多个像素单元60的位置相对应,n为大于1的偶数。

116.在示例性实施方式中,与一个触控列相对应的n/2个像素列中,至少一个相邻的像素列之间设置有触控引线组。在示例性实施方式中,触控引线组可以包括第一引线61和第二引线62。第一引线61和第二引线62的形状可以为沿着第二方向y(像素列方向)延伸的线形状,第二引线62可以设置在第一引线61第一方向x(像素行方向)的一侧。

117.在示例性实施方式中,对于位于第i像素列和第i+1像素列之间的第一引线61和第二引线62,第一引线61可以与第2i-1触控行中的触控电极50连接,第二引线62可以与第2i触控行中的触控电极50连接,i为大于或等于1、小于或等于n/2的正整数。

118.在示例性实施方式中,当多条第一引线61与奇数的触控行中的触控电极50连接时,多条第二引线62则与偶数的触控行中的触控电极50连接。当多条第一引线61与偶数的触控行中的触控电极50连接时,多条第二引线62则与奇数的触控行中的触控电极50连接。

119.在示例性实施方式中,对于图6所示左侧的第一触控列,该触控列与n/2个像素列相对应。对于第1像素列与第2像素列之间的第一引线61和第二引线62,第一引线61与该触控列的第1个触控电极50(第1触控行的触控电极50)连接,第二引线62与该触控列的第2个触控电极50(第2触控行的触控电极50)连接。对于第2像素列与第3像素列之间的第一引线61和第二引线62,第一引线61与该触控列的第3个触控电极50(第3触控行的触控电极50)连接,第二引线62与该触控列的第4个触控电极50(第4触控行的触控电极50)连接。对于第(n/2)像素列与第n/2+1像素列之间的第一引线61和第二引线62,第一引线61与该触控列的第n-1个触控电极50(第n-1触控行的触控电极50)连接,第二引线62与该触控列的第n个触控电极50(第n触控行的触控电极50)连接。其中,第n/2+1像素列是第2触控列所对应的第1像素列。

120.在示例性实施方式中,一个像素单元60可以包括3个子像素或者可以包括4个子像素。以像素单元60包括沿着第一方向x依次设置的第一子像素、第二子像素和第三子像素为例,第一引线61和第二引线62可以设置在第i像素列的第三子像素与第i+1像素列的第一子像素之间,而每个像素列中的第一子像素与第二子像素之间、第二子像素与第三子像素之间均没有设置第一引线,也没有设置第二引线。

121.在示例性实施方式中,显示区域可以包括多个触控列,每个触控列以及对应的多个像素列的结构可以与第一触控列相同。

122.在示例性实施方式中,在垂直于阵列基板的平面上,阵列基板可以包括基底和设置在基底上的多个导电层,第一引线61和第二引线62可以设置在相同的一个导电层中,触控电极50可以设置在另一个导电层中,第一引线61和第二引线62可以通过过孔与触控电极

50连接。

123.一种阵列基板中,引线通常设置在每个相邻的子像素之间,即包括3个子像素的一个像素单元中设置了3条引线,一些引线作为触控引线,另一些引线作为虚设线。由于每条引线均会占用子像素的空间,因而该结构的阵列基板存在像素开口率低等问题,影响了显示装置分辨率的提高。本公开示例性实施例所提供的阵列基板,通过在相邻的像素单元之间设置2条触控引线,因而一个像素单元仅包括2条触控引线。与像素单元中设置3条引线相比,本公开不仅减小了引线数量,增加了子像素的空间,提高了像素开口率,且提高了阵列基板的透光率,有利于显示装置分辨率的提高,而且由于每条引线均与相应的触控电极通过过孔连接,保证了像素结构的一致性和刻蚀均一性,有利于提高制备工艺的质量。

124.在示例性实施方式中,图6所示结构仅仅是一种示例性说明,可以根据实际需要变更相应结构。例如,触控引线组可以包括3条触控引线或者多条触控引线。由于现有阵列基板是将3条引线分别设置在子像素之间,而本公开将3条触控引线设置在相邻的像素单元之间,同样可以增加子像素的空间,提高像素开口率,有利于显示装置分辨率的提高。又如,可以将2个像素单元或者多个像素单元作为一个重复单元,触控引线组可以设置在相邻的重复单元之间,本公开在此不做限定

125.图7a为图6中a区域的放大图,图7b为图6中b区域的放大图。其中,a区域的像素单元是第m1像素行、第n像素列的像素单元,b区域的像素单元是第m2像素行、第n像素列的像素单元,a区域的像素单元和b区域的像素单元均包括沿着第一方向x依次设置的第一子像素p1、第二子像素p2和第三子像素p3。

126.在示例性实施方式中,阵列基板的显示区域可以至少包括多条栅线20和多条数据线30,栅线20的形状可以是沿着第一方向x延伸的线形状,多条栅线20可以沿着第二方向y依次设置,数据线30的形状可以是沿着第二方向y延伸的线形状,多条数据线30可以沿着第一方向x依次设置,相互交叉的多条栅线20和多条数据线30限定出规则排布的多个子像素,每个子像素中设置有薄膜晶体管和像素电极,薄膜晶体管可以分别与栅线20、数据线30和像素电极连接。

127.在示例性实施方式中,阵列基板的显示区域还可以包括复用为公共电极线的多个触控引线组,以及复用为公共电极的多个触控电极50。触控引线组可以设置在第一方向x上相邻的像素单元之间,至少一个触控引线组可以至少包括并列设置的第一引线61和第二引线62,第一引线61和第二引线62分别与相应的触控电极50连接。

128.在示例性实施方式中,每个子像素中的薄膜晶体管被配置为在栅线20的控制下,接收数据线30传输的数据电压并向像素电极输出,控制像素电极和公共电极之间形成驱动液晶偏转的电场,实现灰阶显示。

129.在示例性实施方式中,第一引线61和第二引线62的形状可以为沿着第二方向y延伸的折线状。在一个像素行(如第m1像素行)中,第一引线61可以通过第一过孔k1与一个触控电极50连接。在另一个像素行(如第m2像素行)中,第二引线62可以通过第二过孔k2与另一个触控电极50连接。

130.在示例性实施方式中,在一个像素行中,第一引线61上可以设置有第一连接块61-1,第一连接块61-1可以通过第一过孔k1与相应的触控电极50连接。

131.在示例性实施方式中,在一个像素行中,第一引线61可以包括第一直线段、第二直

线段以及位于第一直线段和第二直线段之间的弯折段,弯折段的第一端与第一直线段连接,弯折段的第二端与第二直线段连接,弯折段的中部可以向着远离第二引线62的方向凸起,第一连接块61-1可以设置在弯折段靠近第二引线62的一侧,即第一连接块61-1可以设置在弯折段弯折形成的区域内。

132.在示例性实施方式中,在另一个像素行中,第二引线62上可以设置有第二连接块62-1,第二连接块62-1可以通过第二过孔k2与另一个触控电极50连接。

133.在示例性实施方式中,在另一个像素行中,第一引线61可以包括第一直线段、第二直线段以及位于第一直线段和第二直线段之间的弯折段,弯折段的第一端与第一直线段连接,弯折段的第二端与第二直线段连接,弯折段的中部可以向着远离第二引线62的方向凸起,使得第二连接块62-1可以设置在弯折段弯折形成的区域内。

134.在示例性实施方式中,第一连接块61-1在基底上的正投影与栅线20在基底上的正投影至少部分交叠,第二连接块62-1在基底上的正投影与栅线20在基底上的正投影至少部分交叠。

135.在示例性实施方式中,至少一个像素单元中的触控电极50可以包括电极部51和连接部52,电极部51可以设置在像素单元内,连接部52可以设置在相邻的像素单元之间,并与相邻的像素单元内的电极部51连接,将多个像素单元内的多个电极部51连接成一体。

136.在示例性实施方式中,连接部52可以设置在第一方向x相邻的像素单元之间,或者,连接部52可以设置在第二方向y相邻的像素单元之间,或者,连接部52可以设置在第一方向x相邻的像素单元之间以及第二方向y相邻的像素单元之间。

137.在示例性实施方式中,电极部51在基底上的正投影与栅线20在基底上的正投影没有交叠,电极部51在基底上的正投影与第一引线61在基底上的正投影没有交叠,电极部51在基底上的正投影与第二引线62在基底上的正投影没有交叠。

138.在示例性实施方式中,连接部52在基底上的正投影与栅线20在基底上的正投影至少部分交叠,连接部52在基底上的正投影与第一引线61在基底上的正投影至少部分交叠,连接部52在基底上的正投影与第二引线62在基底上的正投影至少部分交叠。

139.在示例性实施方式中,一个触控电极50的至少一个连接部52通过第一过孔k1与第一引线61连接,另一个触控电极50的至少一个连接部52通过第二过孔k2与第二引线62连接。

140.在示例性实施方式中,第一过孔k1在基底上的正投影与栅线20在基底上的正投影至少部分交叠,第二过孔k2在基底上的正投影与栅线20在基底上的正投影至少部分交叠。

141.在示例性实施方式中,像素单元中的电极部51上可以设置有至少一个开口53,开口53的形状可以为沿着第二方向y延伸的折线状,使得电极部51形成沿着第一方向x间隔设置的多个条形电极,可以保证面状的像素电极40和条形的公共电极(触控电极)之间形成水平电场。

142.下面通过阵列基板的制备过程进行示例性说明。本公开所说的“图案化工艺”,对于金属材料、无机材料或透明导电材料,包括涂覆光刻胶、掩模曝光、显影、刻蚀、剥离光刻胶等处理,对于有机材料,包括涂覆有机材料、掩模曝光和显影等处理。沉积可以采用溅射、蒸镀、化学气相沉积中的任意一种或多种,涂覆可以采用喷涂、旋涂和喷墨打印中的任意一种或多种,刻蚀可以采用干刻和湿刻中的任意一种或多种,本公开不做限定。“薄膜”是指将

某一种材料在基底上利用沉积、涂覆或其它工艺制作出的一层薄膜。若在整个制作过程当中该“薄膜”无需图案化工艺,则该“薄膜”还可以称为“层”。若在整个制作过程当中该“薄膜”需图案化工艺,则在图案化工艺前称为“薄膜”,图案化工艺后称为“层”。经过图案化工艺后的“层”中包含至少一个“图案”。本公开所说的“a和b同层设置”是指,a和b通过同一次图案化工艺同时形成,膜层的“厚度”为膜层在垂直于阵列基板方向上的尺寸。本公开示例性实施例中,“b的正投影位于a的正投影的范围之内”或者“a的正投影包含b的正投影”是指,b的正投影的边界落入a的正投影的边界范围内,或者a的正投影的边界与b的正投影的边界重叠。

143.在示例性实施方式中,阵列基板的制备可以包括如下操作。

144.(1)形成第一导电层图案。在示例性实施方式中,形成第一导电层图案可以包括:在基底上沉积第一导电薄膜,通过图案化工艺对第一导电薄膜进行图案化,在基底上形成第一导电层图案,第一导电层图案至少包括栅线20和栅电极21,如图8a和图8b所示,图8a为图6中a区域的放大图,图8b为图6中b区域的放大图。

145.在示例性实施方式中,栅线20的形状可以为主体部分沿着第一方向x延伸的直线状,每个子像素的栅线20可以设置在子像素第二方向y的一侧(子像素中靠近下一行子像素的位置),栅线20被配置为与子像素中的薄膜晶体管连接,向薄膜晶体管提供扫描信号。

146.在示例性实施方式中,栅电极21的形状可以为矩形状,栅电极21可以设置在每个子像素中,且与栅线20连接,相当于栅线20在形成晶体管的区域进行了加宽设计,使得栅线20与后续形成的数据线的交叠区域较小,可以减小栅线20与数据线之间的寄生电容,提高阵列基板的电学性能。

147.在示例性实施方式中,栅线20和多个子像素中的栅电极21可以为相互连接的一体结构。

148.(2)形成半导体层图案。在示例性实施方式中,形成半导体层图案可以包括:在形成有前述图案的基底上依次沉积第一绝缘薄膜和半导体层薄膜,通过图案化工艺对半导体层薄膜进行图案化,形成覆盖第一导电层图案的第一绝缘层,以及设置在第一绝缘层上的半导体层图案,如图9a和图9b所示,图9a为图6中a区域的放大图,图9b为图6中b区域的放大图。

149.在示例性实施方式中,半导体层图案至少包括设置在每个子像素内的有源层22,有源层22在基底上的正投影可以位于栅电极21在基底上的正投影的范围之内。

150.在示例性实施方式中,每个子像素中有源层22的形状和位置可以相同,可以简化薄膜晶体管的结构。

151.(3)形成第二导电层图案。在示例性实施方式中,形成第二导电层图案可以包括:在形成有前述图案的基底上沉积第二导电薄膜,通过图案化工艺对第二导电薄膜进行图案化,形成第二导电层图案,如图10a和图10b所示,图10a为图6中a区域的放大图,图10b为图6中b区域的放大图。

152.在示例性实施方式中,第二导电层图案至少包括:源电极23、漏电极24、数据线30、第一引线61和第二引线62。

153.在示例性实施方式中,数据线30、第一引线61和第二引线62的形状可以为主体部分沿着第二方向y延伸的折线状,数据线30、第一引线61和第二引线62中各个折线的延伸方

向可以基本上相同。

154.在示例性实施方式中,每个子像素中均设置有数据线30,数据线30可以设置在每个子像素第一方向x的反方向的一侧(左侧),数据线30被配置为与子像素中的薄膜晶体管连接,向薄膜晶体管提供数据信号。

155.在示例性实施方式中,源电极23和漏电极24可以设置在每个子像素中,数据线30的一部分作为每个子像素的源电极23,每个子像素的漏电极24可以为单独设置的“l”形状,源电极23与有源层22连接,漏电极24的第一端与有源层22连接,漏电极24的第二端向着远离有源层22的方向延伸,被配置为与后续形成的像素电极连接,源电极23与漏电极24之间形成导电沟道。

156.在示例性实施方式中,每个子像素中的栅电极21、有源层22、源电极23和漏电极24构成薄膜晶体管,栅电极21与栅线连接,源电极23与数据线30连接,漏电极24与像素电极连接。

157.在示例性实施方式中,第一引线61和第二引线62可以设置在第一方向x上相邻的像素单元之间,第一引线61和第二引线62被配置为与后续形成的触控电极(复用为公共电极)连接,向触控电极提供触控信号或者公共电压信号。

158.在示例性实施方式中,第一引线61和第二引线62可以设置在第n-1像素列与第n像素列之间,以及设置在第n像素列与第n+1像素列之间。对于第n像素列,第一引线61可以设置在第三子像素p3远离第一子像素p1的一侧,第二引线62可以设置在第一引线61远离第一子像素p1的一侧。

159.如图10a所示,第m1像素行中,第n像素列与第n+1像素列之间的第一引线61的形状与其它相邻像素列之间的第一引线61的形状不同,而第二引线62的形状与其它相邻像素列之间的第二引线62的形状基本上相同。

160.在示例性实施方式中,第一引线61可以包括第一直线段61a、第二直线段61b以及位于第一直线段61a和第二直线段61b之间的弯折段61c,且第一引线61上设置有第一连接块61-1,第一连接块61-1被配置为通过过孔与后续形成的一个触控电极连接。

161.在示例性实施方式中,弯折段61c的第一端与第一直线段61a连接,弯折段61c的第二端与第二直线段61b连接,弯折段61c的中部可以向着第一方向x的反方向(远离第二引线62的方向)凸起,第一连接块61-1设置在弯折段61c第一方向x(靠近第二引线62的方向)的一侧,即第一连接块61-1设置在弯折段61c弯折形成的区域内。

162.在示例性实施方式中,第一直线段61a、第二直线段61b、弯折段61c和第一连接块61-1可以为相互连接的一体结构。

163.在示例性实施方式中,弯折段61c在基底上的正投影与栅线20在基底上的正投影至少部分交叠,第一连接块61-1在基底上的正投影与栅线20在基底上的正投影至少部分交叠,使得第一引线61与触控电极的连接点位于子像素的非开口区域,以提高子像素的开口率。

164.如图10b所示,第m2像素行中,第n像素列与第n+1像素列之间的第一引线61的形状与其它相邻像素列之间的第一引线61的形状不同,且第二引线62的形状与其它相邻像素列之间的第二引线62的形状不同。

165.在示例性实施方式中,第二引线62可以设置有第二连接块62-1,第二连接块62-1

被配置为通过过孔与后续形成的另一个触控电极连接。第二连接块62-1可以设置在第二引线62第一方向x的反方向的一侧(朝向第一引线61的方向),第二连接块62-1的形状可以为向着第一引线61方向凸起的梯形。

166.在示例性实施方式中,第一引线61可以包括第一直线段61a、第二直线段61b以及位于第一直线段61a和第二直线段61b之间的弯折段61c。弯折段61c的第一端与第一直线段61a连接,弯折段61c的第二端与第二直线段61b连接,弯折段61c的中部可以向着第一方向x的反方向凸起,使得第二连接块62-1可以设置在弯折段61c弯折形成的区域内。

167.在示例性实施方式中,第二连接块62-1在基底上的正投影与栅线20在基底上的正投影至少部分交叠,使得第二引线61与触控电极的连接点位于子像素的非开口区域,以提高子像素的开口率。

168.在示例性实施方式中,第一直线段61a、第二直线段61b和弯折段61c可以为相互连接的一体结构。

169.在示例性实施方式中,第二引线62和第二连接块62-1可以为相互连接的一体结构。

170.在示例性实施方式中,位于第n像素列与第n+1像素列之间的第一引线61中,第m1像素行和第m2像素行中的第一直线段61a、第二直线段61b和弯折段61c的形状可以基本上相同。

171.(4)形成第二绝缘层图案。在示例性实施方式中,形成第二绝缘层图案可以包括:在形成有前述图案的基底上,沉积第二绝缘薄膜,通过图案化工艺对第二绝缘薄膜进行图案化,形成覆盖第二导电图案的第二绝缘层图案,第二绝缘层上形成有多个过孔,如图11a和图11b所示,图11a为图6中a区域的放大图,图11b为图6中b区域的放大图。

172.在示例性实施方式中,多个过孔可以至少包括设置在每个子像素的连接过孔k。连接过孔k在基底上的正投影可以位于漏电极24在基底上的正投影的范围之内,连接过孔k内的第二绝缘层被刻蚀掉,暴露出漏电极24的表面,连接过孔k被配置为使后续形成的像素电极通过该过孔与漏电极24连接。

173.在示例性实施方式中,连接过孔k的形状可以为如下任意一种或多种:正方形、矩形、圆形和椭圆形。

174.(5)形成第三导电层图案。在示例性实施方式中,形成第三导电层图案可以包括:在形成有前述图案的基底上沉积第三导电薄膜,通过图案化工艺对第三导电薄膜进行图案化,在第二绝缘层上形成第三导电层图案,如图12a和图12b所示,图12a为图6中a区域的放大图,图12b为图6中b区域的放大图。

175.在示例性实施方式中,第三导电层图案可以至少包括设置在每个子像素中的像素电极40。

176.在示例性实施方式中,每个子像素中的像素电极40的形状可以为整面状,位于栅线20和数据线30围成的区域内,且像素电极40在基底上的正投影与漏电极24在基底上的正投影至少部分交叠,像素电极40通过连接过孔k与薄膜晶体管的漏电极24连接。

177.(6)形成第三绝缘层图案。在示例性实施方式中,形成第三绝缘层图案可以包括:在形成有前述图案的基底上,沉积第三绝缘薄膜,通过图案化工艺对第三绝缘薄膜进行图案化,形成覆盖第三导电图案的第三绝缘层图案,第三绝缘层上形成有多个过孔,如图13a

和图13b所示,图13a为图6中a区域的放大图,图13b为图6中b区域的放大图。

178.在示例性实施方式中,多个过孔可以至少包括设置在第m1像素行、第n像素列中的第一过孔k1和设置在第m2像素行、第n像素列中的第二过孔k2。

179.在示例性实施方式中,第一过孔k1在基底上的正投影可以位于第一引线61的第一连接块61-1在基底上的正投影的范围之内,第一过孔k1内的第二绝缘层和第三绝缘层被刻蚀掉,暴露出第一连接块61-1的表面,第一过孔k1被配置为使后续形成的一个触控电极通过该过孔与第一连接块61-1连接。

180.在示例性实施方式中,第一过孔k1在基底上的正投影与栅线20在基底上的正投影至少部分交叠,使得第一引线61与触控电极的连接点位于子像素的非开口区域,以提高子像素的开口率。

181.在示例性实施方式中,第二过孔k2在基底上的正投影可以位于第二引线62的第二连接块62-1在基底上的正投影的范围之内,第二过孔k2内的第二绝缘层和第三绝缘层被刻蚀掉,暴露出第二连接块62-1的表面,第二过孔k2被配置为使后续形成的另一个触控电极通过该过孔与第二连接块62-1连接。

182.在示例性实施方式中,第二过孔k2在基底上的正投影与栅线20在基底上的正投影至少部分交叠,使得第二引线62与触控电极的连接点位于子像素的非开口区域,以提高子像素的开口率。

183.在示例性实施方式中,第一过孔k1和第二过孔k2的形状可以为如下任意一种或多种:正方形、矩形、圆形和椭圆形。

184.(7)形成第四导电层图案。在示例性实施方式中,形成第四导电层图案可以包括:在形成有前述图案的基底上沉积第四导电薄膜,通过图案化工艺对第四导电薄膜进行图案化,在第三绝缘层上形成第四导电层图案,如图7a和图7b所示。

185.在示例性实施方式中,第四导电层图案至少包括规则排布的多个触控电极50,多个触控电极50复用为公共电极。

186.在示例性实施方式中,覆盖第m1像素行、第n像素列的触控电极50通过第一过孔k1与第一连接块61-1连接。由于第一连接块61-1与第一引线61连接,因而实现了第一引线61与一个触控电极50的连接,第一引线61可以向该触控电极50提供触控信号或者公共电压信号。

187.在示例性实施方式中,覆盖第m2像素行、第n像素列的触控电极50通过第二过孔k2与第二连接块62-1连接。由于第二连接块62-1与第二引线62连接,因而实现了第二引线62与另一个触控电极50的连接,第二引线62可以向该触控电极50提供触控信号或者公共电压信号。

188.在示例性实施方式中,至少一个像素单元中,触控电极50可以包括电极部51和连接部52,电极部51可以设置在像素单元内,即电极部51可以设置在由第一引线61、第二引线62和两条栅线20围成的区域内。连接部52可以设置在相邻的像素单元之间,并与相邻的像素单元内的电极部51连接,将多个像素单元内的多个电极部51连接成一体构成块状的触控电极50。

189.在示例性实施方式中,连接部52可以设置在第一方向x相邻的像素单元之间,将一个像素行中的多个电极部51连接成一体,或者,连接部52可以设置在第二方向y相邻的像素

单元之间,将一个像素列中的多个电极部51连接成一体,或者,连接部52可以设置在第一方向x相邻的像素单元之间以及第二方向y相邻的像素单元之间,将多个像素行和多个像素列中的多个电极部51连接成一体。

190.在示例性实施方式中,电极部51在基底上的正投影与栅线20在基底上的正投影没有交叠,电极部51在基底上的正投影与第一引线61在基底上的正投影没有交叠,电极部51在基底上的正投影与第二引线62在基底上的正投影没有交叠,以减少栅线20、第一引线61和第二引线62传输的信号对触控电极(公共电极)的影响。

191.在示例性实施方式中,连接部52在基底上的正投影与栅线20在基底上的正投影至少部分交叠,连接部52在基底上的正投影与第一引线61在基底上的正投影至少部分交叠,连接部52在基底上的正投影与第二引线62在基底上的正投影至少部分交叠。

192.在示例性实施方式中,一个触控电极50的至少一个连接部52可以通过第一过孔k1与第一连接块61-1连接,另一个触控电极50的至少一个连接部52可以通过第二过孔k2与第二连接块62-1连接,使得第一引线61和第二引线62与触控电极的连接点均位于子像素的非开口区域,以提高子像素的开口率。

193.在示例性实施方式中,像素单元中的电极部51上可以设置有至少一个开口53,开口53内的第四导电薄膜被刻蚀掉,暴露出第三绝缘层。开口53的形状可以为沿着第二方向y延伸的折线状,使得电极部51形成沿着第一方向x间隔设置的多个条形电极,可以保证面状的像素电极40和条形的公共电极(触控电极)之间形成水平电场。

194.在示例性实施方式中,基底可以采用玻璃或石英等。第一导电层和第二导电层可以采用金属材料,如银(ag)、铜(cu)、铝(al)和钼(mo)中的任意一种或多种,或上述金属的合金材料,如铝钕合金(alnd)或钼铌合金(monb),可以是单层结构,或者多层复合结构,如mo/cu/mo等,第一导电层可以称为栅金属(gate)层,第二导电层可以称为源漏金属(sd)层。第三导电层和第四导电层可以采用透明导电材料,如氧化铟锡ito或氧化铟锌izo等。第一绝缘层、第二绝缘层和第三绝缘层可以采用硅氧化物(siox)、硅氮化物(sinx)和氮氧化硅(sion)中的任意一种或多种,可以是单层、多层或复合层。第一绝缘层可以称为栅绝缘(gi)层,第二绝缘层可以称为层间绝缘层(ild),第三绝缘层可以称为钝化(pvx)层。有源层可以采用非晶态氧化铟镓锌材料(a-igzo)、氮氧化锌(znon)、氧化铟锌锡(izto)、非晶硅(a-si)、多晶硅(p-si)、六噻吩或聚噻吩等材料,即本公开适用于基于氧化物(oxide)技术、硅技术或有机物技术制造的晶体管。

195.至此,完成本公开示例性实施例阵列基板的制备。在垂直于阵列基板的平面上,阵列基板可以包括设置在基底上的第一导电层、设置在第一导电层远离基底一侧的第一绝缘层、设置在第一绝缘层远离基底一侧的半导体层、设置在半导体层远离基底一侧的第二导电层、设置在第二导电层远离基底一侧的第二绝缘层、设置在第二绝缘层远离基底一侧的第三导电层、设置在第三导电层远离基底一侧的第四绝缘层、设置在第四绝缘层远离基底一侧的第四导电层。在平行于阵列基板的平面上,阵列基板可以包括多个子像素,每个子像素可以包括薄膜晶体管、像素电极和复用为公共电极的触控电极,薄膜晶体管可以包括栅电极、有源层、第一极和第二极,栅电极与栅线连接,第一极与数据线连接,第二极与像素电极连接,触控电极与第一引线或者第二引线连接,像素电极和公共电极之间形成水平电场。

196.通过本公开示例性实施例阵列基板的结构和制备过程可以看出,本公开通过在相

邻的像素单元之间设置触控引线组,触控引线组可以包括并列设置的第一引线和第二引线,不仅减小了引线数量,增加了子像素的空间,提高了像素开口率,有利于显示装置分辨率的提高,而且由于每条引线均与相应的触控电极通过过孔连接,保证了像素结构的一致性和刻蚀均一性,有利于提高制备工艺的质量。

197.图14为本公开示例性实施例一种绑定区域和边框区域的平面结构示意图。如图14所示,阵列基板可以包括显示区域100、位于显示区域100一侧的绑定区域200、位于显示区域100远离绑定区域200一侧的上边框区310以及位于显示区域100两侧的侧边框区320。

198.在示例性实施方式中,显示区域100可以至少包括构成触控阵列的多个触控电极50和构成像素阵列的多个像素单元60,至少一个像素单元60可以包括三个子像素,至少一个子像素可以包括薄膜晶体管10、栅线20、数据线30和像素电极40,薄膜晶体管10分别与栅线20、数据线30和像素电极40连接,触控电极50可以复用为公共电极。

199.在示例性实施方式中,显示区域100还可以包括多个触控引线组,多个触控引线组分别设置在相邻的像素列之间,至少一个触控引线组可以至少包括并列设置的第一引线61和第二引线62,第一引线61和第二引线62复用为公共电极线,第一引线61可以与奇数的触控行中的触控电极50连接,第二引线62可以与偶数的触控行中的触控电极50连接。

200.在示例性实施方式中,绑定区域200可以至少包括驱动芯片280和多个引脚。驱动芯片280可以通过多条连接线分别与显示区域中的多条数据线和多条触控引线(第一引线和第二引线)对应连接。在正常显示时,驱动芯片280被配置为向多条数据线和多条触控引线分别提供数据信号和触控信号。

201.在示例性实施方式中,绑定区域200的多个引脚可以至少包括如下任意一种或多种:第一测试引脚210、第二测试引脚220、第一数据引脚230、第二数据引脚240、第三数据引脚250、开关控制引脚260和栅线控制引脚270。在进行测试时,多个引脚被配置为与外部测试装置绑定连接,使外部测试装置向相应的信号线输出相应的信号。

202.在示例性实施方式中,第一测试引脚210、第一数据引脚230、开关控制引脚260和栅线控制引脚270可以设置在绑定区域200第一方向x的反方向的一侧,第二测试引脚220、第二数据引脚240、第三数据引脚250和栅线控制引脚270可以设置在绑定区域200的第一方向x的一侧。

203.在示例性实施方式中,第一测试引脚210、第一数据引脚230、开关控制引脚260和栅线控制引脚270可以沿着第一方向x依次设置,栅线控制引脚270、第二数据引脚240、第三数据引脚250和第二测试引脚220可以沿着第一方向x依次设置。

204.在示例性实施方式中,上边框区310可以至少包括测试电路。本公开阵列基板将触控引线组设置在相邻的像素单元之间,触控引线组中的多条引线相邻,当工艺制程或者灰尘(particle)等原因导致相邻引线短路时,或导致触控功能异常。为了在模组之前将此类不良筛选出来,本公开在上边框区310设置了测试电路,测试电路被配置为对阵列基板的短路不良进行检测。

205.在示例性实施方式中,测试电路可以包括多个测试单元70,多个测试单元70可以沿着第一方向x依次设置,且多个测试单元70与显示区域100中多个触控列的位置一一对应。

206.在示例性实施方式中,至少一个测试单元可以至少包括第一测试线71、第二测试

线72、第一数据引线73、第二数据引线74、第三数据引线75、开关控制线76、第一开关91、第二开关92、第三开关93、第四开关94和第五开关95。

207.在示例性实施方式中,开关控制线76、第一数据引线73、第二数据引线74、第三数据引线75、第二测试线72和第一测试线71可以沿着远离显示区域的方向依次设置,且上述信号线均为沿着第一方向x延伸的线形状。

208.在示例性实施方式中,第三开关93、第四开关94、第五开关95、第一开关91和第二开关92可以沿着第一方向x依次设置。

209.在示例性实施方式中,第一开关91的第一极与第一测试线71连接,第一开关91的第二极与显示区域100中的第一引线61连接,第一开关91的控制极与开关控制线76连接,即第一测试线71通过第一开关91与显示区域100中的第一引线61连接,第一测试线71被配置为在开关控制线76和第一开关91的控制下向第一引线61传输第一测试信号。

210.在示例性实施方式中,第二开关92的第一极与第二测试线72连接,第二开关92的第二极与显示区域100中的第二引线62连接,第二开关92的控制极与开关控制线76连接,即第二测试线72通过第二开关92与显示区域100中的第二引线62连接,第二测试线72被配置为在开关控制线76和第二开关92的控制下向第二引线62传输第二测试信号。

211.在示例性实施方式中,第一测试信号的电压值大于第二测试信号的电压值,或者,第一测试信号的电压值小于第二测试信号的电压值,即第一测试信号的电压值与第二测试信号的电压值不相等。

212.在示例性实施方式中,第三开关93的第一极与第一数据引线73连接,第三开关93的第二极与显示区域100中第一子像素的数据线30连接,第三开关93的控制极与开关控制线76连接,即第一数据引线73通过第三开关93与显示区域100中的第一子像素的数据线30连接,第一数据引线73被配置为在开关控制线76和第三开关93的控制下向第一子像素的数据线30传输第一数据信号。

213.在示例性实施方式中,第四开关94的第一极与第二数据引线74连接,第四开关94的第二极与显示区域100中第二子像素的数据线30连接,第四开关94的控制极与开关控制线76连接,即第二数据引线74通过第四开关94与显示区域100中的第二子像素的数据线30连接,第二数据引线74被配置为在开关控制线76和第四开关94的控制下向第二子像素的数据线30传输第二数据信号。

214.在示例性实施方式中,第五开关95的第一极与第三数据引线75连接,第五开关95的第二极与显示区域100中第三子像素的数据线30连接,第五开关95的控制极与开关控制线76连接,即第三数据引线75通过第五开关95与显示区域100中的第三子像素的数据线30连接,第三数据引线75被配置为在开关控制线76和第五开关95的控制下向第三子像素的数据线30传输第三数据信号。

215.在示例性实施方式中,第一开关91、第二开关92、第三开关93、第四开关94和第五开关95可以为薄膜晶体管。

216.在示例性实施方式中,侧边框区320可以至少包括栅极驱动电路330和多条连接线,栅极驱动电路330可以设置在多条连接线靠近显示区域的一侧。

217.在示例性实施方式中,侧边框区320可以包括左侧边框和右侧边框。左侧边框可以至少包括栅极驱动电路330、第一连接线81、第三连接线83和第六连接线86,右侧边框可以

至少包括栅极驱动电路330、第二连接线82、第四连接线84和第五连接线85。

218.在示例性实施方式中,设置在左侧边框和右侧边框内的栅极驱动电路330的测试端分别通过连接线与绑定区域200中的栅线控制引脚270连接,栅极驱动电路330的输出端分别与显示区域100中的多条栅线20连接。在进行测试时,栅极驱动电路330的测试端与输出端连通,栅极驱动电路330被配置为向显示区域100中的多条栅线20输出开启电压。

219.在示例性实施方式中,第一连接线81的第一端与绑定区域200中的第一测试引脚210连接,第一连接线81的第二端向着上边框区310延伸后,与上边框区310中的第一测试线71连接,实现了第一测试线71与第一测试引脚210的连接。

220.在示例性实施方式中,第二连接线82的第一端与绑定区域200中的第二测试引脚220连接,第二连接线82的第二端向着上边框区310延伸后,与上边框区310中的第二测试线72连接,实现了第二测试线72与第二测试引脚220的连接。

221.在示例性实施方式中,第三连接线83的第一端与绑定区域200中的第一数据引脚230连接,第三连接线83的第二端向着上边框区310延伸后,与上边框区310中的第一数据引线73连接,实现了第一数据引线73与第一数据引脚230的连接。

222.在示例性实施方式中,第四连接线84的第一端与绑定区域200中的第二数据引脚240连接,第四连接线84的第二端向着上边框区310延伸后,与上边框区310中的第二数据引线74连接,实现了第二数据引线74与第二数据引脚240的连接。

223.在示例性实施方式中,第五连接线85的第一端与绑定区域200中的第三数据引脚250连接,第五连接线85的第二端向着上边框区310延伸后,与上边框区310中的第三数据引线75连接,实现了第三数据引线75与第三数据引脚250的连接。

224.在示例性实施方式中,第六连接线86的第一端与绑定区域200中的开关控制引脚260连接,第六连接线86的第二端向着上边框区310延伸后,与上边框区310中的开关控制线76连接,实现了开关控制线76与开关控制引脚260的连接。

225.在示例性实施方式中,本公开测试电路的制备可以包括如下操作。

226.(11)在显示区域形成第一导电层图案时,第一导电层图案还包括位于上边框区的第一测试线71、第二测试线72、第一数据引线73、第二数据引线74、第三数据引线75和控制线组,如图15所示。

227.在示例性实施方式中,控制线组、第一数据引线73、第二数据引线74、第三数据引线75、第二测试线72和第一测试线71可以沿着远离显示区域的方向依次设置。

228.在示例性实施方式中,控制线组可以至少包括沿着远离显示区域的方向依次设置的第一控制线76-1、第二控制线76-2、第三控制线76-3、第四控制线76-4和第五控制线76-5。

229.在示例性实施方式中,第三控制线76-3和第五控制线76-5之间可以设置有多个第一栅极块111和多个第二栅极块112,多个第一栅极块111和多个第二栅极块112的第一端与第三控制线76-3连接,多个第一栅极块111和多个第二栅极块112的第二端与第五控制线76-5,多个第一栅极块111和多个第二栅极块112的中部与第四控制线76-4连接,使得第三控制线76-3、第四控制线76-4和第五控制线76-5通过多个第一栅极块111和多个第二栅极块112连接成一体结构,多个第一栅极块111被配置为作为第一开关91的栅电极,多个第二栅极块112被配置为作为第二开关92的栅电极。

230.在示例性实施方式中,第四控制线76-4和第五控制线76-5之间可以设置有多个第四栅极块114,多个第四栅极块114的第一端与第四控制线76-4连接,多个第四栅极块114的第二端与第五控制线76-5,多个第四栅极块114被配置为作为第四开关94的栅电极。

231.在示例性实施方式中,第一控制线76-1和第二控制线76-2之间可以设置有多个第三栅极块113和多个第五栅极块115,多个第三栅极块113和多个第五栅极块115的第一端与第一控制线76-1连接,多个第三栅极块113和多个第五栅极块115的第二端与第二控制线76-2连接,使得第一控制线76-1和第二控制线76-2通过多个第三栅极块113和多个第五栅极块115连接成一体结构,多个第三栅极块113被配置为作为第三开关93的栅电极,多个第五栅极块115被配置为作为第五开关95的栅电极。

232.本公开通过采用多条控制线和多个栅极块组成控制线组,可以有效减小开关的占用面积,减小边框宽度,有利于实现窄边框。

233.(12)在显示区域形成半导体层图案时,半导体层图案还包括位于上边框区的第一有源层121、第二有源层122、第三有源层123、第四有源层124和第五有源层125,如图16所示。

234.在示例性实施方式中,第一有源层121在基底上的正投影可以位于第一栅极块111在基底上的正投影的范围之内,第一有源层121被配置为作为第一开关91的有源层。

235.在示例性实施方式中,第二有源层122在基底上的正投影可以位于第二栅极块112在基底上的正投影的范围之内,第二有源层122被配置为作为第二开关92的有源层。

236.在示例性实施方式中,第三有源层123在基底上的正投影可以位于第三栅极块113在基底上的正投影的范围之内,第三有源层123被配置为作为第三开关93的有源层。

237.在示例性实施方式中,第四有源层124在基底上的正投影可以位于第四栅极块114在基底上的正投影的范围之内,第四有源层124被配置为作为第四开关94的有源层。

238.在示例性实施方式中,第五有源层125在基底上的正投影可以位于第五栅极块115在基底上的正投影的范围之内,第五有源层125被配置为作为第五开关95的有源层。

239.(13)在显示区域形成第二导电层图案时,第二导电层图案还包括位于上边框区的第一源电极131、第二源电极132、第三源电极133、第四源电极134、第五源电极135、第一漏电极141、第二漏电极142、第三漏电极143、第四漏电极144、第五漏电极145、第一搭接块151、第二搭接块152、第三搭接块153、第四搭接块154和第五搭接块155,如图17所示。

240.在示例性实施方式中,第一源电极131的第一端与第一有源层121连接,第一源电极131的第二端向着远离显示区域的方向延伸后,与第一搭接块151连接,第一搭接块151可以设置在第一测试线71靠近显示区域的一侧,第一搭接块151被配置为与后续形成第一搭接电极连接。第一漏电极141的第一端与第一有源层121连接,第一漏电极141的第二端向着显示区域的方向延伸后,与显示区域的第一引线连接。第一源电极131和第一漏电极141之间形成导电沟道,第一栅极块111、第一有源层121、第一源电极131和第一漏电极141构成第一开关91。

241.在示例性实施方式中,第二源电极132的第一端与第二有源层122连接,第二源电极132的第二端向着远离显示区域的方向延伸后,与第二搭接块152连接,第二搭接块152可以设置在第二测试线72靠近显示区域的一侧,第二搭接块152被配置为与后续形成第二搭接电极连接。第二漏电极142的第一端与第二有源层122连接,第二漏电极142的第二端向着

显示区域的方向延伸后,与显示区域的第二引线连接。第二源电极132和第二漏电极142之间形成导电沟道,第二栅极块112、第二有源层122、第二源电极132和第二漏电极142构成第二开关92。

242.在示例性实施方式中,第三源电极133的第一端与第三有源层123连接,第三源电极133的第二端向着远离显示区域的方向延伸后,与第三搭接块153连接,第三搭接块153可以设置在第一数据引线73靠近显示区域的一侧,第三搭接块153被配置为与后续形成第三搭接电极连接。第三漏电极143的第一端与第三有源层123连接,第三漏电极143的第二端向着显示区域的方向延伸后,与显示区域中第一子像素的数据线连接。第三源电极133和第三漏电极143之间形成导电沟道,第三栅极块113、第三有源层123、第三源电极133和第三漏电极143构成第三开关93。

243.在示例性实施方式中,第四源电极134的第一端与第四有源层124连接,第四源电极134的第二端向着远离显示区域的方向延伸后,与第四搭接块154连接,第四搭接块154可以设置在第二数据引线74靠近显示区域的一侧,第四搭接块154被配置为与后续形成第四搭接电极连接。第四漏电极144的第一端与第四有源层124连接,第四漏电极144的第二端向着显示区域的方向延伸后,与显示区域中第二子像素的数据线连接。第四源电极134和第四漏电极144之间形成导电沟道,第四栅极块114、第四有源层124、第四源电极134和第四漏电极144构成第四开关94。

244.在示例性实施方式中,第五源电极135的第一端与第五有源层125连接,第五源电极135的第二端向着远离显示区域的方向延伸后,与第五搭接块155连接,第五搭接块155可以设置在第三数据引线75靠近显示区域的一侧,第五搭接块155被配置为与后续形成第五搭接电极连接。第五漏电极145的第一端与第五有源层125连接,第五漏电极145的第二端向着显示区域的方向延伸后,与显示区域中第三子像素的数据线连接。第五源电极135和第五漏电极145之间形成导电沟道,第五栅极块115、第五有源层125、第五源电极135和第五漏电极145构成第五开关95。

245.(14)在显示区域形成第二绝缘层图案时,第二绝缘层上的多个过孔还包括位于上边框区的第十一过孔v11、第十二过孔v12、第十三过孔v13、第十四过孔v14、第十五过孔v15、第十六过孔v16、第十七过孔v17、第十八过孔v18、第十九过孔v19、第二十过孔v20,如图18所示。

246.在示例性实施方式中,第十一过孔v11在基底上的正投影可以位于第一搭接块151在基底上的正投影的范围之内,第十一过孔v11暴露出第一搭接块151的表面,第十一过孔v11被配置为使后续形成的第一搭接电极通过该过孔与第一搭接块151连接。

247.在示例性实施方式中,第十二过孔v12在基底上的正投影可以位于第二搭接块152在基底上的正投影的范围之内,第十二过孔v12暴露出第二搭接块152的表面,第十二过孔v12被配置为使后续形成的第二搭接电极通过该过孔与第二搭接块152连接。

248.在示例性实施方式中,第十三过孔v13在基底上的正投影可以位于第三搭接块153在基底上的正投影的范围之内,第十三过孔v13暴露出第三搭接块153的表面,第十三过孔v13被配置为使后续形成的第三搭接电极通过该过孔与第三搭接块153连接。

249.在示例性实施方式中,第十四过孔v14在基底上的正投影可以位于第四搭接块154在基底上的正投影的范围之内,第十四过孔v14暴露出第四搭接块154的表面,第十四过孔

v14被配置为使后续形成的第四搭接电极通过该过孔与第四搭接块154连接。

250.在示例性实施方式中,第十五过孔v15在基底上的正投影可以位于第五搭接块155在基底上的正投影的范围之内,第十五过孔v15暴露出第五搭接块155的表面,第十五过孔v15被配置为使后续形成的第五搭接电极通过该过孔与第五搭接块155连接。

251.在示例性实施方式中,第十六过孔v16在基底上的正投影可以位于第一测试线71在基底上的正投影的范围之内,第十六过孔v16暴露出第一测试线71的表面,第十六过孔v16被配置为使后续形成的第一搭接电极通过该过孔与第一测试线71连接。

252.在示例性实施方式中,第十七过孔v17在基底上的正投影可以位于第二测试线72在基底上的正投影的范围之内,第十七过孔v17暴露出第二测试线72的表面,第十七过孔v17被配置为使后续形成的第二搭接电极通过该过孔与第二测试线72连接。

253.在示例性实施方式中,第十八过孔v18在基底上的正投影可以位于第一数据引线73在基底上的正投影的范围之内,第十八过孔v18暴露出第一数据引线73的表面,第十八过孔v18被配置为使后续形成的第三搭接电极通过该过孔与第一数据引线73连接。

254.在示例性实施方式中,第十九过孔v19在基底上的正投影可以位于第二数据引线74在基底上的正投影的范围之内,第十九过孔v19暴露出第二数据引线74的表面,第十九过孔v19被配置为使后续形成的第四搭接电极通过该过孔与第二数据引线74连接。

255.在示例性实施方式中,第二十过孔v20在基底上的正投影可以位于第三数据引线75在基底上的正投影的范围之内,第二十过孔v20暴露出第三数据引线75的表面,第二十过孔v20被配置为使后续形成的第五搭接电极通过该过孔与第三数据引线75连接。

256.第十一过孔v11至第二十过孔v20可以为沿着第一方向x依次设置的多个过孔,以提高连接可靠性。

257.(15)在显示区域形成第三导电层图案时,第三导电层图案还包括位于上边框区的第一搭接电极161、第二搭接电极162、第三搭接电极163、第四搭接电极164和第五搭接电极165,如图19所示。

258.在示例性实施方式中,第一搭接电极161的第一端通过第十一过孔v11与第一搭接块151连接,第一搭接电极161的第二端通过第十六过孔v16与第一测试线71连接。

259.在示例性实施方式中,第二搭接电极162的第一端通过第十二过孔v12与第二搭接块152连接,第二搭接电极162的第二端通过第十七过孔v17与第二测试线72连接。

260.在示例性实施方式中,第三搭接电极163的第一端通过第十三过孔v13与第三搭接块153连接,第三搭接电极163的第二端通过第十八过孔v18与第一数据引线73连接。

261.在示例性实施方式中,第四搭接电极164的第一端通过第十四过孔v14与第四搭接块154连接,第四搭接电极164的第二端通过第十九过孔v19与第二数据引线74连接。

262.在示例性实施方式中,第五搭接电极165的第一端通过第十五过孔v15与第五搭接块155连接,第五搭接电极165的第二端通过第二十过孔v20与第三数据引线75连接。

263.第一搭接电极161至第五搭接电极165可以为沿着第一方向x依次设置的多个搭接电极,以提高连接可靠性。

264.至此,完成本公开示例性实施例测试电路的制备,测试电路可以包括多个测试单元,多个测试单元可以沿着第一方向x依次设置,至少一个测试单元可以至少包括第一测试线71、第二测试线72、第一数据引线73、第二数据引线74、第三数据引线75、开关控制线76、

第一开关91、第二开关92、第三开关93、第四开关94和第五开关95。

265.在示例性实施方式中,测试电路对显示区域中多个触控电极进行检测的过程可以包括:

266.(1)将外部测试装置与绑定区域的多个引脚绑定连接后,外部测试装置分别向栅线控制引脚270提供开启信号,向开关控制引脚260提供导通信号,向第一数据引脚230、第二数据引脚240和第三数据引脚250提供数据信号。在示例性实施方式中,导通信号和开启信号可以是高电平电压(vgh),数据信号可以是公共基准电压(vcom)。外部测试装置提供的开启信号使栅极驱动电路330向显示区域中的多条栅线20输出开启电压,显示区域中多个子像素的薄膜晶体管导通。外部测试装置提供的导通信号使上边框区多个测试单元70的第一开关91、第二开关92、第三开关93、第四开关94和第五开关95导通,外部测试装置提供的数据信号分别通过第一数据引线73和导通的第三开关93、第二数据引线74和导通的第四开关94、第三数据引线75和导通的第五开关95分别提供给显示区域的多条数据线30,并通过导通的薄膜晶体管传输到多个子像素的像素电极40,使显示区域中多个子像素的像素电极40充上公共基准电压。本阶段是通过信号提前打开,在第一测试信号和第二测试信号到来之前将像素电极充上公共基准电压。

267.(2)外部测试装置向第一测试引脚210提供第一测试信号,向第二测试引脚220提供第二测试信号。在示例性实施方式中,第一测试信号可以是第一灰阶电压,第二测试信号可以是第二灰阶电压,第一灰阶电压的电压值可以大于第二灰阶电压的电压值,或者,第一灰阶电压的电压值可以小于第二灰阶电压的电压值。外部测试装置提供的第一测试信号通过第一测试线71和导通的第一开关91提供给显示区域的第一引线61,并传输到与第一引线61连接的多个触控电极50上,使得与这些触控电极50相对应的多个子像素显示第一灰阶。外部测试装置提供的第二测试信号通过第二测试线72和导通的第二开关92提供给显示区域的第二引线62,并传输到与第二引线62连接的多个触控电极50上,使得与这些触控电极50相对应的多个子像素显示第二灰阶。

268.在示例性实施方式中,由于显示区域中所有子像素的像素电极40具有公共基准电压,复用为公共电极的触控电极50分别具有第一灰阶电压和第二灰阶电压,因而显示区域中所有子像素分别显示第一灰阶和第二灰阶。

269.图20和图21为本公开检测电路进行短路检测的示意图,图20为无短路不良时的正常检测画面,图21为有短路不良时的异常检测画面。在示例性实施方式中,第一引线与奇数触控行的触控电极50连接,第二引线与偶数触控行的触控电极50连接。

270.在示例性实施方式中,当阵列基板上无短路不良时,奇数触控行的触控电极50显示第一灰阶,偶数触控行的触控电极50显示第二灰阶,显示区域实现纵向亮暗相间均匀的显示画面,如图20所示。

271.在示例性实施方式中,当阵列基板上有短路不良时,如相邻的第一引线和第二引线出现短路点q,由于此时短路的第一引线和第二引线的电压相同,因而一个奇数行的一个触控电极50与相邻的偶数行的一个触控电极50电压相同,因而相邻的两个触控电极50所在区域显示相同的灰阶,与正常显示画面存在差异,从而可以筛选出不良基板,如图21所示。

272.图22为本公开检测电路进行短路检测时的检测时序示意图。如图22所示,在示例性实施方式中,为了防止液晶同一方向偏转极化导致画面残像,提供给第一测试线和第二

测试线的第一灰阶电压和第二灰阶电压在帧与帧之间进行正负极性翻转。例如,在第m帧,给第一测试线提供第一灰阶电压+lo,给第二测试线提供第二灰阶电压+le。在第m+1帧,给第一测试线提供第一灰阶电压-lo,给第二测试线提供第二灰阶电压-le。

273.通过本公开示例性实施例测试电路的结构、制备过程和测试过程可以看出,本公开在相邻的像素单元之间设置2条触控引线,一条触控引线连接奇数触控行的触控电极,另一条触控引线连接偶数触控行的触控电极,通过向2条触控引线分别提供不同的灰阶电压,在阵列基板无短路不良时,多个触控行呈现纵向亮暗相间的显示画面,在阵列基板有短路不良时,纵向相邻的触控电极会显示相同的灰阶,从而可以筛选出阵列基板短路不良。本公开测试电路的结构简单,检测方法简洁,可以有效筛选出不良基板,减少了模组资材损耗,降低了生产成本,提高了良品率。

274.本公开示例性实施例还提供一种显示装置,显示装置可以包括相对设置的第一基板和第二基板,液晶层设置在第一基板和第二基板之间,第一基板可以采用前述的阵列基板,第二基板可以包括黑矩阵和滤光单元。

275.在示例性实施方式中,本公开显示装置可以为:手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件,本发明实施例并不以此为限。

276.本公开示例性实施例还提供一种采用如上所述阵列基板的检测方法,包括:

277.向显示区域中的多条栅线提供开启电压,使得显示区域中多个子像素的薄膜晶体管导通;向所述显示区域中的多条数据线提供公共基准电压,使得所述显示区域中多个子像素的像素电极具有公共基准电压;

278.向所述显示区域中的第一引线提供第一灰阶电压,使得显示区域中与所述第一引线连接的多个触控电极具有第一灰阶电压;向所述显示区域中的第二引线提供第二灰阶电压,使得显示区域中与所述第二引线连接的多个触控电极具有第二灰阶电压;所述第一灰阶电压的电压值大于所述第二灰阶电压的电压值,或者,所述第一灰阶电压的电压值小于所述第二灰阶电压的电压值。

279.在示例性实施方式中,当所述阵列基板上无短路不良时,一个触控行中的触控电极显示第一灰阶,相邻触控行中的触控电极显示第二灰阶,显示区域呈现纵向亮暗相间的显示画面;当所述阵列基板上有短路不良时,一个触控行中的至少一个触控电极与相邻触控行中的至少一个触控电极显示相同的灰阶。

280.虽然本公开所揭露的实施方式如上,但所述的内容仅为便于理解本公开而采用的实施方式,并非用以限定本发明。任何所属领域内的技术人员,在不脱离本公开所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本发明的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1