具有超薄存储元的存储器

1.本技术涉及集成电路领域,具体而言,涉及一种具有超薄存储元的存储器。

背景技术:

2.交叉阵列(cross point)存储器的存储元面积小(4f2),可实现三维堆叠。如图1所示,存储元00含有第一地址线01、第二地址线02、以及介于它们之间的存储膜06(存储膜06包括所有介于第一地址线01和第二地址线02的薄膜)。存储膜06一般含有选通(selector)膜03和编程(programmable)膜04。其中,选通膜03用于避免的相邻存储元之间的干扰,它具有两个易失的状态(低阻态和高阻态,分别代表“on”和“off”);编程膜04用于存储信息态,它具有至少两个非易失的状态(低阻态和高阻态,分别代表“1”和“0”)。这里,“易失”是指在掉电后,低阻态不再保持、而回到高阻态(当然,在掉电后,高阻态仍是高阻态);“非易失”是指在掉电后,低阻态和高阻态仍继续保持。在存储元00中,地址线01、02的宽度(尺寸)为f。f也为存储元尺寸。存储膜06的总厚度t为第一地址线上表面01p与第二地址线下表面02p之间距离。一般情况下(如存储06仅含有选通膜03和编程膜04),t=ts+tm。其中,选通膜03的厚度为ts,编程膜04的厚度为tm。很多情况下,ts和tm不随f微缩而减少。当f微缩到较小(如10nm)节点时,存储元的厚宽比(t:f)较大,导致工艺难度增加。

3.交叉阵列存储器已被用作三维一次编程存储器(3d-otp)和三维多次编程存储器(3d-mtp)。3d-otp的代表产品是matrix半导体公司生产的3-d otp(图2a);3d-mtp的代表产品是英特尔公司生产的3d-xpoint(图2b)。这两种产品都面临“厚宽比(t:f)过大”的挑战,导致产品难以升级换代。

4.图2a是3-d otp存储元00的截面图,其存储膜06含有选通膜03和编程膜04。其中,选通膜03为二极管膜,在编程时,为了避免反向偏置的二极管产生较大的漏电流,二极管需要具有较大的反向击穿电压,故其厚度ts较大,为~300nm;编程膜04为反熔丝(antifuse)膜,它采用二氧化硅,厚度tm很小,一般小于10nm;由于反熔丝膜04的厚度tm远小于二极管膜03的厚度ts,存储膜06的厚度t主要由二极管膜03的厚度ts决定。在图2a中,存储元尺寸f为130nm,二极管03的厚宽比(ts:f)为2.3:1,尚可接受。但是,由于二极管03的厚度ts不随着f微缩而减少。这导致f微缩后,二极管03的厚宽比过大:如微缩到f=10nm节点,则厚宽比达到30:1,工艺上较难实现。

5.图2b是3d-xpoint存储元00的截面图,其存储膜06也含有选通膜03和编程膜04。其中,选通膜03为ots(ovonic threshold switch)膜,它呈现ovshinsky现象,即在电场作用下从非导通态变为导通态或反之;编程膜04含有相变材料(pcm),它可在晶态(低阻态)和非晶态(高阻态)之间非易失地转换。在图2b中,存储元尺寸f为20nm;ots膜03的厚度ts(包括周围的界面隔离材料)为~50nm,pcm膜04的厚度tm(包括周围的界面隔离材料)为~70nm,故存储膜06的总厚度t为~120nm。相应地,存储膜06的厚宽比为6:1,这在f=20nm节点尚可接受,但进一步微缩的空间有限。例如,在f=10nm节点,厚宽比将增加到12:1。这么大的厚宽比在工艺上实现也具有挑战性。

第二地址线;03-选通膜;04-编程膜;01p-第一地址线上表面;02p-第二地址线下表面;30或06-存储膜;10p-第一表面;20p-第二表面;1000-超薄存储器;0x-超薄存储元;30a-ots膜;30b-反熔丝膜;30c-隔离膜;30d-界面隔离膜;0-衬底;100-第一存储层;200-第二存储层;120v或220v-通道孔;0y-纵向存储元;40-存储孔;16z-存储串;50-绝缘介质。

具体实施方式

33.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。

34.因此,以下对在附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的范围,而是仅仅表示本技术的选定实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

35.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

36.在本技术的描述中,需要说明的是,若出现术语“上”、“下”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

37.此外,若出现术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

38.需要说明的是,在不冲突的情况下,本技术的实施例中的特征可以相互结合。

39.本发明提出一种具有超薄存储膜的存储器(简称为“超薄存储器”),它结合3-d otp(图2a)中反熔丝膜即编程膜04的厚度tm很薄(一般《10nm)以及3d-xpoint(图2b)中ots膜即选通膜03的厚度ts较薄(一般≤50nm)的特性,实现超薄存储膜。其存储膜06采用ots膜作为选通膜03、采用反熔丝膜作为编程膜04(在图7的实施例中甚至不需要反熔丝膜),总厚度t不大于60nm,地址线的宽度f不大于60nm。即使f微缩到10nm,存储膜06的厚宽比(t:f)也仅有6:1,易于制造。注意到,为了不增加其总厚度t,存储膜06不含有单独的pcm膜。鉴于其编程膜04为反熔丝膜,超薄存储器是一种一次编程存储器。

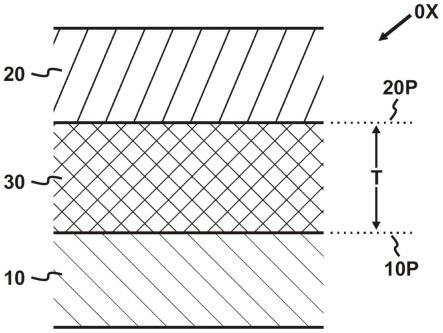

40.如图3a和图3b所示,超薄存储器1000含有多条位于同一平面的第一地址线(10a,10b

…

),其上表面构成第一表面10p;多条位于另一平面的第二地址线(20a,20b

…

),其下表面构成第二表面20p;第二地址线(20a,20b

…

)与第一地址线(10a,10b

…

)相交。存储膜30介于第一和第二表面(10p,20p)之间、并与第一和第二地址线(10a,10b;20a,20b)耦合。存储膜30含有一层ots膜。注意到,由于存储膜30不含有单独的pcm膜(参见图2b),故其总厚度t不大于60nm,易于微缩。

41.图4a-图4d为四种超薄存储元0x的实施例,其存储膜30均含有ots膜30a和反熔丝膜30b。为了获得更好的界面特性,在ots膜30a的周围可以含有一层界面隔离材料,如碳薄膜等。反熔丝膜30b是一层薄的绝缘介质(如二氧化硅),它在编程前处于高阻态;在编程电

压下,反熔丝膜被击穿,不可逆地进入低阻态。整体说来,存储膜30的总厚度t不大于60nm。

42.在图4a的实施例中,反熔丝膜30b可以直接淀积(如通过cvd或ald等方法)形成在第一地址线10之上,也可以通过将第一地址线10中的金属表面直接氧化或氮化生成(如直接将第一地址线中金属电极的上表面氧化或氮化)。在图4b的实施例中,反熔丝膜30b可以直接淀积(如通过cvd或ald等方法)形成在ots膜30a上,也可以通过将ots膜30a氧化或氮化生成(如直接将ots膜中单元素碲的上表层氧化或氮化)。

43.图4c的实施例在ots膜30a和反熔丝膜30b之间进一步加入一层隔离(barrier)膜30c。该隔离膜30c含有一导体材料,主要是为了避免反熔丝膜30b编程时的高温效应影响ots膜30a。反熔丝膜30b除了淀积法形成,也可以通过将隔离膜30c中的导体材料直接氧化或氮化生成。图4d的实施例在ots膜30a和反熔丝膜30b与第一和第二地址线10、20之间加入界面隔离膜30d(如碳元素),以改善界面性能。

44.为了进一步降低存储膜的总厚度t,简化存储元的结构,使存储元更易于微缩和制造,本发明还提出一种基于ots膜的超薄一次编程存储器(简称为“ots/otp存储器”)。它基于ots膜的forming(或firing)特性。如图5所示,ots膜多数呈现一种forming特性——在对ots膜进行电流-电压(i-v)扫描时,首次(第1次,指ots膜成膜之后的首次)翻转曲线包括:ots膜在正向扫描(0

→1→

2)时于v

form

处导通,在反向扫描(3

→4→

5)时于v

hold

处断开;后续(第2次、第3次

…

)翻转曲线包括:正向扫描(6

→7→

8)时于v

th

处导通,反向扫描也是(3

→4→

5)。注意,后续(第2次、第3次

…

)翻转中每次的v

th

基本接近,而首次(第1次)翻转的v

form

大于后续(第2次、第3次

…

)翻转的v

th

,即v

form

》v

th

。为区分它们,首次翻转被称为forming(或firing),后续翻转被称为switching(包括switch-on和switch-off)。

45.forming过程在3d-xpoint中被认为是一种麻烦。这是因为每个3d-xpoint存储元在使用之前,需要进行初始化,即用较大的v

form

将其状态转换,使其后续翻转电压v

th

基本接近。由于3d-xpoint存储元数量众多(128gb),这需要消耗很长时间。因此,工业界一直在寻找不需forming(forming-free)的ots膜。例如,hennen等著《forming-free mott-oxide threshold selector nanodevice showing s-type ndr with endurance(》10^12cycles),excellent v

th stability(《5%),fast(《10ns)switching,and promising scaling properties》,2018international electron device meeting(iedm)technical digest,pp.867-870。

46.图6(表1)比较多种ots材料的性能参数,它们一般含有硫属元素(halcogen),如te基、se基、s基(硫化物)和o基(氧化物)。一种典型的ots材料为硫系玻璃(chalcogenide glass),其例子包括:tin/astegesin/tin(sungho kim et al,vlsi 2013,pp.t240-1)。此外,基于单元素(如单元素碲te或单元素锑sb)的ots材料(shen et al,science 374,pp.1390-1394,2021)也具有良好性能。由于它含有单一元素,ots材料的制造工艺将更加容易。对于单元素ots膜来说,ots膜30a所含的所有元素中,单一元素(如单元素碲te或单元素锑sb)的摩尔占比超过80%。

47.ots/otp存储器不嫌ots膜的forming过程麻烦,反而利用ots膜的(首次)forming过程实现存储元的写操作、(后续)switching过程实现存储元的读操作,从而实现一次编程存储器(otp)。如图7所示,ots/otp存储元0x含有第一和第二地址线10、20、以及介于它们之间的存储膜30,存储膜30含有一层ots膜30a。ots膜30a不仅具有选通膜的功能,而且还具有

存储膜的功能。因此,ots/otp存储元0x完全不需要含有单独的编程膜,它为单膜结构(1s结构,s指选通膜),而非3d-xpoint等的1s1r结构(s指选通膜、r指编程膜)。ots/otp存储元具有结构简单、厚宽比小、易制造、易微缩等优点。与图4d类似,在ots膜30a与第一地址线10和/或第二地址线20之间还可以含有界面隔离膜30d。为了保证必要的厚宽比,作为一个实施例,存储膜30的总厚度t不大于60nm;作为另一个实施例,第一地址线10或第二地址线20的线宽f不大于60nm。

48.三维存储器可以分为三维横向存储器和三维纵向存储器。三维横向存储器中所有地址线均为水平地址线;三维纵向存储器含有至少一组竖直地址线。如图8所示,三维横向超薄存储器1000含有一半导体衬底0(包括晶体管0t及其互连线0m)。在衬底0上堆叠第一存储层100,在第一存储层100上堆叠第二存储层200。地址线通过接触通道孔120v、通道孔220v与衬底0耦合。有关三维横向存储器的细节可参考美国专利us 5,835,396所披露的三维只读存储器。三维横向存储器的存储元0x中被称为横向存储元。

49.图9和图10为三维纵向超薄存储器1000及其纵向存储元0y。如图9所示,纵向存储元0y含有水平的第一地址线(水平地址线)10。存储孔40穿透水平地址线即第一地址线10。之后,在存储孔40边墙上先形成一存储膜30。然后,在存储孔40中继续填充导体材料形成竖直的第二地址线(竖直地址线)20。这样,存储膜30形成于水平地址线即第一地址线10和竖直地址线20之间。注意到,存储膜30含有一层ots膜30a,但不含有单独的pcm膜。为了减少存储孔40的直径,存储膜30的总厚度t最好不大于60nm。在另一实施例中,存储膜30不含有单独的编程膜。

50.三维纵向超薄存储器1000(图10)含有一衬底0(包括晶体管及其互连线)。在这之上有多条相互垂直堆叠的、水平地址线10a-10h。水平地址线10a-10h之间由绝缘介质50隔开。存储孔40穿透水平地址线10a-10h。之后,在存储孔40边墙上先形成存储膜30(如ots膜30a)。然后,在存储孔40中继续填充导体材料形成竖直地址线即第二地址线20。这样,竖直地址线即第二地址线20、存储膜30分别与水平地址线10a-10h形成多个纵向存储元0ya-0yh。这些存储元0ya-0yh构成存储串16z。相对于3d-nand的存储孔中含有5层薄膜,三维纵向超薄存储器1000的存储孔40只含有2层薄膜:存储膜30(如ots膜30a)和竖直地址线即第二地址线20。当然,在本发明的其它实施例中,存储孔40还可以含有反熔丝膜等。总体说来,三维纵向超薄存储器1000结构简单,其存储孔40可以做得更小,工艺更为简单,成本更为低廉。

51.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1