一种倒装电极及其制作方法与流程

1.本发明涉及倒装电极设计,尤其涉及一种提升倒装电极性能的制作方法。

背景技术:

2.氮化镓基发光二极管(light emitting diode,led)具有功能损耗低、寿命长、可靠性好等优点被广泛应用于信号灯、背光源显示、汽车照明及室内照明等领域。随着大功率高光效led的普及和应用,倒装产品(filp chip)具有更广阔的应用市场、应用价值更高。目前在处理芯片级封装技术上,led固晶机、贴片机等传统贴片封装设备在处理芯片与蓝膜分离上,普遍使用顶针刺破蓝膜的办法;本产品设计的倒装结构产品需要进行上述的顶针性能验证,现有技术中如cn 201320549532.1和cn 201320550892.3介绍的倒装芯片,均存在电极耗费高的问题。

技术实现要素:

3.为此,需要提供一种能够提高倒装电极的芯片抗顶针测试性能的方法。

4.一种倒装电极的制作方法,包括如下步骤,

5.制作第1层cr层;

6.制作第2层alcu合金层;

7.交替蒸镀ti层和pt层各3层,形成第3

‑

8层的tipt复合层;

8.制作第9层au层;

9.蒸镀第10ti层及第11层pt层;

10.制作第12层au层;

11.制作第13层ti层。

12.具体地,包括步骤,

13.制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜;

14.制作第2层alcu合金层,以5a/s的镀率进行镀膜;

15.交替蒸镀ti层和pt层各3层,以1a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜,形成第3

‑

8层的tipt复合层;

16.制作第9层au层,以10a/s的镀率进行镀膜;

17.蒸镀第10ti层及第11层pt层,以1a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜;

18.制作第12层au层,以10a/s的镀率进行镀膜;

19.制作第13层ti层,以1a/s的镀率进行ti层镀膜。

20.具体地,包括步骤,

21.制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜;

22.制作第2层alcu合金层,以5a/s的镀率进行镀膜;

23.交替蒸镀ti层和pt层各3层,以2a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层

镀膜,形成第3

‑

8层的tipt复合层;

24.制作第9层au层,以10a/s的镀率进行镀膜;

25.蒸镀第10ti层及第11层pt层,以2a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜;

26.制作第12层au层,以10a/s的镀率进行镀膜;

27.制作第13层ti层,以2a/s的镀率进行ti层镀膜。

28.具体地,包括步骤,

29.制作第1层cr层,镀膜厚度为30a;

30.制作第2层alcu合金层,镀膜厚度为1500a;

31.交替蒸镀ti层和pt层各3层,每层ti厚度600a,每层pt厚度500a,形成第3

‑

8层的tipt复合层;

32.制作第9层au层,镀膜厚度为11000a;

33.蒸镀第10ti层镀膜厚度1500a,蒸镀第11层pt层,镀膜厚度700a;

34.制作第12层au层,镀膜厚度1000a;

35.制作第13层ti层,镀膜厚度500a。

36.具体地,包括步骤,制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜,镀膜厚度为30a;

37.制作第2层alcu合金层,以5a/s的镀率进行镀膜,镀膜厚度为1500a;

38.交替蒸镀ti层和pt层各3层,其中每层ti厚度600a,每层ti先以1a/s的镀率进行300a的镀膜,再以2a/s的镀率进行300a的镀膜,每层pt厚度500a,形成第3

‑

8层的tipt复合层;每层ti厚度600a,每层pt厚度500a,形成第3

‑

8层的tipt复合层;

39.制作第9层au层,以10a/s的镀率进行镀膜,镀膜厚度为11000a;

40.蒸镀第10层ti层,以1a/s的镀率进行ti层镀膜,镀膜厚度1500a,蒸镀第11层pt层,以1a/s的镀率进行pt层镀膜,镀膜厚度700a;

41.制作第12层au层,以10a/s的镀率进行镀膜,镀膜厚度1000a;

42.制作第13层ti层,以2a/s的镀率进行ti层镀膜,镀膜厚度500a。

43.上述技术方案,可以改善倒装电极芯片在顶针测试实验中的性能表现,并能够降低使用成本。

附图说明

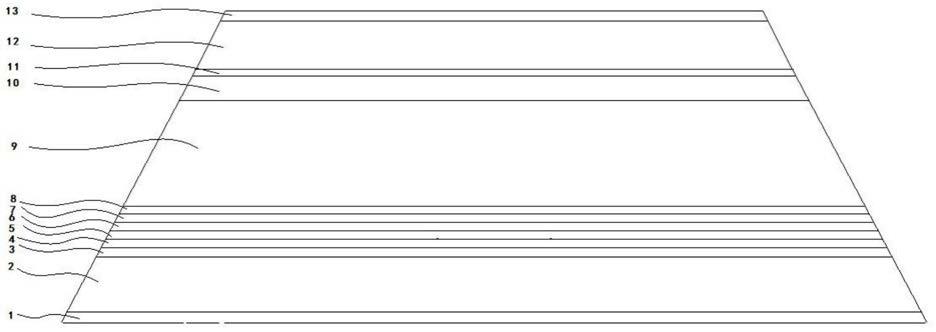

44.图1为具体实施方式所述的倒装电极示意图;

45.图2为具体实施方式所述的顶针实验批次结果示意图;

46.图3为具体实施方式所述的小批次重复实验结果示意图。

具体实施方式

47.为详细说明技术方案的技术内容、构造特征、所实现目的及效果,以下结合具体实施例并配合附图详予说明。

48.一种倒装电极的制作方法,包括如下步骤,

49.制作第1层cr层;cr层用于实现欧姆接触和提升与底材的粘附性,

50.制作第2层alcu合金层;alcu合金层用于增加芯片反射率及可靠性。

51.交替蒸镀ti层和pt层各3层,形成第3

‑

8层的tipt复合层;其中ti层能够增加金属层间的粘附性,pt层用于提高老化能力。

52.制作第9层au层;au层能够增强导电能力,

53.蒸镀第10ti层及第11层pt层;ti层能够增加金属层间的粘附性,pt层用于提高老化能力。

54.制作第12层au层;au层能够增强导电能力,

55.制作第13层ti层;ti层能够增加与芯片dbr层间的粘附性。

56.结合图1我们可以看到,各层按照从底到面,1

‑

13层的方式排布,通过该种排布的设计,最面上实现ti层包覆,能够使电极顶层与芯片dbr层结合地更为紧密,从而提升芯片抗顶针实验的强度。同时在两层au层之间加入tipt层的设计,在保证结构强度的同时,降低了au层的厚度,因而还降低了au的使用,从而降低了整体的设计成本。

57.在图2所示的顶针实验批次结果中我们可以看到,顶针实验对上述方案制成的芯片实验结果为,严重破损12.5%,轻微破损达48.75%,无损率达38.75。对比以往的常规做法的6.75的无损率有较大提升。在图3所示的小批次重复验证结果中,严重破损2.5%,轻微破损达50%,无损率达47.5。

58.具体地,包括步骤,

59.制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜;

60.制作第2层alcu合金层,以5a/s的镀率进行镀膜;

61.交替蒸镀ti层和pt层各3层,以1a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜,形成第3

‑

8层的tipt复合层;

62.制作第9层au层,以10a/s的镀率进行镀膜;

63.蒸镀第10ti层及第11层pt层,以1a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜;

64.制作第12层au层,以10a/s的镀率进行镀膜;

65.制作第13层ti层,以1a/s的镀率进行ti层镀膜。

66.通过上述镀率设置,能够让各膜层内部更加致密,保证性能的同时能够让各膜层之间的结合更为紧密,从而提升顶针实验表现。

67.具体地,包括步骤,制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜;

68.制作第2层alcu合金层,以5a/s的镀率进行镀膜;

69.交替蒸镀ti层和pt层各3层,以2a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜,形成第3

‑

8层的tipt复合层;

70.制作第9层au层,以10a/s的镀率进行镀膜;

71.蒸镀第10ti层及第11层pt层,以2a/s的镀率进行ti层镀膜,以1a/s的镀率进行pt层镀膜;

72.制作第12层au层,以10a/s的镀率进行镀膜;

73.制作第13层ti层,以2a/s的镀率进行ti层镀膜。

74.通过不同的镀率设置,能够让各膜层内部更加致密,保证性能的同时能够让各膜层之间的结合更为紧密,从而提升顶针实验表现。

75.制作第1层cr层,镀膜厚度为30a;

76.制作第2层alcu合金层,镀膜厚度为1500a;

77.交替蒸镀ti层和pt层各3层,每层ti厚度600a,每层pt厚度500a,形成第3

‑

8层的tipt复合层;

78.制作第9层au层,镀膜厚度为11000a;

79.蒸镀第10ti层镀膜厚度1500a,蒸镀第11层pt层,镀膜厚度700a;

80.制作第12层au层,镀膜厚度1000a;

81.制作第13层ti层,镀膜厚度500a。上述厚度方案允许15%的误差调整,通过对各层的厚度设计,能够更好地发挥电极的整体性能。

82.另一些实施例中,包括步骤,

83.制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜,镀膜厚度为30a;

84.制作第2层alcu合金层,以5a/s的镀率进行镀膜,镀膜厚度为1500a;

85.交替蒸镀ti层和pt层各3层,其中每层ti厚度600a,每层ti先以1a/s的镀率进行300a的镀膜,再以2a/s的镀率进行300a的镀膜,每层pt厚度500a,形成第3

‑

8层的tipt复合层;每层ti厚度600a,每层pt厚度500a,形成第3

‑

8层的tipt复合层;

86.制作第9层au层,以10a/s的镀率进行镀膜,镀膜厚度为11000a;

87.蒸镀第10层ti层,以1a/s的镀率进行ti层镀膜,镀膜厚度1500a,蒸镀第11层pt层,以1a/s的镀率进行pt层镀膜,镀膜厚度700a;

88.制作第12层au层,以10a/s的镀率进行镀膜,镀膜厚度1000a;

89.制作第13层ti层,以2a/s的镀率进行ti层镀膜,镀膜厚度500a。

90.上述方案通过在ti层和pt层的复合层中进行ti的不同速率成膜,能够使得成膜的ti更加紧密,性能更好,具有更强的抗顶针实验性能。

91.另一些进一步的实施例中,制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜,镀膜厚度为27a;

92.制作第2层alcu合金层,以5a/s的镀率进行镀膜,镀膜厚度为1350a;

93.交替蒸镀ti层和pt层各3层,其中每层ti厚度540a,每层ti先以1a/s的镀率进行270a的镀膜,再以2a/s的镀率进行270a的镀膜,每层pt厚度450a,形成第3

‑

8层的tipt复合层;每层ti厚度540a,每层pt厚度450a,形成第3

‑

8层的tipt复合层;

94.制作第9层au层,以10a/s的镀率进行镀膜,镀膜厚度为9900a;

95.蒸镀第10层ti层,以1a/s的镀率进行ti层镀膜,镀膜厚度1350a,蒸镀第11层pt层,以1a/s的镀率进行pt层镀膜,镀膜厚度630a;

96.制作第12层au层,以10a/s的镀率进行镀膜,镀膜厚度900a;

97.制作第13层ti层,以2a/s的镀率进行ti层镀膜,镀膜厚度450a。

98.上述方案通过在ti层和pt层的复合层中进行ti的不同速率成膜,能够使得成膜的ti更加紧密,性能更好,具有更强的抗顶针实验性能。

99.另一些实施例中,包括步骤,

100.制作第1层cr层,以0.2a/s的镀率对芯片表面进行镀膜,镀膜厚度为33a;

101.制作第2层alcu合金层,以5a/s的镀率进行镀膜,镀膜厚度为1650a;

102.交替蒸镀ti层和pt层各3层,其中每层ti厚度660a,每层ti先以1a/s的镀率进行

330a的镀膜,再以2a/s的镀率进行330a的镀膜,每层pt厚度500a,形成第3

‑

8层的tipt复合层;每层ti厚度660a,每层pt厚度550a,形成第3

‑

8层的tipt复合层;

103.制作第9层au层,以10a/s的镀率进行镀膜,镀膜厚度为12100a;

104.蒸镀第10层ti层,以1a/s的镀率进行ti层镀膜,镀膜厚度1650a,蒸镀第11层pt层,以1a/s的镀率进行pt层镀膜,镀膜厚度770a;

105.制作第12层au层,以10a/s的镀率进行镀膜,镀膜厚度1100a;

106.制作第13层ti层,以2a/s的镀率进行ti层镀膜,镀膜厚度550a。

107.上述方案通过在ti层和pt层的复合层中进行ti的不同速率成膜,能够使得成膜的ti更加紧密,性能更好,具有更强的抗顶针实验性能。

108.需要说明的是,尽管在本文中已经对上述各实施例进行了描述,但并非因此限制本发明的专利保护范围。因此,基于本发明的创新理念,对本文所述实施例进行的变更和修改,或利用本发明说明书及附图内容所作的等效结构或等效流程变换,直接或间接地将以上技术方案运用在其他相关的技术领域,均包括在本发明专利的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1