一种超宽带雷达信号模拟平台的制作方法

1.本实用新型涉及数字信号模拟领域,尤其涉及一种超宽带雷达信号模拟平台。

背景技术:

2.随20世纪90年代以来,随着宽带微波器件的发展和软件算法数字信号处理能力的增强,超宽带雷达的性能已经达到较高水平。超宽带雷达的高分辨率,强穿透性等特点意味着超宽带雷达具有以下优越的性能:高距离分辨率,高度隐蔽性,低截获率及抗干扰性;信号多波束传播时具有对抗衰减的能力;与窄带信号相比具有好的电磁兼容性和频谱利用率。距离分辨力和发射信号带宽成正比,要提高雷达的距离分辨力,就需要增大发射信号带宽。研制超宽带的雷达信号源成为高分辨力雷达系统研制的关键。随着信号带宽的增加,高速数字电路信号完整性的诸多问题凸现,雷达信号源的研制变得越来越困难。因此,研究高速数字电路信号完整性,研制超宽带雷达信号源,对发展高分辨力雷达有着重要的意义。

技术实现要素:

3.为了解决上述现有技术的不足之处,本实用新型的目的在于提供一种超宽带雷达信号模拟平台,以满足电子电路的发展趋势。

4.为了实现上述目的,本实用新型提供了一种超宽带雷达信号模拟平台;所述模拟平台包括电源模块、串口通信模块、千兆网口模块、用户自定义i/o模块、核心计算单元、辅助计算单元、存储模块、时钟系统、数模转换模块、模拟信号调理模块和光口模块;所述电源模块与所述核心计算单元、辅助计算单元、存储模块和数模转换模块均电连接,用于系统供电;所述串口通信模块与所述核心计算单元、辅助计算单元均通信连接,用于提供低速数据通信,方便调试;所述千兆网口模块与所述核心计算单元通信连接,用于网络通信,接收上位机下发的指令并上传工作状态;所述用户自定义i/o模块与所述辅助计算单元通信连接,用于提供用户自定义i/o,灵活扩展功能;所述核心计算单元与所述辅助计算单元通信互联为emif,sriox4,pciex4;所述核心计算单元用于构成雷达模拟信号生成算法的核心计算力,所述辅助计算单元用于将生成的雷达模拟信号合成并发送出去;所述存储模块与所述核心计算单元通信连接,用于缓存核心计算数据;所述时钟系统与所述辅助计算单元通信连接,用于为系统工作提供时钟信号;所述数模转换模块与所述辅助计算单元通信连接,用于完成数字信号到模拟信号的转换;所述模拟信号调理模块与所述数模转换模块通信连接,用于完善提高生产模拟信号的信号完整性;所述光口模块与所述辅助计算单元通信连接,用于提供光口,实现与外部的高速数据交换。

5.优选的,所述电源模块由6个储能电源子模块组成,输入电压为8~12v,功耗为45~50w。

6.优选的,所述核心计算单元包括dsp1、dsp2、phy1、phy2、nand flash1和nand flash2;所述dsp1和所述dsp2通过hyper link 5gbps进行互联;所述phy1与所述dsp1通信连接,用于接收所述千兆网口模块的信号,并将信号传输至所述dsp1;所述phy2与所述dsp2

通信连接,用于接收所述千兆网口模块的信号,并将信号传输至所述dsp2;所述nand flash1与所述dsp1通信连接,用于设定所述dsp1的flash为nand模式;所述nand flash2与所述dsp2通信连接,用于设定所述dsp2的flash为nand模式。

7.优选的,所述存储模块包括10颗ddr3内存颗粒,支持ecc校验功能;所述ddr3内存颗粒中5颗与所述dsp1通信连接,5颗与所述dsp2通信连接。

8.优选的,所述辅助计算单元包括fpga和spi flash;所述spi flash与所述fpga通信连接,用于设定所述fpga的flash为spi模式。

9.优选的,所述数模转换模块包括并联的4路模数转换芯片dac,每通道采样率1250m,芯片采用ad9129芯片。

10.优选的,所述模拟信号调理模块包括并联的4路调理电路。

11.优选的,所述光口模块包括并联的8路光口,容量为10g。

12.同现有技术相比,本实用新型的有益效果体现在:

13.(1)本实用新型基于信号完整性的理论,解决了雷达信号多路径发射的相位同步问题,以及模拟雷达回波的多路径问题。

14.(2)本实用新型可以解决信号完整性的问题,模拟雷达实际应用场景。

15.(3)本实用新型确保了设计的可靠性,缩短了研发周期,降低了研发成本,在数字系统设计中可以广泛适用。

附图说明

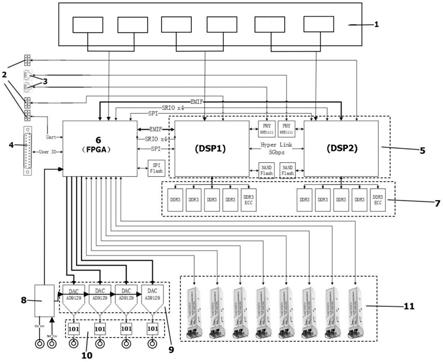

16.图1为本实用新型的一种超宽带雷达信号模拟平台的结构示意图;

17.图2为本实用新型的所述dsp1和dps2的加载方式示意图;

18.图3为本实用新型的所述dsp1和dps2的ddr3接口设计图;

19.图4为本实用新型的所述数模转换模块的dac设计图;

20.图5为本实用新型的所述核心计算单元与所述辅助计算单元通信互联的原理图。

具体实施方式

21.为了能够进一步了解本实用新型的结构、特征及其他目的,现结合所附较佳实施例附以附图详细说明如下,本附图所说明的实施例仅用于说明本实用新型的技术方案,并非限定本实用新型。

22.首先,如图1所示,图1是本实用新型的一种超宽带雷达信号模拟平台的结构示意图;所述模拟平台包括电源模块1、串口通信模块2、千兆网口模块3、用户自定义i/o模块4、核心计算单元5、辅助计算单元6、存储模块7、时钟系统8、数模转换模块9、模拟信号调理模块10和光口模块11;所述电源模块1与所述核心计算单元5、辅助计算单元6、存储模块7和数模转换模块9均电连接,用于系统供电,输入电压为8~12v,功耗为45~50w;所述核心计算单元5包括dsp1、dsp2、phy1、phy2、nand flash1和nand flash2;所述dsp1和所述dsp2采用ti dsp tms320c6678;所述dsp1和所述dsp2外接所述千兆网口模块3和存储模块7;所述辅助计算单元6包括fpga和spi flash;所述fpga芯片采用xilinx fpga xc72k325t ffg900

‑

2 i;所述fpga外接所述串口通信模块2、用户自定义i/o模块4、数模转换模块9和光口模块11;所述fpga flash为spi模式;所述数模转换模块9包括并联的4路模数转换芯片dac,每通道

采样率1250m,芯片采用ad9129芯片;所述光口模块11包括并联的8路光口,容量为10g;所述dsp1与所述fpga互联为emif,sriox4,pciex4。

23.进一步地,请参看图2,图2为本实用新型的所述dsp1和dps2的加载方式示意图;所述dsp1和所述dsp2采用ti dsp tms320c6678;tms320cc6678是ti推出的新一代dsp芯片,它的内核、外设接口和内部互联的能力比c64x系列的dsp有了非常大的提高。首先,它具有八个处理器核c66x,并且c66x核同时具备320gmac的定点和160gflop的浮点处理能力。然后,其外设集成了新一代的srio2.1、pcie2.0和hyperlink等高速接口。另外,内部互联也采用新的teranet开关互联技术,具有非常高的速率。

24.dsp的全局控制管脚为所述dsp1和所述dsp2的配置电路,用于dsp的初始化设置和状态控制,如加载方式设置等。c6678的配置管脚电平均为1.8v lvcmos。dsp在上电复位时,会根据配置管脚的状态来设置其工作模式。c6678支持多种加载方式,这些方式通过bootmode[12:0]来设置,其中bootmode[2:0]用来选择boot器件,bootmode[9:3]用来对所选的boot器件进行设置,bootmode[12:10]用来设置dsp的系统锁相环,设置如下表所示,其中bootmode[9:3]的含义根据boot器件的不同而不同。本方案首选emif16的加载方式,同时可通过寄存器配置,灵活选择其他加载方式。

[0025]

此外,请参看图3,图3为本实用新型的所述dsp1和dps2的ddr3接口设计图;基于dsp tms320cc6678,c6678中的ddr3控制器用于ddr3 sdram的访问,它在c6678存储映射中的起始地址为0x80000000,其主要特征如下:1)支持jesd79

‑

3c ddr3

[0026]

sdram标准;2)数据位宽为64bit/32bit/16bit;3)寻址空间为两个ce,最大8gb;4)最高速率为ddr3

‑

1600;5)cas latency为5、6、7、8、9、10、11;6)bank数为1,2,4,8;7)突发长度为8;8)页大小为256,512,1024,2048;9)支持自动初始化和自刷新(self

‑

refresh);10)支持ecc。

[0027]

板卡单片dsp按照512mb容量设计,最大可兼容4gb,sdram必须占用1个dce空间,数据位宽设计为64bit,设计时选用4片16bit位宽sdram mt41j128m16jt

‑

125,同时板卡支持ecc模式。为了统一选型,用做存储ecc数据的芯片选用相同的sdrammt41j128m16jt

‑

125,但只用其低8bit。

[0028]

另外,对于所述fpga,其板卡主芯片采用xilinx kintex

‑

7 fpga xc7k325t

‑

ffg900

‑

2,带pci express endpoint模块、高速串行通讯接口、ddr3内存接口和用户自定义i/o接口。所述fpga的缓存由两颗ddr3组:两片mt41k256m16ha

‑

125为一组,组成256x32方式缓存;所述fpga上接一个50m的单端时钟,作为源时钟。另外需要1片200m的差分时钟,所有时钟都接到所述fpga的全局时钟资源上。

[0029]

另外,请参见图4,图4为本实用新型的所述数模转换模块的dac设计图;所述数模转换模块9中的dac芯片采用4颗adi公司的高速模数转换器ad9129(14位、最高支持5.7gsps(2.85gsps直接rf合成)),输出阻抗50欧姆;工作在1.25gsps,最高支持2.5gsps。

[0030]

另外,请参见图5,图5为本实用新型的所述核心计算单元与所述辅助计算单元通信互联的原理图;所述dsp1与所述fpga通过高速收发器接口互联,采用srio接口协议,工作在x4模式@5ghz,从而实现dsp与fpga之间的高速数据交换;所述dsp1与所述fpga的连接采取交流耦合方式,耦合电容靠近接收端。

[0031]

另外,所述dps1与所述dsp2通过hyper link@5gbps进行互联,实现两颗核心处理

单元dsp之间的高速数据交换功能。

[0032]

最后,本实用新型的一种超宽带雷达信号模拟平台,其具体的技术特点如下:

[0033]

(1)本实用新型基于信号完整性的理论,解决了雷达信号多路径发射的相位同步问题,以及模拟雷达回波的多路径问题。

[0034]

(2)本实用新型可以解决信号完整性的问题,模拟雷达实际应用场景。

[0035]

(3)本实用新型确保了设计的可靠性,缩短了研发周期,降低了研发成本,在数字系统设计中可以广泛适用。

[0036]

需要声明的是,上述实用新型内容及具体实施方式意在证明本实用新型所提供技术方案的实际应用,不应解释为对本实用新型保护范围的限定。本领域技术人员在本实用新型的精神和原理内,当可作各种修改、等同替换或改进。本实用新型的保护范围以所附权利要求书为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1