一种基于FPGA的红外凝视成像系统高速通信链路自适应高精度调整方法与流程

一种基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法

技术领域

1.本发明涉及信号采集处理、嵌入式开发等交叉应用技术领域,具体涉及一种基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法。

背景技术:

2.红外凝视成像系统目前广泛应用于各个领域,尤其在现代高科技战争中,为了能够尽早地发现敌方卫星及来袭导弹、飞机等军事目标并使制导系统尽快响应,要求红外凝视成像系统具备全天候实时处理传输大量数据的能力。只有及时地完成发现目标、跟踪目标、捕获和锁定目标等工作流程,才能对其实施有效地拦截或攻击。由于红外凝视成像系统所属的武器系统经常工作于严寒酷暑等各种严苛的作战环境中,因此红外凝视成像系统也必须在极限温度的条件下完成数据实时处理和可靠传输的任务。

3.随着红外凝视成像系统信息处理能力要求的不断提高,信息复杂度和数据量的提升以及处理时间的减少,弹上处理平台必然进行更新换代,数据通信速率的提高也必不可少,保证红外凝视成像系统极限温度下数据实时处理和可靠传输的难度也与日俱增。

4.现阶段,红外凝视成像系统高低温的环境带来的高速通信链路时序特性漂移需要设计人员在设计之初就需要通过参数约束的方法保留时序裕量,以保证通信可靠,然而实际情况往往与预估情况不一致,所以就会存在极限温度情况下高速通信质量不佳甚至失效的现象;且由于红外凝视成像系统(芯片,印制板等)本身热性能的差异,即使设计约束参数设置正确,也难以保证其覆盖性。

技术实现要素:

5.本发明的目的在于:提供一种基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法。根据红外凝视成像系统内fpga芯片附近多点采样的温度值,通过均值运算,确定已锁定的fpga内部个逻辑区域对应的实际结温,依据该结温得到当前通信链路使用的逻辑区域对应的延时长度,自动添加相应数目组合逻辑,进而完成通信链路延时的自适应调整,保证全温范围下红外凝视成像系统内部高速通信链路稳定可靠。

6.本发明通过以下技术方案实现:一种基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法,包括如下步骤:

7.1)计算得到各测量点对应的fpga芯片结温;

8.2)计算得到高速通信链路调整补偿延时长度;

9.3)插入指定数目的组合逻辑资源,精确控制通信链路延时。

10.所述步骤1)中,采用高性能均匀导热硅脂层粘连高精度温度传感器和fpga芯片的外壳,采用高精度温度传感器均匀分布在fpga芯片表面。

11.所述步骤1)的具体过程为:依据导热硅脂的导热系数以及fpga芯片外壳至内核的热阻参数,以及高精度温度传感器测得的各点温度值,计算得到各测量点对应的fpga芯片

内核温度值。

12.所述fpga芯片内核温度值的计算公式如下:

13.δt=w

·

θ

14.δt——fpga芯片内核与外壳的温差;

15.θ——fpga芯片内核-外壳的热阻参数;

16.w——fpga平均功耗;

17.t

n’=δt+tn=tn+w

·

θ;

18.t

n’——fpga芯片内核温度值;

19.tn——温度传感器测得的fpga芯片表面各点温度值。

20.所述步骤2)的具体过程为:锁定实现高速通信链路的fpga片内资源布局,并确定该布局区域与温度测试点的位置关系,依据该位置关系,通过均值运算,获得实现该高速通信链路资源对应位置的芯片核心温度t

pt’;测量全温t

min

~t

max

范围内数据信号相较于时钟信号的延时变化δt,得到t

pt’条件下走线补偿延时长度δt

pt

;t

max

为最高工作温度,t

min

为最低工作温度。

21.所述实现该高速通信链路资源对应位置的芯片核心温度t

pt’的具体计算过称为:

22.t

pt’=(d

t1

·

t1’

+d

t2

·

t2’

+d

t3

·

t3’

+d

t4

·

t4’

)/(d

t1

+d

t2

+d

t3

+d

t4

)

23.d

t1

、d

t2

、d

t3

、d

t4

——相邻探测点与当前探测点距离;

24.t1’

、t2’

、t3’

、t4’

——相邻探测点芯片内核温度;

25.所述补偿延时长度δt

pt

=δt*(t

pt

’‑

t

min

)/(t

max-t

min

)。

26.所述步骤3)的具体过程为,依据fpga内部各种组合逻辑单元的延时,并依据步骤三中计算得到的补偿延时δt

pt

,计算满足要求的组合逻辑资源的选用数目n,精确控制通信链路,具体如下:

27.n=δt

pt’/δt

min

28.δt

pt’=mod(δt

pt

,t

ck

)

29.mod(x,y)——x除以y的余数;

30.δt

pt

——高速通信链路走线补偿延时δt

pt

;

31.t

ck

——高速通信链路串行数据周期;

32.δt

min

——组合逻辑最小延时单位,即延时精度。

33.所述δt

min

取值为0.1ns。

34.本发明与现有技术相比的优点和有益效果是:

35.1)准确性更高。现有设计方式中,约束参数的设定依据为红外凝视成像系统环境温度,而真正影响fpga芯片时序的参数为fpga结温。本发明根据相关材料、器件的导热系数、热阻等参数推算出fpga的芯片结温,作为延时计算的依据,同时采用多点采样温度和布局锁定的方式,能更加精确地控制延时;

36.2)无需重复设计调试,具备自适应调节能力。与通信链路相关的fpga片内资源区域确定后,用以实现精确控制通信链路延时的组合逻辑资源的选用功能均由fpga内部程序自动实现;

37.3)易于工程实现。本发明涉及的高速通信链路自适应高精度调整方法,仅需要对各温度传感器输出结果进行均值运算,将温度结果映射为延时长度后,再用线性乘除运算

得到实现延时的组合逻辑单元的数目,算法复杂度低且实时性高,易于工程实现。

附图说明

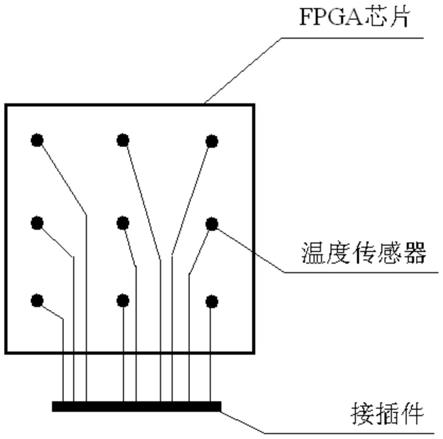

38.图1是温度传感器在fpga芯片表面分布示意图。

具体实施方式

39.以下将结合图1对本发明的基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法作进一步的详细描述。

40.先介绍红外凝视成像系统内部高速通信链路的通信机理:

41.红外凝视成像系统内部高速通信链路通常包含主节点和从节点,主从节点通常用fpga芯片实现,节点之间采用lvds协议进行互连通信,信号种类包括差分时钟信号和差分数据信号。时钟信号为单向信号,由主节点发送,数据信号为双向信号。主节点向从节点发送数据时,从节点依据从端口的时钟沿口采样并接收数据信号,从节点向主节点发送数据时,主节点依据主端口的时钟沿口采样并接收数据信号。

42.由于fpga内部连接线资源的硬件特性,在布局方式确定的情况下,随着温度的变化,时钟信号走线延时基本不变,数据信号的走线延时呈现与温度变化量线性相关的10ns以内的增加或减少。由于高速通信带宽为500m-1gbps,数据周期为1-2ns,因此,温度的变化可能导致无法满足主从节点接收寄存器的建立保持时间,造成通信异常。

43.fpga片内有数目众多的各种组合逻辑单元,不同种类组合逻辑单元的延时也不同。组合逻辑单元的延时精度不大于0.1ns,远小于数据周期。依据温度值,通过在主机或从机任何一端数据信号走线中引入相应种类和数目的组合逻辑单元,便可以实现高速通信链路时钟信号和数据信号之间相位的精确调整,保证通信的可靠性。

44.以调整主节点为例,基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法主要通过以下过程展开:

45.1)将多个小型化温度传感器(如热电偶)均匀分布在主节点fpga芯片表面,如图1所示;温度传感器用导热硅胶密闭包裹后与导热片粘连;在fpga芯片所在电路中添加位宽不小于8位的多通道ad转换芯片,转换芯片的模拟信号输入通道数目不小于温度传感器数目,温度传感器输出信号可通过飞线、接插件等形式连接至ad转换芯片的输入端,ad转换芯片数字量输出接口采用串行接口如spi,i2c等与fpga进行通信,以节省fpga管脚资源;

46.在fpga开发环境中使用功耗计算工具,计算当前fpga运行状态下的平均功耗,依据平均功耗w和fpga芯片内核-外壳的热阻参数θ,求得fpga芯片内核与外壳的温差δt,计算方式如下:

47.δt=w

·

θ

48.fpga采集ad转换芯片输入的各通道数字量,该数字量代表温度传感器测得的fpga芯片表面各点的温度值t1、t2……

tn,结合2)中计算结果,可以求得与各测试点对应的内核区域的结温为:

49.t

n’=δt+tn=tn+w

·

θ

50.2)将fpga芯片表面的温度传感器位置映射到fpga开发环境的资源使用监测界面中。在环境温度为指标要求最低温度t

min

、高速通信链路能够正常工作、且实现高速通信链

路的fpga片内资源布局锁定的前提下,观察数据发送寄存器和数据接收寄存器的布局点p

t

、pr与各温度传感器映射点的位置关系。假设p

t

和与其相邻的四个映射点的距离分别为d

t1

、d

t2

、d

t3

、d

t4

,那么pt处的结温t

pt’如下:

51.t

pt’=(d

t1

·

t1’

+d

t2

·

t2’

+d

t3

·

t3’

+d

t4

·

t4’

)/(d

t1

+d

t2

+d

t3

+d

t4

)

52.同理,pr点结温的计算方式类似;

53.用示波器测量全温t

min

~t

max

范围内数据信号相较于时钟信号的延时变化,测得延时变化为δt,得到当前温度条件下,输出寄存器与fpga芯片引脚之间的走线延时变化δt

pt

为:

54.δt

pt

=δt*(t

pt

’‑

t

min

)/(t

max-t

min

)

55.同理,输入寄存器与fpga芯片引脚之间的走线延时变化δt

pr

的计算方式类似;

56.3)如果任何温度下,δt

pt

和δt

pr

均为通信周期的n倍,那么在红外凝视成像系统指标要求的全温范围内,接收寄存器发送寄存器的建立保持时间均能够得到满足,高速通信均稳定可靠。因此,当δt

pt

和δt

pr

不为通信周期的整数倍时,通过添加指定长度的组合逻辑单元,便可以达到输出输入寄存器和fpga顶层管脚走线延时变化量为通信周期整数倍的要求,需要增加的延时如下式所示:

57.δt

pt’=mod(δt

pt

,t

ck

)

58.δt

pr’=mod(δt

pr

,t

ck

)

59.在fpga内设置总线切换模块,该模块输入端为发送寄存器输出端和接收寄存器输入端,输出端共计100个端口,各输出端口与输入端口延时范围为0.1ns~10ns,延时的增加采用组合逻辑单元的串联实现,由于fpga组合逻辑最小延时精度δt

min

为0.1ns,故该模块各输出端对应增加的组合逻辑单元数目为1~100个,依据δt

pt’和δt

pr’的输入,可计算得知需要插入的组合逻辑单元数目n,将输入端口信号切换至总线切换模块中增加n个组合逻辑单元的那一路输出端口,就实现了红外凝视成像高速通信链路延时的自适应调整。组合逻辑单元数目n的计算公式如下所示。

60.n=δt

pt’/δt

min

61.本发明提供的基于fpga的红外凝视成像系统高速通信链路自适应高精度调整方法应用于某红外凝视成像系统中,提升其内部lvds高速通信链路全温范围下的可靠通信的最高频率,提高数据流带宽,实现了640x512分辨率红外图像数据流在导引头内部的稳定传输,从而提高红外凝视成像系统的测量精度和数据更新率。

62.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1