正余弦编码器的解码装置和微控制单元的制作方法

1.本发明涉及编码器解码技术领域,特别涉及一种正余弦编码器的解码装置和一种微控制单元。

背景技术:

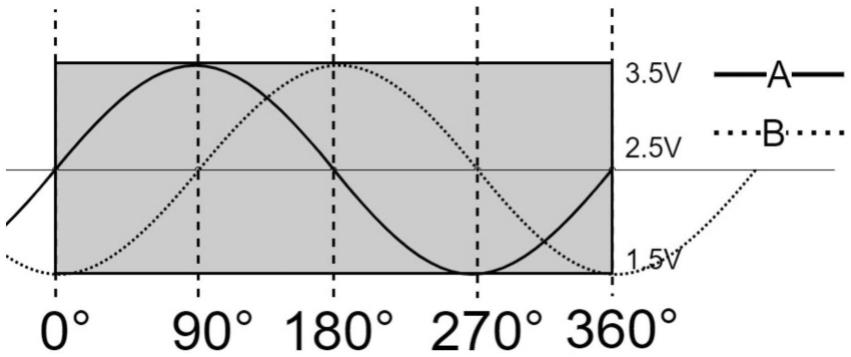

2.正余弦编码器是一种采用模拟输出的增量编码器,其输出为正余弦模拟信号。正余弦编码器与普通方波增量式编码器的ab正交脉冲信号类似,但与普通增量编码器的通断输出不同,正余弦编码器输出的是两路相位相差90

°

的正弦波。正余弦编码器输出波形如图1所示。

3.目前,正余弦编码器的解码方案一般包括以下两种:1、使用mcu(microcontroller unit,微控制单元)的adc(analog to digital converter,模数转换器)采集编码器的正余弦信号,通过软件查表的方式进行反正切运算,并进一步得到角度、速度、方向等数据。但是,存在采样率低、软件复杂、cpu负载过重等问题。2、使用adc采样芯片采集正余弦信号,通过spi(serial peripheral interface,串行外设接口)传输到fpga(field-programmable gate array,现场可编程门阵列),fpga进行解码再将数据传输给mcu。但是,存在价格昂贵、系统复杂、需要更多的开发维护人员等问题。

技术实现要素:

4.本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的目的在于提出一种正余弦编码器的解码装置和微控制单元,以实现在进行正余弦编码器的解码时,能够降低cpu负载、系统的复杂度和成本,同时提高采样率。

5.为达到上述目的,本发明第一方面实施例提出了一种正余弦编码器的解码装置,包括:模数转换器,用于对正余弦编码器输出的模拟正弦信号和模拟余弦信号进行模数转换,得到离散正弦信号和离散余弦信号;迟滞比较器,用于将所述模拟正弦信号与参考信号进行比较得到第一开关信号,并将所述模拟余弦信号与参考信号进行比较得到二开关信号;过零比较器,用于将所述正余弦编码器输出的参考标记信号与所述参考信号和进行比较,得到零位信号;坐标变换单元,与所述模数转换器和所述迟滞比较器分别连接,用于根据所述第一开关信号和所述第二开关信号,对所述离散正弦信号、所述离散余弦信号进行坐标变换,得到细分角度信号;正交解码单元,与所述迟滞比较器和所述过零比较器分别连接,用于对所述第一开关信号、所述第二开关信号和所述零位信号进行正交解码处理,得到方向信号和所述第一开关信号、所述第二开关信号的多倍频信号;脉冲个数计数单元,与所述正交解码单元连接,用于根据所述多倍频信号和所述方向信号进行脉冲个数计数,得到粗分位置信号;耦合计算单元,与所述坐标变换单元和所述脉冲个数计数单元分别连接,用于根据所述粗分位置信号和所述细分角度信号,得到细分位置信号。

6.本发明实施例的正余弦编码器的解码装置,能够降低cpu负载、系统的复杂度和成本,同时提高采样率。

7.另外,本发明实施例的正余弦编码器的解码装置还可以具有如下附加技术特征:

8.根据本发明的一个实施例,所述解码装置还包括:数模转换器,与所述迟滞比较器和所述过零比较器分别连接,用于生成所述参考信号。

9.根据本发明的一个实施例,所述解码装置还包括:滑动平均滤波单元,连接在所述模数转换器和所述坐标变换单元之间,用于对所述离散正弦信号和所述离散余弦信号进行滑动平均滤波处理。

10.根据本发明的一个实施例,所述解码装置还包括:故障检测单元,与所述模数转换器和所述迟滞比较器分别连接,用于对所述离散正弦信号和所述离散余弦信号的幅值和模值进行监测,并在所述幅值和模值超出相应的阈值时进行报错,以及对所述第一开关信号和所述第二开关信号的象限变化进行监测,并在变化异常时报错。

11.根据本发明的一个实施例,所述解码装置还包括:时钟单元,与所述脉冲个数计数单元连接,用于提供时基;其中,所述脉冲个数计数单元具体用于:利用所述时基根据所述多倍频信号和所述方向信号进行脉冲个数计数。

12.根据本发明的一个实施例,所述解码装置还包括:测速单元,与所述脉冲个数计数单元连接,用于采用m法根据计数得到的脉冲个数计算速度。

13.根据本发明的一个实施例,所述解码装置还包括:脉冲宽度捕获单元,与所述正交解码单元和所述时钟单元分别连接,用于利用所述时基根据所述多倍频信号、所述方向信号,得到脉冲时间宽度。

14.根据本发明的一个实施例,所述测速单元还与所述脉冲宽度捕获单元连接,还用于采用t法根据所述脉冲时间宽度计算速度。

15.根据本发明的一个实施例,所述解码装置还包括:差分放大器,与所述模数转换器连接,用于对所述模拟正弦信号和所述模拟余弦信号进行差分放大处理,并将处理后的所述模拟正弦信号和所述模拟余弦信号输出至所述模数转换器。

16.为达到上述目的,本发明第二方面实施例提出了一种微控制单元,包括上述的正余弦编码器的解码装置。

17.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

18.图1是正余弦编码器的输出波形示意图;

19.图2是本发明第一个实施例的正余弦编码器的解码装置的结构示意图;

20.图3是本发明实施例中第一开关信号和第二开关信号象限划分示意图;

21.图4是本发明第二个实施例的正余弦编码器的解码装置的结构示意图;

22.图5是本发明第三个实施例的正余弦编码器的解码装置的结构示意图;

23.图6是本发明第四个实施例的正余弦编码器的解码装置的结构示意图;

24.图7是本发明第五个实施例的正余弦编码器的解码装置的结构示意图;

25.图8是本发明第六个实施例的正余弦编码器的解码装置的结构示意图;

26.图9是本发明第七个实施例的正余弦编码器的解码装置的结构示意图;

27.图10是本发明第八个实施例的正余弦编码器的解码装置的结构示意图;

28.图11是本发明实施例的微控制单元的结构示意图。

具体实施方式

29.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

30.下面参考附图2-附图11描述本发明实施例的正余弦编码器的解码装置和微控制单元。图2是本发明实施例的正余弦编码器的解码装置的结构示意图。

31.如图2所示,正余弦编码器的解码装置,包括:模数转换器100、迟滞比较器101、过零比较器102、坐标变换单元103、正交解码单元104、脉冲个数计数单元105和耦合计算单元106。

32.其中,模数转换器100,用于对正余弦编码器输出的模拟正弦信号和模拟余弦信号进行模数转换,得到离散正弦信号和离散余弦信号;

33.迟滞比较器101,用于将所述模拟正弦信号与参考信号进行比较得到第一开关信号,并将所述模拟余弦信号与参考信号进行比较得到二开关信号。

34.具体地,如图3所示,根据第一开关信号a的电平和第二开关信号b的电平,将一个电周期划分为4个象限,每个象限对应90

°

区间。其中,一个电周期的4个跳边沿分别对应0

°

、90

°

、180

°

和270

°

。

35.过零比较器102,用于将所述正余弦编码器输出的参考标记信号与所述参考信号和进行比较,得到零位信号。

36.坐标变换单元103,与所述模数转换器100和所述迟滞比较器101分别连接,用于根据所述第一开关信号和所述第二开关信号,对所述离散正弦信号、所述离散余弦信号进行坐标变换,得到细分角度信号。

37.具体地,在所述第一开关信号和所述第二开关信号确定的象限内,根据所述第一开关信号和所述第二开关信号的跳边沿对所述离散正弦信号和离散余弦信号进行校准,并计算校准后的离散正弦信号和离散余弦信号的反正切值,得到细分角度信号。

38.正交解码单元104,与所述迟滞比较器101和所述过零比较器102分别连接,用于对所述第一开关信号、所述第二开关信号和所述零位信号进行正交解码处理,得到方向信号和所述第一开关信号、所述第二开关信号的多倍频信号。

39.具体地,多倍频信号可以是4倍频信号。

40.脉冲个数计数单元105,与所述正交解码单元104连接,用于根据所述多倍频信号和所述方向信号进行脉冲个数计数,得到粗分位置信号。

41.耦合计算单元106,与所述坐标变换单元103和所述脉冲个数计数单元105分别连接,用于根据所述粗分位置信号和所述细分角度信号,得到细分位置信号。

42.具体地,粗分位置每加1,相当于一个正余弦周期的90

°

。

43.根据本发明实施例的正余弦编码器的解码装置,能够降低cpu负载、系统的复杂度和成本,同时提高采样率。

44.在本发明的一个实施例中,如图4所示,所述解码装置还包括:数模转换器107,与所述迟滞比较器101和所述过零比较器102分别连接,用于生成所述参考信号。

45.在本发明的一个实施例中,如图5所示,所述解码装置还包括:滑动平均滤波单元108,连接在所述模数转换器100和所述坐标变换单元103之间,用于对所述离散正弦信号和所述离散余弦信号进行滑动平均滤波处理。

46.在本发明的一个实施例中,如图6所示,所述解码装置还包括:故障检测单元109,与所述模数转换器100和所述迟滞比较器101分别连接,用于对所述离散正弦信号和所述离散余弦信号的幅值和模值进行监测,并在所述幅值和模值超出相应的阈值时进行报错,以及对所述第一开关信号和所述第二开关信号的象限变化进行监测,并在变化异常时报错。

47.具体地,例如象限变化从象限1跳变到象限3时,进行报错。

48.在本发明的一个实施例中,如图7所示,所述解码装置还包括:时钟单元110,与所述脉冲个数计数单元105连接,用于提供时基;其中,所述脉冲个数计数单元105具体用于:利用所述时基根据所述多倍频信号和所述方向信号进行脉冲个数计数。

49.在本发明的一个实施例中,如图8所示,所述解码装置还包括:测速单元111,与所述脉冲个数计数单元105连接,用于采用m法根据计数得到的脉冲个数计算速度。

50.在本发明的一个实施例中,如图9所示,所述解码装置还包括:脉冲宽度捕获单元112,与所述正交解码单元104和所述时钟单元110分别连接,用于利用所述时基根据所述多倍频信号、所述方向信号,得到脉冲时间宽度。

51.具体地,所述测速单元111还与所述脉冲宽度捕获单元112连接,还用于采用t法根据所述脉冲时间宽度计算速度。

52.在本发明的一个实施例中,如图10所示,所述解码装置还包括:差分放大器113,与所述模数转换器100连接,用于对所述模拟正弦信号和所述模拟余弦信号进行差分放大处理,并将处理后的所述模拟正弦信号和所述模拟余弦信号输出至所述模数转换器100。

53.本发明实施例的正余弦编码器的解码装置,通过硬件实现正余弦编码器的解码,可降低系统的复杂度和成本,提高采样率和降低cpu负载,以及可以直接读取角度数据,方向数据,并通过m法和t法计算速度。

54.对应上述实施例,本发明还提出一种微控制单元。

55.图11是本发明的微控制单元的结构框图。

56.如图11所示,微控制单元10包括上述的正余弦编码器的解码装置1000,即正余弦编码器的解码装置1000集成在微控制单元10中。

57.该微控制单元,通过集成上述的正余弦编码器的解码装置,能够降低cpu负载、系统的复杂度和成本,同时提高采样率。

58.应当理解,本发明的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

59.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不

一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

60.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

61.在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

62.尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1