一种差分鬼成像重构方法、系统及电子设备

1.本发明涉及图像重构技术领域,特别是涉及一种差分鬼成像重构方法、系统及电子设备。

背景技术:

2.鬼成像又称双光子成像或关联成像,是一种利用双光子复合探测恢复待测物体空间信息的一种新型成像技术。传统的光学观察是基于光场的强度的分布测量,鬼成像则基于光场的强度的关联测量,并且现有的成像技术主要利用光场的一阶关联信息(强度与位相)。工程环境通常会存在雾霾,沙尘等各种恶劣条件的影响,而鬼成像具有抗干扰性强优势,一定程度上可以抵抗大气湍流和散射介质的干扰。工程应用中不可避免的会遇到弱光场成像的问题,而鬼成像配合单光子探测器具有高灵敏性的优势,可以在弱光条件下依旧完成图像重构工作。

3.基于以上优势,鬼成像已经可以在许多复杂环境中完成对于二维目标物体的成像,但是鬼成像采用传统二阶关联算法需要经过多达500次的采样才能恢复出一个32*32分辨率的目标物体大致形貌,重建图像过程不仅耗时严重,无法做到实时成像以及高分辨率成像,而且还需要耗费巨大的内存空间,针对上述问题,基于fpga的鬼成像图象重构方法逐渐成为鬼成像领域研究热点。

4.目前制约鬼成像实时重建工作的主要有两个因素:一是个人计算机无法进行并行运算,对于大矩阵的复杂运算既耗费大量时间又占用了极大的内存资源,甚至内存容量较小的计算机无法完成256*256的鬼成像图像重建。二是采用fpga板卡,只通过verilog语言设计迫使研发人员陷入构建复杂电路过程,研发周期较长,同时开发出的fpga电路无法准确指明单次采样重建工作所耗费时间以及资源。

技术实现要素:

5.本发明的目的是提供一种差分鬼成像重构方法、系统及电子设备,基于高层次综合工具构建集成有鬼成像算法的知识产权核,能够提高鬼成像重构算法的运行速度并降低执行鬼成像重构的硬件要求。

6.为实现上述目的,本发明提供了如下方案:

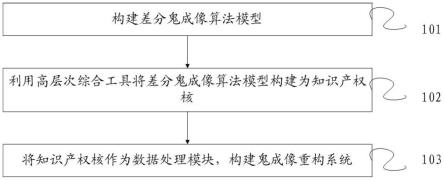

7.一种差分鬼成像重构方法,包括:

8.构建差分鬼成像算法模型;

9.利用高层次综合工具将所述差分鬼成像算法模型构建为知识产权核;

10.将所述知识产权核作为数据处理模块,构建鬼成像重构系统;所述数据处理模块的输入量为待测物体的光强测量值和光场调制矩阵;所述数据处理模块的输出量为待测物体的重构图像。

11.可选的,所述光强测量值是通过鬼成像重构系统的测量模块获取的;

12.所述测量模块包括:激光器、毛玻璃、分束器、透镜、信号光路探测器、和参考光路

探测器;

13.所述毛玻璃设置于所述激光器的输出光路上;

14.所述分束器设置于所述毛玻璃的输出光路上;

15.所述透镜设置于所述分束器的透射输出光路上;

16.所述参考光路探测器设置于所述透镜的输出光路上;所述参考光路探测器用于获取待测物体的参考光强;

17.所述待测物体设置于所述分束器的反射输出光路上;

18.所述信号光路探测器设置于所述物体的反射输出光路上;所述信号光路探测器用于获取待测物体的信号光强。

19.可选的,所述差分鬼成像算法模型为:g

dgi

=《b1i2(x2)》-《b2i2(x2)》《b1》/《b2》;

20.其中,g

dgi

表示差分鬼成像重构的结果;b1表示信号光强;b1=∫∫i1(x1)t(x)d2x1;i1(x1)表示空间内x1处光强;t(x)表示目标物体的反射率函数;i2(x2)表示空间内x2处光强;b2表示参考光强;b2=∫∫i2(x2)d2x2;《*》表示平均值;

21.一种差分鬼成像重构系统,包括:

22.模型构建模块,用于构建差分鬼成像算法模型;

23.知识产权核构建模块,用于利用高层次综合工具将所述差分鬼成像算法模型构建为知识产权核;

24.鬼成像重构系统构建模块,用于将所述知识产权核作为数据处理模块,构建鬼成像重构系统;所述数据处理模块的输入量为待测物体的光强测量值和光场调制矩阵;所述数据处理模块的输出量为待测物体的重构图像。

25.一种电子设备,包括存储器及处理器,所述存储器用于存储计算机程序,所述处理器运行所述计算机程序以使所述电子设备执行所述的一种差分鬼成像重构方法。

26.可选的,所述存储器为可读存储介质。

27.根据本发明提供的具体实施例,本发明公开了以下技术效果:

28.本发明提供了一种差分鬼成像重构方法、系统及电子设备,涉及图像重构技术领域,方法包括构建差分鬼成像算法模型;利用高层次综合工具将差分鬼成像算法模型构建为知识产权核;将知识产权核作为数据处理模块,构建鬼成像重构系统;数据处理模块的输入量为待测物体的光强测量值和光场调制矩阵;数据处理模块的输出量为待测物体的重构图像。本发明基于高层次综合工具构建集成有鬼成像算法的知识产权核,能够提高鬼成像重构算法的运行速度并降低执行鬼成像重构的硬件要求。

附图说明

29.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

30.图1为本发明实施例1中一种差分鬼成像重构方法流程图;

31.图2为本发明实施例1中鬼成像重构系统结构图;

表示参考光强;b2=∫∫i2(x2)d2x2;《*》表示平均值;《b1》表示信号光强多次测量结果的平均值;《b2》表示参考光强多次测量结果的平均值。

50.图2表明迭代差分鬼成像算法流程,在数值仿真中有下式成立:

51.i1(x1)=i2(x2)

52.为了提升成像质量,采用哈达玛(hadamard)散斑取代随机二值散斑作为光场强度i1(x1),投影到目标物体。哈达玛矩阵是由+1和-1元素构成的且满足hn*h

nt

=ni(这里h

nt

为n阶矩阵hn的转置,ni为n阶单位方阵),在数值仿真中-1不具有实际意义,将哈达玛矩阵中-1全部替换为0生成哈达玛散斑投射到目标物体上,也将此哈达玛散斑作为输入存入到sd卡中,以重构32*32图像大小为例,sd卡以字符类型需存储1024阶哈达玛散斑,若需要重构出更高分辨率图像,可选择更高阶哈达玛矩阵。

53.步骤102:利用高层次综合工具将差分鬼成像算法模型构建为知识产权核。

54.根据idgi算法模型确定输入以及输出,将哈达玛散斑以及哈达玛散斑与物体作用后的总光强值(简称测量值)作为输入,利用鬼成像方式重构出的图像作为输出。采用c++编程实现,定义哈达玛散斑数据类型为整型(int),测量值数据类型为双精度浮点型(double),结果输出为双精度浮点型(double)。

55.由于idgi算法采用迭代方式重构图像,算法迭代过程中没有转移指令,共享资源冲突,中断请求,故可采用流水线技术进行硬件加速,在计算机体系结构中流水线技术是指将规模较大,层次较多的组合电路分解为多级结构,在每一级中添加寄存器用来暂存中间数据,将上一级的输出作为下一级的输入而此过程又无反馈电路,此技术提高了电路的吞吐率以及工作频率实现了硬件加速功能。

56.高层次综合设计过程首先确定系统芯片工作时钟频率为100mhz,并采用赛灵思(xilinx)的xc7z020芯片型号。将idgi算法添加项目的源文件(source)中,并编写测试程序添加到项目测试文件(testbench)中,测试程序的作用是用来验证高级语言编写的idgi算法正确性,验证方式是利用哈达玛散斑以及真实测量值作为输入,测试程序调用idgi算法模块计算输出结果与目标图像的均方根误差,结构相似度等指标符合要求即可。

57.在高层次综合设计过程中,经过c仿真(c simulation)即可完成上一步骤中的验证工作,然后在源文件中idgi算法的循环语句中添加#pragma hls pipeline(流水线)语句。

58.根据输入输出数据类型以及模块连接方式确定接口封装类型(#pragma hls interface),哈达玛矩阵作为矩阵类型的输入可以绑定为bram接口,此接口可连接zynq的pl端的存储ram单元,通过此方式完成ps端与pl端数据交换功能,相比于sd卡数据传输,它可以加速数据访问完成实时数据传输,同样将idgi算法的重构结果输出接口绑定为bram,两者数据深度均为1024,若后续需要更高分辨率的图象重构结果,可增加存储深度,idgi算法的测量值输入并非矩阵类型,仅为单一数值,故将其端口绑定为advanced extensible interface lite(axi4-lite)接口,此端口实现成本低,无需突发传输模式,ps端与pl端通过axi4-lite接口每次只传输一次数据,满足idgi算法输入要求,同时也将idgi算法模块的控制返回功能绑定为axi4-lite接口,每次ps端可通过axi4-lite总线发送算法启动指令控制pl端idgi算法启动,也可以通过axi4-lite总线协议读取pl端idgi算法模块是否完成运

算的状态判断下一步的操作。可根据其他模块连接方式将上述输入输出也可绑定为其他类型接口,实现接口灵活配置。

59.然后完成c综合(c synthesis)获得idgi算法模块完成一次运算所需的总耗时情况以及占用fpga资源情况,根据可视化的综合结果可对算法进一步优化,平衡资源占用与耗时情况。最终导出生成知识产权核(ip核),在集成电路设计中ip核是指形式为逻辑单元,芯片设计的可重用模组,对外显示接口类型,对内实现功能运算,经过上述步骤的设计验证后,设计人员以ip核为基础进行设计开发,可以缩短设计所需周期。

60.对于知识产权核,一个散斑对应一个探测器数值;一次可成像但是根本不清晰,需要多组数据,每次都可逐渐获得更加清晰的图片,简单来说:一次测量出一次图,逐渐变得更加清晰,测量足够多,重构效果就会很好,知识产权核输出的重构图像与拍摄图像的均方根误差在预设均方根误差范围内。

61.步骤103:将知识产权核作为数据处理模块,构建鬼成像重构系统;数据处理模块的输入量为待测物体的光强测量值和光场调制矩阵;数据处理模块的输出量为待测物体的重构图像。光场调制矩阵可为哈达玛矩阵;光强测量值是通过鬼成像重构系统的测量模块获取的。

62.如图2所示,测量模块包括:激光器、毛玻璃、分束器、透镜、信号光路探测器、和参考光路探测器;毛玻璃设置于激光器的输出光路上;分束器设置于毛玻璃的输出光路上;透镜设置于分束器的透射输出光路上;参考光路探测器设置于透镜的输出光路上;参考光路探测器用于获取待测物体的参考光强;待测物体设置于分束器的反射输出光路上;信号光路探测器设置于物体的反射输出光路上;信号光路探测器用于获取待测物体的信号光强。

63.构建应用于数据处理模块的鬼成像重构系统:

64.1.采用基于ip核设计开发模式,创建block design(模块设计方式),添加zynq7 proccessing system ip核(zynq7000系列处理器ip核),打开ip核配置页面,使能m_axi_gp0 interface(通用目的axi主端口)完成ps端与pl端数据交互功能。使能sd外设接口完成ps端从sd卡读取哈达玛散斑功能。使能uart外设端口完成打印调试信息功能。设置pl端时钟频率为100mhz。设置ddr类型为ddr3,总线位宽为32位,突发传输长度为8,工作频率为533.333333mhz,其他选择默认设置。

65.2.添加idgi算法ip核,此ip核无需配置。idgi算法模块作为核心通过与bram接口以及axi_lite接口嵌入整个系统中,一个bram端口是32位数据位宽,另一个是64位数据位宽。

66.3.添加block memory generatorip核(块存储器模块),配置为bram controller模式,设置存储类型为true dual port ram(真双口ram),其他选择默认设置,此模块对外显示两个bram接口,其中一个接口与idgi算法ip核的bram接口连接,另一个bram接口通过axi bram controller ip核(通过axi总线访问bram接口内容,配置32位数据位宽)与ps端相连,同理再添加一个block memory generator ip核和axi bram controller ip核(配置64位数据位宽)与idgi另一个bram端口相连。

67.4.添加axi互联ip(axi interconnect)ip核用于连接axi存储器映射(memory-mapped)的主器件和从器件。主器件是ps端处理器,通过m_axi_gp0 interface端口相连,从器件是两个axi bram controller ip核和idgi算法ip核,均通过axi总线相连。

68.5.最后完成rtl综合以及rtl实现步骤生成比特流文件,该文件中包含了可编程逻辑器件(fpga)的详细硬件信息,为后续嵌入式开发提供基础。

69.基于zynq的fpga板卡是由两个部分组成的:一个由双核arm cortex-a9为核心构成的处理器系统(ps,processing system),和一个等价于fpga的可编程逻辑(pl,programmable logic)部分组成。zynq架构实现了工业标准的axi接口,在芯片的两个部分实现了高带宽,低延迟的连接。在上述装置结构图中,基于axi4总线协议,ps端通过axi通用接口(m_axi_gp)与pl端axi互联ip核(axi_interconnect)进行数据控制信息的交互。详细系统设计如下所示:

70.在ps端需要对ddr3_memory_controller,uart,sd模块配置。

71.memory(内存)指的是硬件电路板上的双倍速率同步动态随机存储器(ddr),使用的是h5tq4g63ffr-rd芯片,作为cpu能够直接寻址的存储空间,其作用是为程序运行提供空间,存储临时变量等。

72.ddr3_memory_controller指的是ddr的内存控制器,其作用是设置内存种类为ddr3,设置总线传输带宽为32bit,设置是否对数据进行校验,设置ddr工作频率,设置突发传输长度等。

73.rs-232串口通信作为uart的物理层面实现,硬件上以usb接口形式与上位机相连,其硬件底层包含cp2102芯片完成usb与uart的转换功能,配合txs0102dctr芯片完成硬件层面的数据传输功能。此串口主要用于sdk嵌入式开发中的查阅调试信息,后期可去除。

74.tf卡是用来作为替代ddr存储大容量数据的物理介质,在本次设计中其主要存储大量的哈达玛矩阵信息,其硬件采用txs02612rtwr芯片实现,在实测中其读入速率约为1.3mb/s。

75.mio(multiplexing io)是ps端可复用的io管脚资源,类似于rs-232与tf卡都需要接入ps端mio部分,该硬件即为ps端bank501。在mio配置中勾选uart与sd,就可以将fpga板卡外部的rs-232与tf卡分别与ps端uart以及sd接口相连接,也就是物理层连接。

76.uart作为ps端外设资源的一部分,其作用是将数据转换为uart协议进而发送到cpu中,cpu也可以通过uart访问外部rs-232的缓冲数据。

77.sd也是ps端外设资源,其作用与uart类似,完成cpu与外部tf卡数据交互。

78.arm-cortex-a9是指zynq的ps端所采用的处理器型号,该型号可运行多任务的操作系统,也是sdk嵌入式开发设计的核心。

79.在装置结构图pl部分:

80.axi-interconnect作为一个具有多个主机与从机端口的axi组件,主要作用是作为中间结点连接各个axi接口的组件,本次设计的bram-controller就是通过axi4总线与之相联,idgi算法模块是通过axi4-lite总线与之相联。

81.blockmemory generatorip核是一种存储类的ip核,将其配置为bram模式,此设计中有两个模块。其中一个ip核主要作用是存储从sd卡读出的哈达玛矩阵信息,另外一个是存储idgi算法重构结果。设置存储哈达玛矩阵的bram模块读写位宽是32位,该模块消耗了fpga中8个36k rams资源,为了提高重构结果的精度,设置存储idgi算法重构结果的bram模块读写位宽为64位,此部分消耗16个36k brams资源,合计24个36k brams资源。

82.bram-controller ip核是为了方便的与本地的block memory generator模块进

行通信而设计的ip核,其bram端接口连接本地block memory generator模块,另一端axi4接口与axi-interconnect连接,其作用方便ps端通过axi总线对pl端bram数据交互。

83.idgi算法ip核是通过hls设计产生的,它是pl端的核心模块,内部是利用哈达玛散斑与测量值,基于迭代差分鬼成像的算法重构目标图像,该图像是以矩阵的形式存储在bram中。通过hls将其数据接口全部封装为bram接口与本地blockmemory generator模块进行数据交互,将控制端口封装为axi-lite接口,与axi-interconnect连接,直接由ps端控制该ip核是否启动,并实时监控其运行状态。

84.综上所述,ps端负责资源调用以及外设配置,pl端负责运算以及其他辅助数据协议转换,两者之间通过axi总线进行数据交互,这样的设计既实现了对算法重构的硬件加速,也减少了cpu对数据处理的负担。

85.本发明利用高层次综合工具设计出idgi算法模块(知识产权核或ip核),并将该模块成功嵌入到鬼成像图象重构系统中,实现快速实时的鬼成像图像重建工作,并大幅缩短产品系统的开发周期。具体实现方式是通过高层次综合工具设计idgi算法ip核,并在pl端构建idgi算法的门级电路,在ps端通过axi总线对idgi算法模块进行控制(状态监测),通过axi总线借助bram-controller模块对idgi算法模块进行数据访问:建立迭代鬼成像算法模型,该模型中,将哈达玛散斑信息作为输入,将鬼成像方式重构出的图像作为输出;利用高层次综合工具将上述算法模型设计成idgi算法模块,形成知识产权核(ip核);基于上述知识产权核(ip核)设计zynq鬼成像重构系统,将上述知识产权核(ip核)嵌入到鬼成像重构系统中;采集哈达玛散斑信息,存储进上述zynq鬼成像重构系统中的sd卡内;挂载sd卡,打开已在sd卡中存储哈达玛散斑信息的文件,并重置读取指针的偏移量为0,完成数据类型的转换;配置并初始化知识产权核(ip核),启动知识产权核(ip核),输入哈达玛散斑信息,等待并检查知识产权核(ip核)是否完成运算,完成一次运算后,输出重构出的图像;将输出的图像写入上述zynq鬼成像重构系统的bram中并通过uart串口打印调试信息,或将结果写入sd卡中,最后由上位机对重构结果的质量进行评估。

86.实施例2

87.为了执行上述实施例一对应的方法,以实现相应的功能和技术效果,下面提供了一种差分鬼成像重构系统,包括:

88.模型构建模块,用于构建差分鬼成像算法模型。

89.知识产权核构建模块,用于利用高层次综合工具将所述差分鬼成像算法模型构建为知识产权核。

90.鬼成像重构系统构建模块,用于将所述知识产权核作为数据处理模块,构建鬼成像重构系统;所述数据处理模块的输入量为待测物体的光强测量值和光场调制矩阵;所述数据处理模块的输出量为待测物体的重构图像。

91.实施例3

92.本实施例提供了一种电子设备,包括存储器及处理器,存储器用于存储计算机程序,处理器运行计算机程序以使电子设备执行实施例1所述的一种差分鬼成像重构方法。其中,存储器为可读存储介质。

93.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统

而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

94.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1