使用CXL测试器件以增加并行性的系统和方法与流程

本发明的实施例总体涉及器件测试的领域。更具体而言,本发明的实施例涉及用于使用计算快速链路(compute express link,cxl)对被测器件(device under test,dut)进行测试的方法和系统。

背景技术:

1、通常对被测器件(或被测设备)进行测试,以在出售器件之前确定该器件的性能和一致性。例如,可以使用各种各样的测试用例来测试dut,并且可以将测试用例的结果与预期的输出结果进行比较。当测试用例的结果与令人满意的值或值的范围不匹配时,该器件可以被认为是故障器件或具有异常值,并且可以基于性能等对该器件进行分类。

2、dut通常由自动或自动化测试设备(ate)测试,该ate设备可用于使用软件和自动化进行复杂的测试,以提高测试效率。dut可以是旨在集成到最终产品(例如计算机、网络接口或固态驱动器(ssd))中的任何类型的半导体器件、晶片或组件。通过在制造时使用ate去除有缺陷或不满意的芯片,可以显著提高产量的质量。

3、计算快速链接(compute express link)是为高性能数据中心计算机设计的高速cpu到器件和cpu到存储器的连接的开放标准。cxl建立在快速pci(pci express)的物理和电气接口上,并且包括基于pcie的块输入/输出协议和新的缓存一致性协议以用于访问系统存储器和器件存储器。最近,对cxl 2.0中的cxl总线协议进行了改进,允许并行使用16个总线通道(pcie总线通道)测试不同宽度的器件。然而,最多支持cxl 1.1的现有处理器无法使用现有方法在多端口测试中利用这一改进,并且通常局限于并行使用16个通道测试器件,这限制了测试的并行性和效率。

技术实现思路

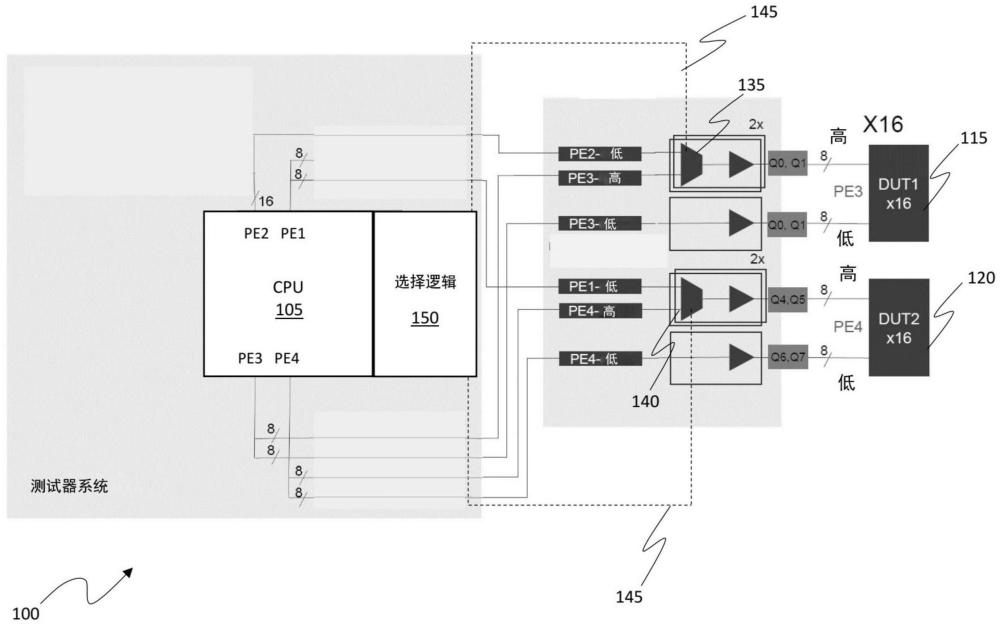

1、因此,需要一种使用cxl 1.1对器件进行测试的方法,该方法可以利用改进的cxl总线协议下可用的所有16个通道进行并行测试。本发明的实施例可以选择性地启用这样的配置,即在测试期间使用位于cpu和dut之间的扩展板的多路复用器,允许并行地对一个dut进行16通道测试(x16),或者并行地对两个dut进行8通道测试(x8)。通过这种方式,与只能使用cxl 1.1cpu的16个通道对器件进行测试的现有方法相比,并行性和测试效率得到了显著提高。

2、根据一个实施例,公开了一种用于对处理器总线进行分叉的电路。该电路包括:多个输入端口,用于耦合到来自处理器的四个n位总线,其中,四个总线中的每一个包括n位,并且分别包括下半部分和上半部分;多个输出端口,用于提供四个总线,其中,来自多个输出端口的四个总线中的每一个包括n/2位;以及耦合到多个输入端口并耦合到多个输出端口的多路复用电路,该多路复用电路响应于公共选择线,以用于选择性地实现两种配置之一,这两种配置包括:第一配置,第一配置将多个输出端口仅耦合到来自处理器的四个总线的下半部分;以及第二配置,第二配置将多个输出端口耦合到来自处理器的四个总线中的至少两个总线的下半部分和上半部分。

3、根据一些实施例,多路复用电路包括多个高速多路复用器,每个高速多路复用器耦合到公共选择线。

4、根据一些实施例,所述多个高速多路复用器包括两个多路复用器。

5、根据一些实施例,n是16。

6、根据一些实施例,第一配置可操作以将处理器耦合到四个被测器件(dut),四个dut中的每一个包括n/2位宽的总线。在这个示例中,n=16。

7、根据一些实施例,第二配置可操作以将处理器耦合到两个dut,这两个dut中的每一个包括n位宽的总线。在这个示例中,n=16。

8、根据一些实施例,第一配置和第二配置可操作以基于选择线的值进行动态配置。

9、根据不同的实施例,公开了一种用于测试被测器件(dut)的测试器电路。该测试器电路包括:处理器,该处理器具有四个n位总线;多个输入端口,多个输入端口耦合到处理器的四个n位总线,其中,四个n位总线中的每一个包括下半部分和上半部分;多个输出端口,用于提供四个n/2位总线;以及高速多路复用电路,高速多路复用电路耦合到多个输入端口并耦合到多个输出端口,高速多路复用电路响应于公共选择线,以用于选择性地实现两种配置之一,这两种配置包括:第一配置,第一配置将多个输出端口仅耦合到来自处理器的四个n位总线的下半部分;以及第二配置,第二配置将多个输出端口耦合到来自处理器的四个n位总线中的至少两个n位总线的下半部分和上半部分。

10、根据一些实施例,高速多路复用电路包括多个高速多路复用器,每个高速多路复用器耦合到公共选择线。

11、根据一些实施例,n是16。

12、根据一些实施例,第一配置可操作以将处理器耦合到四个dut以对其进行测试,四个dut中的每一个包括n/2位宽的总线。

13、根据一些实施例,第二配置可操作以将处理器耦合到两个器件dut以对其进行测试,这两个dut中的每一个包括n位宽的总线。

14、根据一些实施例,第一配置和第二配置可操作以进行动态配置。

15、根据另一实施例,公开了一种对处理器的总线进行分叉以进行测试的方法。该方法包括:处理器通过至少四个n位总线生成信号;在第一操作模式中,多路复用器电路耦合到处理器的至少四个n位总线,并且设置在处理器的外部,通过四个n/2位输出总线生成信号。在第一操作模式中,处理器用四个n/2位输出总线同时测试四个被测器件(dut)。在第二操作模式中,多路复用器电路通过两个n位输出总线生成信号,并且处理器用这两个n位输出总线同时测试两个dut。该方法还包括:通过切换耦合到多路复用电路的选择线的值,在第一操作模式和第二操作模式之间切换。

16、根据一些实施例,多路复用器电路包括公共耦合到选择线的高速多路复用器。

17、根据一些实施例,高速多路复用器包括两个多路复用器。

18、根据一些实施例,n=16。

19、根据一些实施例,第一操作模式仅通过四个n/2位输出总线从处理器提供4个n位总线的下半部分。

20、根据一些实施例,第二操作模式通过两个n位输出总线从处理器提供4个n位总线中的两个。

21、根据一些实施例,第二操作模式通过两个n位输出总线从处理器提供4个n位总线中的两个。

技术特征:

1.一种用于对处理器的总线通道进行分叉的电路,所述电路包括:

2.根据权利要求1所述的电路,其中,所述多路复用电路包括多个高速多路复用器,每个高速多路复用器耦合到所述公共选择线。

3.根据权利要求2所述的电路,其中,所述多个高速多路复用器包括两个多路复用器。

4.根据权利要求1所述的电路,其中,n是16。

5.根据权利要求1所述的电路,其中,所述第一配置可操作以将所述处理器耦合到四个被测器件(dut),所述四个dut中的每一个dut包括n/2位宽的总线。

6.根据权利要求5所述的电路,其中,所述第二配置可操作以将所述处理器耦合到两个dut,所述两个dut中的每一个dut包括n位宽的总线。

7.根据权利要求6所述的电路,其中,所述第一配置和所述第二配置可操作以基于所述选择线的值进行动态配置。

8.一种用于测试被测器件(dut)的测试器电路,所述测试器电路包括:

9.根据权利要求8所述的测试器电路,其中,所述多路复用电路包括多个高速多路复用器,每个高速多路复用器耦合到所述公共选择线。

10.根据权利要求8所述的测试器电路,其中,n是16。

11.根据权利要求8所述的测试器电路,其中,所述第一配置可操作以将所述处理器耦合到四个dut以对其进行测试,所述四个dut中的每一个dut包括n/2位宽的总线。

12.根据权利要求11所述的测试器电路,其中,所述第二配置可操作以将所述处理器耦合到两个器件dut以对其进行测试,所述两个dut中的每一个dut包括n位宽的总线。

13.根据权利要求8所述的电路,其中,所述第一配置和所述第二配置可操作以进行动态配置。

14.一种对处理器的总线进行分叉以进行测试的方法,所述方法包括:

15.根据权利要求14所述的方法,其中,所述多路复用器电路包括公共耦合到所述选择线的高速多路复用器。

16.根据权利要求15所述的方法,其中,所述高速多路复用器包括两个多路复用器。

17.根据权利要求14所述的方法,其中,n=16。

18.根据权利要求14所述的方法,其中,所述第一操作模式仅通过所述四个n/2位输出总线从所述处理器提供所述4个n位总线的下半部分。

19.根据权利要求14所述的方法,其中,所述第二操作模式通过所述两个n位输出总线从所述处理器提供所述4个n位总线中的两个n位总线。

20.根据权利要求18所述的方法,其中,所述第二操作模式通过所述两个n位输出总线从所述处理器提供所述4个n位总线中的两个n位总线。

技术总结

本申请公开了使用CXL测试器件以增加并行性的系统和方法。本发明的实施例可以在测试期间使用设置在CXL1.1CPU和DUT之间的多路复用器电路选择性地启用16通道(x16)或8通道(x8)对器件的测试。与只能使用CXL 1.1CPU的8通道对器件进行测试的现有方法相比,通过这种方式,并行性和测试效率得到了显著提高。

技术研发人员:埃德蒙多·德·拉·普恩特

受保护的技术使用者:爱德万测试公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!