芯片引脚短路的检测方法及设备与流程

本发明涉及集成电路领域,尤其涉及芯片引脚短路的检测方法。

背景技术:

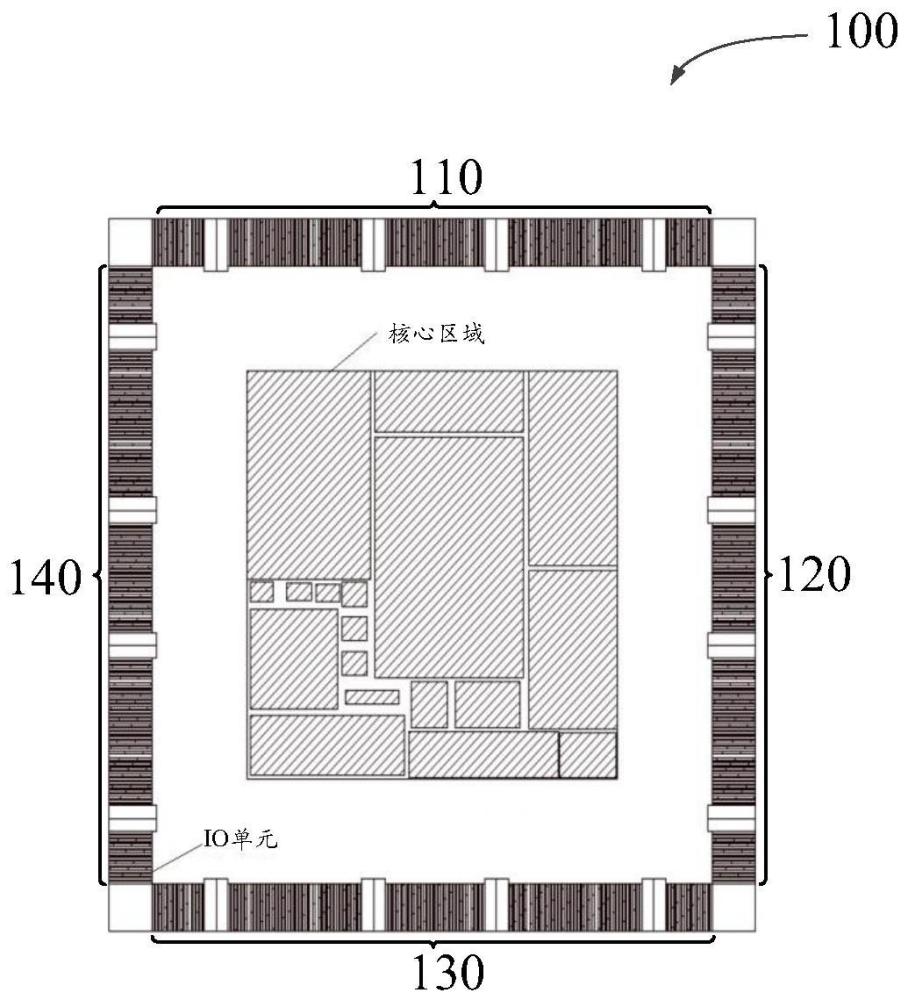

1、图1展示了现有技术提供的一种芯片100的示意图。

2、作为举例,如图1所示,芯片100包括核心区域(“core area”)以及位于core area外围的io单元(“i/o cell”)。在芯片设计过程中,芯片的核心区域的面积、io单元的数量以及每个io单元的尺寸都是固定的。随着集成电路集成度的提升芯片的io单元也越来越多,如芯片周围排满了成百上千的io单元。在芯片中io单元位于core area的外围并且布置成一圈的形式,如对于core area的每条边仅布置成与该边平行的一排。如图1中所示,对应第一条边布置一排io单元110,对应第二条边布置一排io单元120,对应第三条边布置一排io单元130以及对应第四条边布置一排io单元140。

3、图2展示了现有技术提供的芯片的io单元对应的简化电路结构示意图。

4、作为举例,如图2所示,io单元包括两个二级管(diode1和diode2)、三个mos管(mp0、mn0、mn1)、rc定时器电路(rc timer)以及电阻(r)。vdd表示电源;vss表示接地;io表示io端口(输入输出端口)。从io端口输入的电流会通过二级管diode1或者diode2传输。

技术实现思路

1、随着半导体技术的高速发展,半导体集成电路的系统集成度越来越高,功能越来越多,由于功能的增加从而需要在芯片上增加引脚。引脚的增加造成芯片在生产封装等过程中无可避免出现一定比率的信号短路,特别是封装基板的短路是难以避免的。而引脚之间的短路现象会造成产品dppm(defect part per million每百万颗芯片中的不良品数)过高,进而造成芯片产品后续的返修率过高从而导致芯片无法量产。

2、对于引脚较多的芯片,要检测其中任何两个引脚之间是否存在短路是复杂且耗时的。例如,芯片上有1000个引脚,检测包括=499500种引脚的两两组合的情况。在检测过程中要完成种组合的短路检测是极其耗时的。另外,也可以通过购买专用的检测治具来检测,而通过专用的检测治具又引入高昂的成本。

3、本发明希望能降低引脚较多芯片的引脚短路检测的成本与复杂度基础上,能够快速有效识别众芯片中多引脚中可能存在的任何短路现象。

4、根据本发明的第一方面,提供了根据本发明第一方面的第一芯片引脚短路的检测方法,所述芯片包括n个待测试引脚,包括:将芯片上除被测引脚之外的其他引脚均接地;向芯片中所述被测引脚施加测量电流,检测所述被测引脚的电压;根据所述电压确定所述被测引脚短路情况。

5、根据本发明的第一方面的第一芯片引脚短路的检测方法,提供了根据本发明第一方面的第二芯片引脚短路的检测方法,所述测量电流包括正向电流和/或负向电流。

6、根据本发明的第一方面的第二芯片引脚短路的检测方法,提供了根据本发明第一方面的第三芯片引脚短路的检测方法,在所述测量电流为正向电流情况下,检测所述被测引脚是否存在正向电压;若所述被测引脚存在正向电压,则所述被测引脚未短路。

7、根据本发明的第一方面的第二或第三芯片引脚短路的检测方法,提供了根据本发明第一方面的第四芯片引脚短路的检测方法,其中,在所述测量电流为负向电流情况下,检测所述被测引脚是否存在负向电压;若所述被测引脚存在负向电压,则所述被测引脚未短路。

8、根据本发明的第一方面的第一至第四任一项芯片引脚短路的检测方法,提供了根据本发明第一方面的第五芯片引脚短路的检测方法,逐个向芯片中各个引脚依次施加测量电流,检测得到各个引脚的电压;根据各个引脚对应的电压确定出各个引脚短路情况;其中,每次检测一个引脚,每次检测的引脚作为该次的被测引脚,每次检测向其对应的被测引脚一个施加测量电流;对每个引脚进行检测时,除被测引脚之外,芯片上其他引脚均接地。

9、根据本发明的第一方面的第五芯片引脚短路的检测方法,提供了根据本发明第一方面的第六芯片引脚短路的检测方法,向芯片中第一引脚施加第一测量电流,检测得到所述第一引脚对应的第一电压;根据第一电压确定出第一引脚的短路情况;又向芯片中第二引脚施加第二测量电流,检测得到所述第二引脚对应的第二电压;根据第二电压确定出第二引脚的短路情况;其中,第二引脚与第一引脚为芯片中不同引脚。

10、根据本发明的第二方面,提供了根据本发明第一方面的设备,该设备包括:测试向量生成电路和检测电路;测试向量生成电路,用于将芯片上除被测引脚之外的其他引脚均接地,以及向芯片中被测引脚施加测量电流;检测电路,用于检测所述被测引脚的电压;以及根据所述电压确定所述被测引脚短路情况。

11、本发明利用引脚电路中二极管的单向导电特性,针对每个引脚向其对应的io单元提供正向和/或负向电流来构建测试量,根据io单元对应的测试量情况即可确定io单元对应的引脚短路情况,减少了检测的次数,降低检测时间,进而可以提高检测芯片引脚短路的效率。

技术特征:

1.一种芯片引脚短路的检测方法,所述芯片包括n个待测试引脚,其特征在于,所述方法包括:

2.根据权利要求1所述的检测方法,其特征在于,其中,所述测量电流包括正向电流和/或负向电流。

3.根据权利要求2所述的检测方法,其特征在于,

4.根据权利要求2或3所述的检测方法,其特征在于,其中,

5.根据权利要求1-4任一项所述的检测方法,其特征在于,其中,

6.根据权利要求5所述的检测方法,其特征在于,其中,

7.一种设备,其特征在于,包括:测试向量生成电路和检测电路;

技术总结

本发明公开了芯片引脚短路的检测方法及设备,所述芯片包括N个待测试引脚,该方法包括:将芯片上除被测引脚之外的其他引脚均接地,向芯片中被测引脚施加测量电流,检测所述被测引脚的电压;根据所述电压确定所述被测引脚短路情况。利用引脚电路中二极管的单向导电特性,针对每个引脚向其对应的IO单元提供正向和/或负向电流来构建测试量,根据IO单元对应的测试量情况即可确定IO单元对应的引脚短路情况,减少了检测的次数,降低检测时间,进而可以提高检测芯片引脚短路的效率。

技术研发人员:陈绕所,周刚

受保护的技术使用者:上海忆芯实业有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!