一种基于瞬态电流的半导体器件快界面态表征方法

本发明属于半导体测试领域,涉及一种基于瞬态电流的半导体器件快界面态表征方法。

背景技术:

1、半导体的界面研究在半导体物理学和器件工艺中占据着很重要的地位。半导体-绝缘介质接触在微电子技术中有广泛应用,sio2/si是典型的半导体-绝缘介质接触。在sio2/si界面存在有:由于硅晶格周期性中断而产生的“快界面态”与由于氧化、金属杂质、结构缺陷等原因产生的“慢界面态”。这些界面态可以俘获电子也可以俘获缺陷,其会极大的影响器件的最终性能与可靠性。因此如何准确地提取界面态成为微电子器件工艺中至关重要的一环。目前,对于快界面的表征提取面临着巨大的挑战,一方面由于器件的尺寸不断缩小,快界面对器件可靠性与性能影响更为明显;另一方面,由于芯片的工作频率不断升高导致对器件的高频性能的要求升高,准确的提取快界面态的方法可以有效的实现对器件在高频状况下的模拟。

2、目前的器件的界面态提取一般是采用准静态法、电导法、s-factor法,其原理是通过测量器件的电容-电压关系曲线,然后根据电容-电压曲线进行数据化处理,计算得出界面态密度,该类方法一般应用有以下要求:1、由于快界面态可以响应高频信号,故在电容-电压曲线测量过程中会产生电容效应,使金属氧化物半导体器件的电容-电压特性曲线形状发生畸变,故传统方法只能应用于慢界面态的提取;2、以上几种方法的界面态测试对测试设备要求更高,且计算过程繁琐,无法快速提取界面态密度的大小。

3、本发明提出了一种基于瞬态电流的半导体器件快界面态表征方法,通过获取样品在不同激励条件下的瞬态信息对样品的界面缺陷进行相关分析,本质上是通过运用电容、电流和电荷的瞬态测量。但值得注意的是传统的dlts(深能级瞬态光谱检测)法测试的界面态密度仍然是通过电容的瞬态值进行测量,其仍然无法准确的响应高频信号的快界面态。因此本发明提出一种基于电流的dlts法的快界面态的表征方法,利用器件在不同激励信号的输入下的电流瞬态值进行测试计算,其实质是不同上升、下降时间的方波脉冲边沿,界面态会俘获电子和空穴,因此在源漏和衬底分别产生电子电流与空穴电流,该过程伴随着反型层电荷的积累与释放,故在通过高速的电流放大器获取到电流大小时,如何提取电子电流与空穴电流至关重要。本发明通过电路设计采用了高速的电流-电压转换放大电路,实现对器件输出电流的测量,克服当前传统快界面态测试方法的限制,具有一系列优点。首先,基于电流的dlts法的快界面态的表征方法不涉及到器件电容曲线的测量,故其不受快界面导致电容曲线畸变的影响;其次,该测试方法不但可以进行快界面态的测试,对于传统的慢态测试也十分可靠;此外基于电流的dlts法的快界面态的表征装置结构简单,易于集成,有利于测试系统的小型化一体化;最后基于电流的dlts法的快界面态的表征方法的理论分析十分可靠,数据处理过程清晰可靠。综上所述,本发明提出的基于电流的dlts法的快界面态的表征方法具有很好的应用前景。

技术实现思路

1、本发明的目的在于针对现有的界面态测试方法在快界面态测试方面的不足,提出一种基于瞬态电流的半导体器件快界面态表征方法,该方法具有测试效率高、测试准确度高、应用范围广、测试结构小型化、计算便捷等优势,在数字电路与模拟电路的pdk模型的界面态参数修正与器件的可靠性、失效分析等多个领域具有广泛的应用前景。

2、本发明的目的是通过以下技术方案来实现的:一种基于瞬态电流的半导体器件快界面态表征方法,该方法包括以下步骤:

3、s1,在待测半导体器件的栅极通过信号发生器施加多组不同上升和下降时间的阶跃信号/阶梯信号,使栅氧化物和衬底形成的快界面态在信号的上升沿和下降沿快速填充或释放界面电荷,从而产生感应电流;

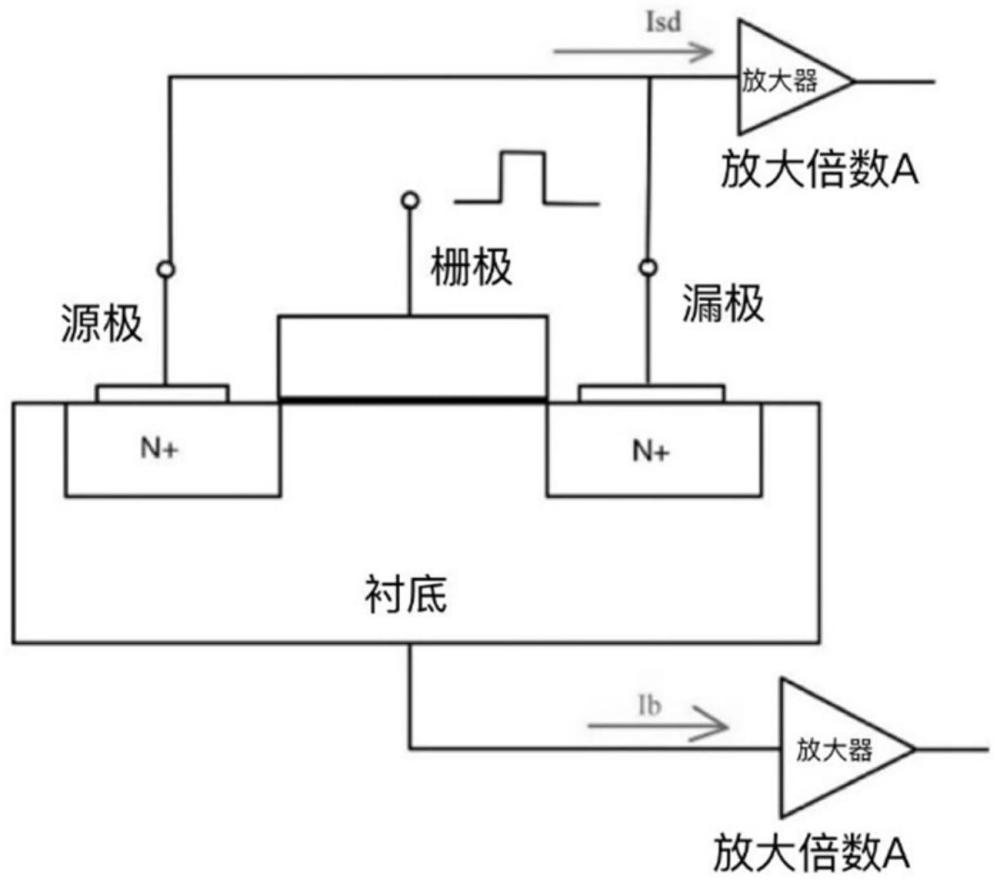

4、s2,在激励信号的上升沿和下降沿对源漏电流isd与衬底电流ib进行电流-电压信号放大并采样;

5、s3,将s2得到的采样值按不同激励信号的时间边沿进行积分,获取不同响应时间的界面电荷与反型层电荷的和;

6、s4,在待测半导体器件的栅极通过信号发生器施加一组上升和下降时间足够长的阶跃信号/阶梯信号,获取界面电荷的总量与反型层电荷的和;

7、s5,根据s3和s4得到的结果,获取不同响应时间的界面态密度。

8、进一步地,对待测半导体器件的栅极施加的激励信号的时间边沿包括但不限于10-8s,在10-8s时也能够实现快界面态表征。

9、进一步地,所述待测半导体器件包含但不限于金属-氧化物半导体场效应晶体管、铁电栅场效应管。

10、进一步地,利用待测半导体器件在栅极施加阶跃信号的情况下,快界面态会快速释放或俘获界面电荷从而产生电流这一特性,实现对不同响应时间的快界面态密度的表征。

11、进一步地,利用待测半导体器件在栅极施加阶梯信号的情况下,快界面态会快速释放或俘获界面电荷从而产生电流这一特性,实现对不同能级的快界面态密度的表征。

12、进一步地,步骤s2中采用带宽大于100mhz且有良好的相位特性的电流-电压转换电路实现对电流的放大。

13、进一步地,步骤s2中对所述电流-电压转换电路输出的电压信号通过模拟-数字转换电路转换为数字信号,并通过主控板传输到pc进行数据处理。

14、进一步地,步骤s4中施加的激励信号的时间边沿相比于步骤s1中施加的多组激励信号中最大的时间边沿多至少一个量级。

15、进一步地,步骤s3中,获取不同响应时间的界面电荷与反型层电荷的和的计算公式为:

16、

17、

18、其中为响应时间在tdown内的界面电荷,为响应时间在tup内的界面电荷,qinv为反型层电荷,tdown为下降沿的时间长度,tup为上升沿的时间长度,vb为s2从衬底电流放大采样得到的电压信号,vs/d从源漏电流放大采样得到的电压信号,a为电流-电压转换的放大倍数。

19、进一步地,步骤s4中,获取界面电荷的总量与反型层电荷的和的计算公式如下:

20、

21、

22、其中qit,total为界面电荷的总量,temission为足够长的下降沿的时间长度temission>>tdown,tcapture为足够长的上升沿的时间长度,tcapture>>tup;

23、分别将公式(3)与公式(1)、公式(4)与公式(2)做差值,得到响应时间大于tdown的界面电荷qit与响应时间大于tup的界面电荷qit,结合电子电荷q和栅氧化物面积s,分别得到响应时间大于tdown与tup的界面态密度dit,公式为

24、当tdown与tup大小相等时,其分别计算得到的界面态密度dit大小相等,因为其获取得到的是相同响应时间范围内的界面态。

25、本发明采用的原理是在激励信号的上升沿,被测半导体器件的界面态会从被测半导体器件源漏俘获电子,因此会在被测半导体器件的源漏产生由于电子俘获产生的填充电流;同样的,在输入激励信号的下降沿,被测半导体器件的界面态会释放电子,这些释放的电子会与衬底的多子复合,在被测半导体器件的衬底产生复合电流。

26、本发明的有益效果是:本发明可以快速且准确的表征各类器件的快界面态的密度。传统方法测得的界面态的响应频率往往低于1mhz,对于响应频率高于1mhz的界面态的测试结果并不准确,且传统方法采用的srh模型的可靠性仍然有待商榷。本发明提出的基于瞬态电流的半导体器件快界面态表征方法,其通过高速的电流-电压转换电路可以准确测的响应频率高于1mhz的界面态密度;且其原理是采用的是在不同电压条件下,界面电荷会俘获和释放电荷这一特性,不依赖于srh物理模型,理论依据可靠,测试结果更为准确。

- 还没有人留言评论。精彩留言会获得点赞!