芯片测试器、其制造方法及芯片测试装置与流程

本技术涉及芯片测试,尤其是涉及一种芯片测试器、其制造方法及芯片测试装置。

背景技术:

1、芯片测试器是一种用于对芯片进行测试的器械,其包括绝缘基板、设于绝缘基板上的多根测试针,该多根测试针的一端部与电路板连接、另一端部为测试端,通过多个测试端与芯片侧部的引脚接触从而实现对芯片的测试。上述的芯片测试器在制造时,需要预先加工出多根测试针,随后将多根测试针逐个贴合在绝缘基板上,并使测试针的一端部突出于绝缘基板,以与芯片侧部的引脚相接触。

2、针对上述的相关方案,发明人认为存在以下缺陷:第一,将多根测试针逐个贴合在绝缘基板上,不仅效率较低,而且多根测试针的贴合位置、贴合角度等参数不可避免的会出现误差,从而会影响制得的测试片的测试精度;第二,为了保证测试针与芯片的接触效果,测试针的测试端需要延伸出较大的长度,较长的测试端无法得到有效的保护,其在多次使用后容易发生断裂,极大的降低了芯片测试器的使用寿命;第三,为了避免芯片与电路板发生干涉,分别用于连接芯片和电路板的测试针的两端部之间需要具有足够的距离,也即是说测试针需要具有足够的长度,较长的测试针容易在使用过程中发生弯曲或断裂,从而影响芯片测试器的使用。

技术实现思路

1、本技术的第一个目的是克服现有技术的不足,提供一种能够为测试针和测试端提供有效保护的芯片测试器。

2、本技术提供的一种芯片测试器采用如下技术方案:

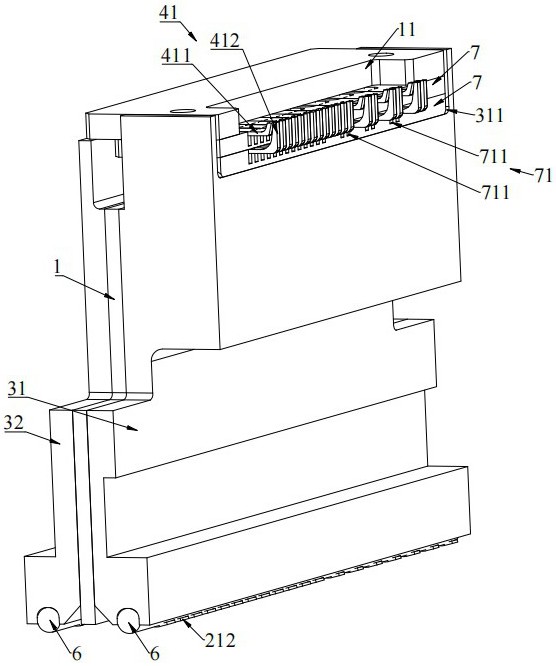

3、一种芯片测试器,包括绝缘基板、第一测试片、第一绝缘块和第二测试片,所述第一测试片包括多根贴设于所述绝缘基板上且沿着所述绝缘基板的宽度方向排布的第一测试针,所述第一绝缘块扣压于所述绝缘基板贴设有所述第一测试针的一侧部,所述第二测试片包括多根沿着所述绝缘基板的宽度方向排布的第二测试针,所述的多根第二测试针的一端部与所述的多根第一测试针一一对应且相互压接,所述的多根第二测试针的另一端部沿着所述绝缘基板至所述第一绝缘块的方向弯折形成第一弯折部,所述第一弯折部承载于所述第一绝缘块端部,所述第一弯折部突出所述第一绝缘块的一端沿着所述第一测试片至所述第二测试片的方向弯折并形成测试端。

4、通过采用上述技术方案,将第一测试针与第二测试针相互压接并组合成一整体,不仅能够保证芯片和电路板之间的有效距离,避免两者发生干涉,而且相互压接的第一测试针和第二测试针相比单个的测试针,其强度更高;同时,将第一绝缘块扣压于绝缘基板上,不仅能够对第一测试针进行保护,而且第一绝缘块端部能够承托于第一弯折部下方,使得测试端只需适当突出第一绝缘块即可与芯片引脚接触,有效的避免了测试端的伸出长度过大而在使用过程中发生断裂,延长了芯片测试器的使用寿命。

5、优选的,所述第一测试针的一端部为第一连接端,所述第二测试针的一端部为第二连接端,所述第一连接端和所述第二连接端相互压接,所述第一连接端和所述第二连接端的其中一个上设置有多个用于与其中另一个相抵接的压接部,所述的多个压接部沿着所述第一测试片至所述第二测试片的方向间隔排布,所述压接部呈梯台状。

6、通过采用上述技术方案,有效的提升了第一连接端与第二连接端的压接强度。

7、优选的,所述第一测试针远离所述第一连接端的一端部穿出所述第一绝缘块并沿着所述绝缘基板至所述第一绝缘块的方向弯折形成第二弯折部,所述第一绝缘块靠近所述第二弯折部的一端设置有胶条,所述胶条突出所述第一绝缘块并与所述第二弯折部相抵触。

8、通过采用上述技术方案,有效的增加了第二弯折部与电路板的接触面积,提升了芯片测试器对芯片的测试效果。

9、优选的,所述第一测试片有两个,所述的两个第一测试片分别贴设于所述绝缘基板厚度方向的两侧部,所述第一绝缘块有两个,所述的两个第一绝缘块包括绝缘块a和绝缘块b,所述绝缘块a和所述绝缘块b分别扣压于所述绝缘基板厚度方向的两侧部,所述第二测试片有两个,所述的两个第二测试片与所述的两个第一测试片相对应连接,两个所述的第一弯折部分别承载于所述绝缘块a的一端部。

10、优选的,所述绝缘基板厚度方向的两侧部分别开设有用于容置所述的两个第一测试片的第一承载槽,所述第一承载槽包括用于容置所述第一测试片主体的第一槽体、分别连通于所述第一槽体两端的多条第二槽体和多条第三槽体,多个所述的第一连接端分别一一对应的嵌设于所述的多条第二槽体中,所述的多根第一测试针远离所述第一连接端的一端部分别一一对应的嵌设于所述的多条第三槽体中。

11、通过采用上述技术方案,能够有效的实现第一测试片与绝缘基板的相对固定,避免第一测试片在测试时发生损坏,延长了芯片测试器的使用寿命。

12、优选的,所述的两个第一绝缘块上分别开设有用于对应的容置所述的两个第二测试片的第二承载槽,所述第二承载槽包括多条间隔设置的第四槽体,多个所述的第二连接端分别一一对应的嵌设于所述的多条第四槽体中。

13、通过采用上述技术方案,能够有效的实现第一绝缘块与第二测试片的相对固定,避免第二测试片在测试时发生损坏,延长了芯片测试器的使用寿命。

14、优选的,所述绝缘块a的一端部开设有安装槽,所述安装槽内层叠设置有两个第二绝缘块,所述的两个第一弯折部分别一一对应的承载于所述的两个第二绝缘块上。

15、通过采用上述技术方案,两个第二绝缘块能够分别承载两个第一弯折部,实现第二绝缘块与第一弯折部的相对固定,避免第一弯折部在测试时发生损坏,延长了芯片测试器的使用寿命。

16、优选的,所述的两个第二绝缘块上分别开设有用于容置所述的两个第一弯折部的第三承载槽,所述第三承载槽包括多条间隔排布的第五槽体,构成所述第一弯折部的多根所述的第二测试针分别一一对应的嵌设于所述的多条第五槽体中。

17、通过采用上述技术方案,能够有效的实现第二绝缘块与第一弯折部的相对固定,避免第一弯折部在测试时发生损坏,延长了芯片测试器的使用寿命。

18、本技术的第二个目的是提供一种能够有效的避免制得的芯片测试器上的测试针在绝缘基板上的安装位置和角度产生偏差的芯片测试器的制造方法。

19、本技术提供的一种芯片测试器的制造方法采用如下技术方案:

20、一种芯片测试器的制造方法,包括如下步骤:

21、步骤a,选取一第一金属片,在所述第一金属片上沿其宽度方向切割出多条第一长槽,每条所述的第一长槽两侧部分别形成第一测试针,所述第一金属片长度方向的至少一端部形成用于连接所述的多根第一测试针的第一连接条;

22、步骤b,选取一绝缘基板,将所述绝缘基板贴合于所述第一金属片的中部,并使所述绝缘基板的长度方向与所述第一测试针的长度方向一致,随后将所述第一连接条切除;

23、步骤c,选取一第二金属片,在所述第二金属片上沿其宽度方向切割出多条与所述的多条第一长槽一一对应的第二长槽,每条所述的第二长槽两侧部分别形成第二测试针,所述第二金属片长度方向的一端部形成用于连接所述的多根第二测试针的第二连接条,将多根所述的第二测试针远离所述第二连接条的一端部一一对应的压接于所述的多根第一测试针的一端部;

24、步骤d,选取一绝缘块,将所述绝缘块扣压于所述绝缘基板贴合有所述第一金属片的一侧部,所述绝缘块长度方向的一端部具有承载面,将所述的多根第二测试针靠近所述第二连接条的一端部沿着所述绝缘基板至所述绝缘块的方向弯折形成第一弯折部,随后将所述第一弯折部压嵌于所述承载面中;

25、步骤e,将所述第一弯折部突出所述绝缘块的一端部沿着所述第一金属片至所述第二金属片的方向弯折,随后将所述第二连接条切除。

26、通过采用上述技术方案,能够有效的避免第一测试针和第二测试针与绝缘基板之间的安装位置和安装角度产生偏差,提升了制得的芯片测试器的测试精度;同时,能够有效的保证多根第一测试针和多根第二测试针之间的精准对接,进一步提升了制得的芯片测试器的测试精度。

27、本技术的第三个目的是提供一种芯片测试装置。

28、本技术提供的一种芯片测试装置采用如下技术方案:

29、一种芯片测试装置,包括测试座,所述芯片测试装置还包括两个如上所述的芯片测试器,所述的两个芯片测试器分别设于所述测试座两端,构成所述的两个芯片测试器的两个测试端相对设置,所述的两个测试端之间形成用于容置芯片的测试间隙,所述芯片两侧分别设置有若干引脚,所述的两个测试端分别承托于所述芯片两侧的若干引脚下部。

30、通过采用上述技术方案,测试时只需将芯片放置于测试间隙中即可进行测试,测试效率高。

31、综上所述,本发明包括以下至少一种有益技术效果:

32、1.本技术的芯片测试器,将第一测试针与第二测试针相互压接并组合成一整体,不仅能够保证芯片和电路板之间的有效距离,避免两者发生干涉,而且相互压接的第一测试针和第二测试针相比单个的测试针,其强度更高;

33、2.本技术的芯片测试器,其将第一绝缘块扣压于绝缘基板上,不仅能够对第一测试针进行保护,而且第一绝缘块端部能够承托于第一弯折部下方,使得测试端只需适当突出第一绝缘块即可与芯片引脚接触,有效的避免了测试端的伸出长度过大而在使用过程中发生断裂,延长了芯片测试器的使用寿命;

34、3.本技术的制造方法,其能够有效的避免第一测试针和第二测试针与绝缘基板之间的安装位置和安装角度产生偏差,提升了制得的芯片测试器的测试精度;

35、4.本技术的制造方法,能够有效的保证多根第一测试针和多根第二测试针之间的精准对接,进一步提升了制得的芯片测试器的测试精度;

36、5.本技术的芯片测试装置,其在测试时只需将芯片放置于测试间隙中即可进行测试,测试效率高。

- 还没有人留言评论。精彩留言会获得点赞!