基于异构冗余的国产化底盘综合控制器及控制方法与流程

1.本发明涉及底盘综合控制技术领域,尤其涉及一种基于异构冗余的国产化底盘综合控制器及控制方法。

背景技术:

2.目前,大多数混合动力特种车辆都配置了底盘综合控制器(vcu:vehicle control unit),用于完成底盘能源、动力、转向、制动、安全和故障诊断等核心控制功能。

3.军用特种车辆在信息化、智能化方面不断涌现出新需求,分系统之间、系统内部各设备之间信息交互更加紧密,控制策略更加复杂,而单一处理器存在一定的不可靠因素。虽然国内厂商已经根据用户需求开发和量产了很多货架产品,但这些vcu的硬件设计大部分都是基于国外进口芯片,特别是在电源、处理器、存储器、通讯接口等设计方面严重依赖进口芯片,且目前没有基于冗余的底盘综合控制器,不符合自主可控的发展方向,而核心技术和产品自主可控已经成为军用装备研制的基本要求和设计原则,进口芯片成为不符合自主可控的发展方向的重要阻碍。

4.因此,现有技术中却反一种基于异构冗余的国产化底盘综合控制器及控制方法。

技术实现要素:

5.鉴于上述的分析,本发明实施例旨在提供一种基于异构冗余的国产化底盘综合控制器及控制方法,用以解决现有没有基于冗余机制的国产化的底盘综合控制器的问题。

6.一方面,本发明实施例提供了一种基于异构冗余的国产化底盘综合控制器,包括:

7.处理器模块,包括主处理器电路和从处理器电路,所述主处理器电路周期发送在线工作标志并且完成系统控制功能,所述从处理器电路实时监测所述标志信息,与所述主处理器电路接收相同信息,执行相同控制逻辑;所述从处理器电路监测到所述标志信息消失后判定主处理器工作异常,发送使能指令,接替所述主处理器电路完成系统控制功能;

8.通讯接口模块,包括第一通信单元和第二通信单元,所述主处理器电路与所述第一通信单元连接,通过所述第一通信单元与外部设备进行通信;所述从处理器电路与所述第二通信单元连接,通过所述第二通信单元实时监听所述主处理器电路通过第一通信单元发送和接收的信息;当所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一通信单元断开,所述从处理器电路通过所述第二通信单元与外部设备进行通信。

9.进一步地,所述第一通信单元包括第一串口通信子单元,所述第二通信单元包括第二串口通信子单元;

10.所述主处理器电路与所述第一串口通信单元连接,通过外部通讯串口与外部设备进行通信;所述从处理器电路与所述第二串口通信单元连接,所述第二串口通信单元与所述外部通讯串口连接,实时监听所述主处理器电路通过第一串口通信单元发送和接收的信息;当所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一

串口通信单元断开,所述从处理器电路通过所述第二串口通信单元与外部设备进行通信。

11.进一步地,所述第一串口通信子单元,包括:第一隔离与逻辑电路、第一串口收发器电路、第一串口保护电路和串口阻抗匹配电路;所述主处理器电路sci信号和gpio信号经过所述第一隔离与逻辑电路变换后接入所述第一串口收发器电路,经所述第一串口收发器电路选择通讯模式后通过所述第一串口保护电路和串口阻抗匹配电路输出数据;

12.所述第二串口通信子单元,包括:第二隔离与逻辑电路、第二串口收发器电路、第二串口保护电路和所述串口阻抗匹配电路;所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一串口收发器电路断开,所述从处理器电路sci信号和gpio信号经过所述第二隔离与逻辑电路变换后接入所述第二串口收发器电路,经所述第二串口收发器电路选择通讯模式后通过所述第二串口保护电路和串口阻抗匹配电路输出数据。

13.进一步地,所述第一通信单元还包括第一can口通信子单元,所述第二通信单元还包括第二can口通信子单元;

14.所述主处理器电路与所述第一can口通信子单元连接,通过外部通讯can口与外部设备进行通信;所述从处理器电路与所述第二can口通信子单元连接,所述第二can口通信子单元与所述外部通讯can口连接,实时监听所述主处理器电路通过第一can口通信子单元发送和接收的信息;当所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一can口通信子单元连接断开,所述从处理器电路通过所述第二can口通信子单元与外部设备进行通信。

15.进一步地,所述第一can口通信子单元,包括:第一隔离电路、第一can口收发器电路、第一can口保护电路和can口阻抗匹配电路;所述主处理器电路信号ecan信号隔离后接入所述第一can口收发器电路,所述第一can口收发器电路将隔离后的单端信号变换为can通讯信号,所述第一can口保护电路为接口提供过压保护和滤波,经所述can口阻抗匹配电路后输出数据;

16.所述第二can口通信子单元,包括:第二隔离电路、第二can口收发器电路、第二can口保护电路和所述can口阻抗匹配;所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一can口收发器电路断开,所述从处理器电路ecan信号隔离后接入所述第二can口收发器电路,所述第二can口收发器电路将隔离后的单端信号变换为can通讯信号,所述第二can口保护电路为接口提供过压保护和滤波,经所述can口阻抗匹配电路后输出数据。

17.进一步地,所述主处理器电路工作正常时,屏蔽所述第二通信单元的发送功能。

18.进一步地,还包括:输入模块,包括第一模拟输入单元、第二模拟输入单元和数字输入单元;

19.所述主处理器电路通过所述第一模拟输入单元输入高精度数据;

20.当所述主处理器电路工作异常时,所述从处理器电路通过所述第二模拟输入单元直接输入调理信号;

21.所述主处理器电路和所述从处理器电路通过数字输入单元输入数字信号。

22.另一方面,本发明实施例提供了一种基于异构冗余的国产化底盘综合控制器的控制方法,包括:

23.主处理器电路周期发送在线工作标志并且完成系统控制功能,通过外部通讯接口与外部设备进行通信;

24.从处理器电路通过第二通信单元与所述外部通讯接口连接,实时监听所述主处理器电路通过第一通信单元发送和接收的信息,与所述主处理器电路接收相同信息,执行相同控制逻辑,并实时监测所述标志信息;

25.所述从处理器电路监测到所述标志信息消失后判定主处理器工作异常,发送使能指令,接替所述主处理器电路完成系统控制功能;所述从处理器电路将所述主处理器电路与所述第一通信单元断开,所述从处理器电路通过所述第二通信单元与外部设备进行通信。

26.进一步地,包括:

27.所述主处理器电路工作正常时,屏蔽所述第二通信单元的发送功能。

28.进一步地,所述主处理器电路通过所述第一模拟输入单元输入高精度数据;

29.当所述主处理器电路工作异常时,所述从处理器电路通过所述第二模拟输入单元直接输入调理信号;

30.所述主处理器电路和所述从处理器电路通过数字输入单元输入数字信号。

31.与现有技术相比,本发明至少可实现如下有益效果之一:

32.1、国产化底盘综合控制器,选用国产化成熟的军用级芯片,从设计到应用均可实现自主可控,且其应用温度从工业级扩展至军温级;

33.2、采用处理器、通讯接口的双冗余配置,可满足高可靠性应用场景;

34.3、冗余处理机制不依赖第三方裁决器,从处理器直接根据主处理器是否发送标志信息判断,当主处理器异常时,可快速接替主处理器工作;

35.4、从处理器与主处理器同步接收信息,并执行相同的控制逻辑,主处理器和从处理器的转态同步,可以提高异常处理的精度。

36.本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

附图说明

37.附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

38.图1为本技术一个实施例所示的基于异构冗余的国产化底盘综合控制器结构示意图;

39.图2为本技术一个实施例所示的处理器模块结构示意图;

40.图3为本技术一个实施例所示的通讯接口模块结构示意图;

41.图4为本技术一个实施例所示的串口通讯接口模块构示意图;

42.图5为本技术一个实施例所示的can口通讯接口模块构示意图;

43.图6为本技术一个实施例所示的模拟输入单元结构示意图;

44.图7为本技术一个实施例所示的数字输入单元结构示意图;

45.图8为本技术一个实施例所示的电源管理模块结构示意图;

46.图9为本技术一个实施例所示的低边驱动电路结构示意图;

47.图10为本技术一个实施例所示的基于异构冗余的国产化底盘综合控制器的控制方法流程图。

具体实施方式

48.下面结合附图来具体描述本发明的优选实施例,其中,附图构成本技术一部分,并与本发明的实施例一起用于阐释本发明的原理,并非用于限定本发明的范围。

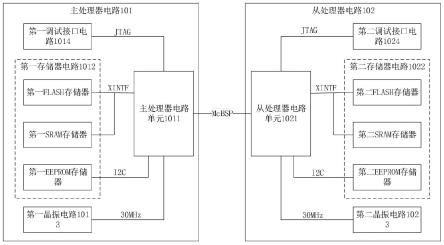

49.本发明的一个具体实施例,公开了一种基于异构冗余的国产化底盘综合控制器,如图1所示,包括:处理器模块10、通讯接口模块20、输入模块30、电流驱动模块40、电源管理模块50、存储器模块60和实时时钟模块70。

50.目前,底盘综合控制器各模块均为国外进口芯片,且存储器模块60、输入模块30大多都被集成到处理器模块10中,造成整个vcu硬件设计方案非常依赖处理器模块10主处理芯片的具体型号,一旦处理器模块10主处理芯片出现供货短缺,直接导致整车研制和交付进度脱期。另外,货架vcu产品允许的工作温度范围只有-40℃~85℃,不符合军用装备对环境条件的基本要求。

51.本技术实施例中基于异构冗余的国产化底盘综合控制器,从具体设计到芯片选型,均可实现自主可控;采用处理器双冗余配置,满足高可靠性应用场景;由于芯片均来自国内厂商的成熟军用级产品,因此,本实施例中基于异构冗余的国产化底盘综合控制器可达到军温级工作范围。

52.具体地,电源管理模块50将外部供电变换成处理器模块10、通讯接口模块20、输入模块30、电流驱动模块40、存储器模块60和实时时钟模块70需要的二次电源;电流驱动模块40接收处理器模块10发送的控制指令,按照指令要求,闭合或者断开驱动开关,对负载执行高边或低边驱动,向处理器模块10回传状态;通讯接口模块20由处理器模块10直接控制,负责通讯协议栈解析和链路层接口匹配,与底盘其他设备通讯;实时时钟模块70为处理器模块10提供绝对时间基准,用于文件记录;处理器模块10是vcu的核心,控制模拟输入单元301、数字输入单元302、电流驱动模块40、和通讯接口模块20执行信号采集和测量、功率驱动、内部和外部通讯,根据传感器信号、开关信号状态,实现对底盘设备、电动附件的逻辑和流程控制、安全保护、故障诊断等功能,通过通讯接口模块20,将重要信息上报给驾驶员仪表台。

53.具体地,处理器模块10包括主处理器电路101和从处理器电路102,所述从处理器电路102与主处理器电路101通过多通道缓冲串口连接(mcbsp),所述主处理器电路101周期发送在线工作标志并且完成系统控制功能,所述从处理器电路102实时监测所述标志信息,与所述主处理器电路101接收相同信息,执行相同控制逻辑;所述从处理器电路102监测到所述标志信息消失后判定主处理器电路101工作异常,发送使能指令,接替所述主处理器电路101完成系统控制功能;所述主/从处理器电路根据所述控制逻辑控制;具体地,所述控制逻辑包括:高/低压上电控制逻辑,行驶前安全性检查、轮边电机扭矩、转速控制、转向角控制和制动控制;具体地,存储器模块60可裁剪,根据处理器模块10片上存储器规模,为其扩展容量;

54.具体地,如图2所示,为了实现三级以上软硬件安全监控功能,采用主处理器电路101+从处理器电路102的双冗余配置方案;更具体地,主处理器电路101,包括主处理器电路单元1011、第一存储器电路1012、第一晶振电路1013和第一调试接口电路1014;从处理器电路102,包括从处理器电路单元1021、第二存储器电路1022、第二晶振电路1023和第二调试接口电路1024。

55.可选地,主处理器电路单元1011与从处理器电路单元1021选用国产32位dsp处理器,型号为jdsp28335,其内置浮点运算单元,主频达到150mhz,自带硬件加密锁,可保证主处理器电路单元1011片上存储器访问安全。vcu核心控制程序在主处理器电路单元1011和从处理器电路单元1021中同时执行,构成功能热备份;在正常情况下,主处理器电路101为主控、从处理器电路102为备份,主处理器电路101通过多通道缓冲串口(mcbsp)周期发送在线工作标志并且完成系统控制功能,从处理器电路102实时监测主处理器电路101在线标志,并与主处理器电路101软件接收相同信息,执行相同控制逻辑,但屏蔽指令发送功能;主处理器电路单元1011故障时,从处理器电路102监测到主处理器电路101在线状态消失,使能指令发送,迅速接替主处理器电路101完成系统控制功能。

56.更具体地,第一存储器电路1012,包括:第一flash存储器、第一sram存储器和第一eeprom存储器;第二存储器电路1022,包括:第二flash存储器、第二sram存储器和第二eeprom存储器;主处理器电路单元1011和从处理器电路单元1021通过xintf接口读写各自扩展的片外flash存储器;主处理器电路单元1011和从处理器电路单元1021通过xintf接口读写数据(与flash存储器分时复用xintf接口);主处理器电路单元1011和从处理器电路单元1021通过使用i2c接口访问第一eeprom存储器和第二eeprom存储器。

57.可选地,第一flash存储器和第二flash存储器选用国产nor flash存储器,型号为sm29lv160,容量为16mbit,兼容3.3v cmos电平,用于存储程序和数据;第一sram存储器和第二sram存储器选用国产sram存储器,用于为程序运行提供数据空间,型号为jm64lv25616,容量为256k

×

16bit,兼容3.3v cmos电平;第一eeprom存储器和第二eeprom存储器选用国产eeprom存储器,用于保存故障代码,型号为sm9977,容量为32kb,通过电平转换兼容3.3vcmos电平。

58.更具体地,第一晶振电路1013和第二晶振电路1023,分别为主处理器电路单元1011和从处理器电路单元1021提供外部时钟。可选地,第一晶振电路1013和第二晶振电路1023可选择无源晶体谐振器或者有源晶体振荡器,频率为30mhz。

59.更具体地,第一调试接口电路1014和第二调试接口电路1024为标准jtag接口,用于分别调试或下载程序到主处理器电路单元1011和从处理器电路单元1021。

60.具体地,通讯接口模块20,包括第一通信单元和第二通信单元,所述主处理器电路101与所述第一通信单元连接,通过外部通讯接口与外部设备进行通信;所述从处理器电路102与所述第二通信单元连接,所述第二通信单元与所述外部通讯接口连接,实时监听所述主处理器电路101通过第一通信单元发送和接收的信息;当所述主处理器电路102工作异常时,所述从处理器电路102将所述主处理器电路101与所述第一通信单元断开,所述从处理器电路102通过所述第二通信单元与外部设备进行通信;

61.所述第一通信单元包括第一串口通信子单元201,所述第二通信单元包括第二串口通信子单元202;

62.所述主处理器电路与所述第一串口通信单元连接,通过外部通讯串口与外部设备进行通信;所述从处理器电路与所述第二串口通信单元连接,所述第二串口通信单元与所述外部通讯串口连接,实时监听所述主处理器电路通过第一串口通信单元发送和接收的信息;当所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一串口通信单元断开,所述从处理器电路通过所述第二串口通信单元与外部设备进行通信。

63.具体地,所述第一串口通信子单元201,包括:第一隔离与逻辑电路2011、第一串口收发器电路2012、第一串口保护电路2013和串口阻抗匹配电路205;所述主处理器电路sci(串行通讯接口:serial communications interface)信号和gpio(通用输入输出:general-purpose input/output)信号经过所述第一隔离与逻辑电路变换后接入所述第一串口收发器电路,经所述第一串口收发器电路选择通讯模式后通过所述第一串口保护电路和串口阻抗匹配电路输出数据,如图3所示:

64.所述第二串口通信子单元202,包括:第二隔离与逻辑电路2021、第二串口收发器电路2022、第二串口保护电路2023和所述串口阻抗匹配电路205;所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一串口收发器电路断开,所述从处理器电路sci信号和gpio信号经过所述第二隔离与逻辑电路变换后接入所述第二串口收发器电路,经所述第二串口收发器电路选择通讯模式后通过所述第二串口保护电路和串口阻抗匹配电路输出数据。

65.更具体地,如图4所示,第一隔离与逻辑电路2011和第二隔离与逻辑电路2021中隔离电路芯片可选型号为gl1200cs,逻辑电路芯片可选的型号为54ls14+54ls08,主处理器电路单元1011片上sci信号和gpio信号经过隔离、逻辑变换后接入第一串口收发器电路2012;第一串口收发器电路2012和第二串口收发器电路2022,选用标准差分收发器,型号为sm485,2片sm485通过方向控制逻辑可以实现软件选择通讯模式,支持半双工或全双工差分异步串行通讯;第一串口保护电路2013和第二串口保护电路2023,选用双向瞬态抑制二极管,为接口提供过压保护,型号为sy1512ca;串口阻抗匹配电路205为端接电阻,包括偏置电阻(提供总线空闲状态下的电压拉偏)和匹配电阻(匹配传输线的特征阻抗)。

66.具体地,所述第一通信单元还包括第一can口通信子单元203,所述第二通信单元还包括第二can口通信子单元204:

67.更具体地,所述主处理器电路与所述第一can口通信子单元203连接,通过外部通讯can口与外部设备进行通信;所述从处理器电路与所述第二can口通信子单元204连接,所述第二can口通信子单元204与所述外部通讯can口连接,实时监听所述主处理器电路通过第一can口通信子单元203发送和接收的信息;当所述主处理器电路工作异常时,所述从处理器电路将所述主处理器电路与所述第一can口通信子单元203连接断开,所述从处理器电路通过所述第二can口通信子单元204与外部设备进行通信。

68.具体地,如图3所示,所述第一can口通信子单元203,包括:第一隔离电路2031、第一can口收发器电路2032、第一can口保护电路2033和can口阻抗匹配电路206;所述主处理器电路ecan信号(增强型can信号)经第一隔离电路2031隔离后接入所述第一can口收发器电路2032,所述第一can口收发器电路2032将隔离后的单端信号变换为can通讯信号,所述第一can口保护电路2033为接口提供过压保护和滤波,经所述can口阻抗匹配电路206后输出数据;

69.所述第二can口通信子单元204,包括:第二隔离电路2041、第二can口收发器电路2042、第二can口保护电路2043和所述can口阻抗匹配206;所述主处理器电路101工作异常时,所述从处理器电路102将所述主处理器电路102与所述第一can口收发器电路2032断开,所述从处理器电路ecan信号经第二隔离电路2041隔离后接入所述第二can口收发器电路2042,所述第二can口收发器电路2042将隔离后的单端信号变换为can通讯信号,所述第二can口保护电路2033为接口提供过压保护和滤波,经所述can口阻抗匹配电路206后输出数据。

70.更具体地,如图5所示,第一隔离电路2031选用高速磁耦隔离器,型号为gl1200cs,将主处理器电路101片上ecan信号隔离后接入第一can口收发器电路2032,第一can口收发器电路2032选用符合标准的can收发器,型号为sm1040,将隔离后的单端信号变换为can通讯信号;第一can口保护电路2033选用双向瞬态抑制二极管+共模电感,双向瞬态抑制二极管选用型号为smaj24ca、共模电感选用型号为cmw2012-900t2,为接口提供过压保护和滤波;can口阻抗匹配电路206为端接电阻(匹配电阻),匹配传输线的特征阻抗。第二隔离电路2041选用高速磁耦隔离器,型号为gl1200cs,将从处理器电路102片上ecan信号隔离后接入第二can口收发器电路2042,第二can口收发器电路2042选用符合标准的can收发器,型号为sm1040,将隔离后的单端信号变换为can通讯信号;第二can口保护电路2043选用双向瞬态抑制二极管+共模电感,双向瞬态抑制二极管选用型号为smaj24ca、共模电感选用型号为cmw2012-900t2,为接口提供过压保护和滤波;can口阻抗匹配电路206为端接电阻(匹配电阻),匹配传输线的特征阻抗。

71.正常情况下,主处理器电路101负责对外通讯,发送指令或接收数据;从处理器电路102只工作在接收模式,实时监听总线消息,发送功能被屏蔽;主处理器电路101与从处理器电路102还可进行板内闭环测试。主处理器电路101故障时,从处理器电路102控制主处理器电路101端第一can口收发器电路/第一串口收发器电路2012断电,使其从总线断开,由从处理器电路102接替主处理器电路101完成对外通讯功能。所述主处理器电路工作正常时,屏蔽所述第二通信单元发送功能。

72.具体地,输入模块30,包括模拟输入单元和数字输入单元,模拟输入单元调理和采样传感器信号,执行模数转换,结果回传给处理器模块10;数字输入单元调理开关信号和频率信号,输出给处理器模块10,由处理器模块10执行电平识别、占空比捕获和频率测量;

73.具体地,模拟输入单元包括第一模拟输入单元、第二模拟输入单元和数字输入单元;所述主处理器电路101通过所述第一模拟输入单元输入高精度数据;当所述主处理器电路101工作异常时,所述从处理器电路102通过所述第二模拟输入单元直接输入调理信号;主处理器电路101采用片外模数转换器满足高精度应用,在主处理器电路101故障时,从处理器电路102使用从处理器电路单元1021主芯片片上模数转换器保证基本功能需求(降性能运行);

74.更具体地,如图6所示,模拟输入单元包括第一前置调理电路301、过压保护电路302、模拟开关电路303、仪表运放电路304、模数转换器电路305和基准源电路306。

75.更具体地,第一前置调理电路301为阻容网络,根据信号特性(电压或者电流),实现电流-电压转换、分压、滤波,将原始信号调理后接入过压保护电路。过压保护电路302可选用低压肖特基二极管和稳压二极管,对3.3v电源和地形成过压保护。从处理器电路102使

用片上模数转换器(12bit)直接采样调理信号。模拟开关电路303选用多通道低导通阻抗模拟开关,型号为cc4051,由主处理器电路101通过gpio控制,将模拟信号选通接入仪表运放电路304。仪表运放电路304选用仪表运算放大器,型号为7f620md,调理(放大+偏置)信号后输出给模数转换器电路305。模数转换器电路选用14bit逐次比较型模数转换器,型号为sad3578,主处理器电路101通过spi接口控制操作,将模拟信号转换为数字量。基准源电路306为模数转换器电路提供外部高精度电压基准,型号为7w431amfs。

76.具体地,所述主处理器电路101和所述从处理器电路102通过数字输入单元302输入数字信号,如图7所示,数字输入单元包括第二前置调理电路307和总线驱动电路308;第二前置调理电路307为阻容网络,根据信号特性(电压、频率),实现分压、滤波。总线驱动电路308选用芯片型号为sm164245,对调理信号进行电平转换和驱动,分两组接入主处理器电路101和从处理器电路102。按照信号频率区分,静态信号通过片上gpio端口直接采样电平,而动态信号通过片上ecap接口捕获边沿,实现占空比和频率(周期)测量。

77.具体地,如图8所示,电源管理模块50采用dc/dc+ldo+辅助电路+监控的设计架构,组成包括防反接保护电路501、浪涌抑制电路502、电源滤波电路503、dc/dc电源504、ldo电源505和监控电路506。更具体地,防反接保护电路501可选用pmos或低压肖特基二极管,将外部供电接入浪涌抑制电路502。浪涌抑制电路502与防反接保护电路501后级并联,利用瞬态抑制二极管和电阻,抑制浪涌电压,防止后级电路承受过电应力。电源滤波电路503与防反接保护电路501、浪涌抑制电路502串联,通过共模电感、y电容、差模电感、钽电容和陶瓷电容实现共模滤波+差模滤波,接入dc/dc电源504前级。dc/dc电源504选用非隔离buck型dc/dc电源变换器,将12v~24v宽幅电压变换为5v电压,直接为ldo电源505和板内其他电路供电。ldo电源505可选用2只单通道或1只双通道ldo电源,将5v降压为3.3v和1.9v,为处理器和i/o外设供电,也将3.3v接入监控电路506。监控电路506为3.3v电源提供电压监控和处理器上电复位。可选地,如果ldo电源505自带电压监控和复位功能,监控电路506可省略。

78.具体地,电流驱动模块40接针对不同负载特性,采用低边驱动+高边驱动的设计方案,组成包括低边驱动电路401、高边驱动电路402、第一过压保护电路403和第二过压保护电路404。

79.更具体地,如图9所示,低边驱动电路401选用带过电应力保护的多通道低边驱动开关,由主处理器电路101通过spi接口控制和读取开关状态,而冗余设计的从处理器102,主要是为了保证主处理器101异常时关键的通信功能和传感器数据采集,不直接控制电流驱动模块40。高边驱动电路402选用带过电应力保护的多通道高边驱动开关,由主处理器电路101通过spi接口和gpio接口控制和读取开关状态。第一过压保护电路403为稳压二极管与电容并联组合,与低边驱动电路401输出端口并联,第二过压保护电路404为稳压二极管与电容并联组合,与高边驱动电路402输出端口并联,防止负载承受过压。

80.如图10所示,本发明的另一个具体实施例,公开了一种基于异构冗余的国产化底盘综合控制器的控制方法,包括:

81.s10、主处理器电路周期发送在线工作标志并且完成系统控制功能,通过外部通讯接口与外部设备进行通信;

82.s20、从处理器电路通过第二通信单元与所述外部通讯接口连接,实时监听所述主处理器电路通过第一通信单元发送和接收的信息,与所述主处理器电路接收相同信息,执

行相同控制逻辑,并实时监测所述标志信息;

83.s30、所述从处理器电路监测到所述标志信息消失后判定主处理器工作异常,发送使能指令,接替所述主处理器电路完成系统控制功能;所述从处理器电路将所述主处理器电路与所述第一通信单元断开,所述从处理器电路通过所述第二通信单元与外部设备进行通信。

84.更具体地,所述主处理器电路工作正常时,屏蔽所述第二通信单元的发送功能。

85.更具体地,所述主处理器电路通过所述第一模拟输入单元输入高精度数据;

86.当所述主处理器电路工作异常时,所述从处理器电路通过所述第二模拟输入单元直接输入调理信号;

87.所述主处理器电路和所述从处理器电路通过数字输入单元输入数字信号。

88.本领域技术人员可以理解,实现上述实施例方法的全部或部分流程,可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于计算机可读存储介质中。其中,所述计算机可读存储介质为磁盘、光盘、只读存储记忆体或随机存储记忆体等。

89.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1