一种线上硬件实验透明化配置方法及系统

1.本发明属于线上硬件实验教学领域,特别涉及一种线上硬件实验透明化配置方法及系统。

背景技术:

2.计算机、网络通信技术的发展极大地促进了现代教育的发展,从多媒体教室到近年来蓬勃发展的mooc(大型开放式网络课程massive open online courses),教学内容、形式等都发生了较大的变化。线上课程、网上直播课甚至有时成为主要的教学手段,线上教学内容、方法等也成为时下的研究热点。一些软件类实验课程由线下转为线上,取得了较好的效果,一些与物理设备密切相关的理工类课程也在探索线上实验,乃至建立在线实验室。在线实验室有虚拟实验室和远程实验室两种形式,前者采用软件模拟,未涉及实际的硬件设备,在实验体验和效果等方面与真实的实验环境还有差距;后者利用网络与真实设备进行交互,使用户虽在远程却有身临其境的感觉。与线下实验室相比,在线实验室具有如下优点:1)便于管理,减少损耗。线下实验室设备众多,既有电源、电路板、仪表仪器,还有电路模块、连接线等,实验课之后,相关设备放置杂乱,整理工作量很大,丢失、损坏也时有发生。远程在线实验室虽然也有相关设备,但由于学生不与设备直接接触,便于统一部署与管理。2)打破时空界限,极大提高实验室的利用率。线下实验室大多必须在课上开展,利用率较低。为了提高利用率,有些学校尝试开放实验室,但管理起来比较麻烦。线上远程实验室则可随时随地开展实验,便于学生充分利用个人时间和实验设备,有效提高实验室利用率和学习效率。3)便于记录实验过程,全面掌握学生的学习情况。线下实验时,学生很多,老师很难关注到每个学生的实验过程,更不可能挨个指导。线上实验则可以充分利用实验管理系统和实验实景监控设备记录实验过程,便于老师根据相关实验记录掌握每个学生的学习情况。

3.由上可知,在线实验系统对促进线上实验课程的建设和发展、探索线上实验课程混合式教学模式等都具有十分重要的意义。然而,由于硬件配置实验平台通常由核心控制板和各种各样的传感器外围模块组成,往往需要根据实验内容安排实地插拔相关模块进行系统配置。因此,在线上实验室中,如何自动化地、透明地配置线上实验平台成为亟待解决的问题。

技术实现要素:

4.为此,本发明提供一种线上硬件实验透明化配置方法及系统,能够实现线上实验平台的灵活、透明化配置,提升线上硬件实验的效果,达到线上硬件实验目的,便于实际场景应用。

5.按照本发明所提供的设计方案,提供一种线上硬件实验透明化配置方法,用于核心控制板与外围模块之间的系统配置,包含如下内容:

6.通过互联网建立用户端上位机与实验室配置服务器之间的远程连接关系;

7.用户端利用上位机生成核心控制板与外围模块之间连接关系,并将该连接关系上

传至实验室中的配置服务器;

8.配置服务器依据核心控制板与外围模块之间连接关系生成连接关系表,并依据连接关系表确定fpga开发板管脚使用情况来获取fpga开发板的电路逻辑配置文件及管脚约束文件;根据电路逻辑配置文件及管脚约束文件,通过调用fpga开发工具对fpga开发板进行自动化配置。

9.作为本发明线上硬件实验透明化配置方法,进一步地,用户端依据实验需求,利用上位机软件建立核心控制板与外围模块之间的连接关系。

10.作为本发明线上硬件实验透明化配置方法,进一步地,用户端利用上位机与配置服务器之间的通信传输协议将连接关系传输至配置服务器。

11.作为本发明线上硬件实验透明化配置方法,进一步地,所述通信传输协议包含:核心控制板与外围模块之间的连线总数,若干核心控制板连线编号,及与每个核心控制板连线编号对应的外围模块连线编号。

12.作为本发明线上硬件实验透明化配置方法,进一步地,依据连接关系表确定fpga开发板管脚使用情况,所确定的fpga开发板管脚使用情况至少包含:输入输出类型、管脚之间的通联逻辑。

13.作为本发明线上硬件实验透明化配置方法,进一步地,获取fpga开发板的电路逻辑配置文件及管脚约束文件中,依据核心控制板与外围模块之间连接信号的电气特性,分别生成与电气特性对应的电路逻辑配置文件及管脚约束文件,其中,电气特性至少包含:单向传输数字信号、双向传输数字信号及模拟信号。

14.作为本发明线上硬件实验透明化配置方法,进一步地,核心控制板与外围模块之间为单向数字信号时,根据核心控制板、fpga开发板及外围模块之间的电压是否一致或兼容来生成电路逻辑配置文件及管脚约束文件,若三者之间的电压一致或兼容,则直接利用fpga开发板内部连线资源进行管脚连接并生成电路逻辑配置文件及管脚约束文件,若三者之间的电压不匹配,则在fpga开发板上设置用于电压匹配的电平转换芯片,再生成对应的电路逻辑配置文件及管脚约束文件。

15.作为本发明线上硬件实验透明化配置方法,进一步地,核心控制板与外围模块之间为双向数字信号或模拟信号时,将核心控制板信号与外围模块之间对应信号分别连接在多通道选择器两端,并将多通道选择器的配置信号连接在fpga开发板管脚上,并生成对应的电路逻辑配置文件及管脚约束文件。

16.作为本发明线上硬件实验透明化配置方法,进一步地,通过调用fpga开发工具对fpga 开发板进行自动化配置中,利用tcl脚本将目标电路逻辑配置文件及管脚约束文件添加至开发项目中,通过运行生成比特流文件,利用比特流文件对目标fpga开发板进行自动配置。

17.进一步地,本发明还提供一种线上硬件实验透明化配置系统,用于核心控制板与外围模块之间的系统配置,包含:多个用户端上位机,及与每个用户端上位机通过互联网建立远程连接关系的实验室配置服务器;其中,

18.用户端利用上位机生成核心控制板与外围模块之间连接关系,并将该连接关系上传至实验室中的配置服务器;

19.配置服务器依据核心控制板与外围模块之间连接关系生成连接关系表,并依据连

接关系表确定fpga开发板管脚使用情况来获取fpga开发板的电路逻辑配置文件及管脚约束文件;根据电路逻辑配置文件及管脚约束文件,通过调用fpga开发工具对fpga开发板进行自动化配置。

20.本发明的有益效果:

21.本发明利用上位机建立核心控制板和外围模块之间的连接关系,并将其上传至远程连接的实验室配置服务器,通过配置服务器自动生成基于硬件描述语言的fpga开发板电路逻辑配置文件及管脚约束文件,利用fpga开发板的内部资源实现核心控制板与外围模块的连接,即以fpga为桥梁来实现硬件灵活配置的目的,真正实现硬件远程实验配置,具有较好的应用前景。

附图说明:

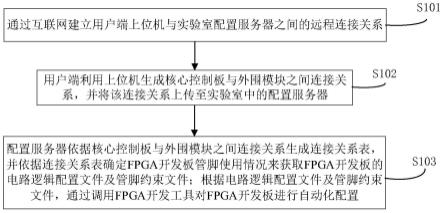

22.图1为实施例中线上硬件实验透明化配置流程示意;

23.图2为实施例中fpga开发板电路分类处理示意;

24.图3为实施例中线上硬件实验透明化配置工作原理示意。

具体实施方式:

25.为使本发明的目的、技术方案和优点更加清楚、明白,下面结合附图和技术方案对本发明作进一步详细的说明。

26.本发明实施例,参见图1所示,提供一种线上硬件实验透明化配置方法,用于核心控制板与外围模块之间的硬件配置,包含如下内容:

27.s101、通过互联网建立用户端上位机与实验室配置服务器之间的远程连接关系;

28.s102、用户端利用上位机生成核心控制板与外围模块之间连接关系,并将该连接关系上传至实验室中的配置服务器;

29.s103、配置服务器依据核心控制板与外围模块之间连接关系生成连接关系表,并依据连接关系表确定fpga开发板管脚使用情况来自动生成fpga开发板的电路逻辑配置文件及管脚约束文件;根据电路逻辑配置文件及管脚约束文件,通过调用fpga开发工具对fpga开发板进行自动化配置。

30.利用上位机建立核心控制板和外围模块之间的连接关系,并将其上传至远程连接的实验室配置服务器,通过配置服务器自动生成基于硬件描述语言的fpga开发板电路逻辑配置文件及管脚约束文件,利用fpga开发板的内部资源实现核心控制板与外围模块的连接,即以fpga 为桥梁来实现硬件灵活、高效、可靠配置的目的,真正实现硬件远程实验配置。

31.进一步地,本案实施例中,用户端依据实验需求,利用上位机软件建立核心控制板与外围模块之间的连接关系。进一步地,用户端利用上位机与配置服务器之间的通信传输协议将连接关系传输至配置服务器。配置服务器接收到连接关系之后,自动生成基于硬件描述语言的配置文件,通过自动化编译、布局布线、下载等操作,实现外围模块的自动化透明配置。

32.进一步地,本案实施例中,所述通信传输协议包含:核心控制板与外围模块之间的连线总数,若干核心控制板连线编号,及与每个核心控制板连线编号对应的外围模块连线

编号。

33.其中,上位机与配置服务器之间的通信传输协议可如下表所示:

34.np1s1p2s2......pnsn

35.其中,n表示核心控制板与传感器之间共有n对线相连;p1与s1表示核心控制板与传感器的第一对连线,pn与sn表示核心控制板与传感器的第n对连线;pn表示第n对连线中核心控制板的处理器管脚号、sn表示第n对连线中传感器的管脚编号。上位机与配置服务器按照该协议完成信息传输,配置服务器即可据此生成连接关系对应表。

36.进一步地,本案实施例中,依据连接关系表确定fpga开发板管脚使用情况,所确定的 fpga开发板管脚使用情况至少包含:输入输出类型、管脚之间的通联逻辑。根据核心控制板与传感器之间的连接对应表,结合核心控制板管脚、传感器管脚与fpga管脚的连接关系,就可以确定fpga管脚的使用情况(包括输入输出类型、管脚之间的通联逻辑等)。根据verilog 语言格式以及实际所需,在指定fpga上的输入输出引脚后,利用python脚本自动生成符合语法规范及目标功能的.v文件;根据所使用的fpga引脚以及管脚约束文件的特定格式,利用python脚本生成管脚约束文件(.xdc)。

37.本案实施例中,进一步地,获取fpga开发板的电路逻辑配置文件及管脚约束文件中,依据核心控制板与外围模块之间连接信号的电气特性,分别生成与电气特性对应的电路逻辑配置文件及管脚约束文件,其中,电气特性至少包含:单向传输数字信号、双向传输数字信号及模拟信号。

38.参见图2所示,鉴于核心控制板与外围模块之间的连接信号的电气特性存在一定差异, fpga开发板需根据核心控制板的信号、外围模块信号的特点进行设计,fpga的配置方法也要分类处理,以实现线上实现过程中核心控制板与外围模块的可靠连接。核心控制板与外围模块之间是单向传输的数字信号,如核心控制板输出、外围模块输入的数字信号或核心控制板输入、外围模块输出的数字信号。对于此类连接信号,如果核心控制板、fpga开发板、外围模块之间的驱动电压一致或兼容,直接用fpga内部连线资源实现相应管脚的连接即可;若核心控制板、fpga开发板、外围模块之间的驱动电压不匹配,在fpga开发板上加入相应的电平转换芯片即可。核心控制板与外围模块之间是双向传输的数字信号,fpga电路板将核心控制板的相关信号与外围模块之间的相关信号分别接在继电器的两端,继电器的使能信号接在 fpga的管脚上,通过fpga配置实现相关管脚的通联关系。核心控制板与外围模块之间是模拟信号。fpga电路板将核心控制板的相关信号与外围模块之间的相关信号分别接在多通道模拟选择器的两端,多通道模拟模拟选择器的配置信号接在fpga的管脚上,通过fpga配置实现相关管脚的通联关系。

39.进一步地,本案实施例中,通过调用fpga开发工具对fpga开发板进行自动化配置中,利用tcl脚本将目标电路逻辑配置文件及管脚约束文件添加至开发项目中,通过运行生成比特流文件,利用比特流文件对目标fpga开发板进行自动配置。

40.根据核心控制板与外围模块之间的连接对应表,可通过查找管脚对应文件(包括核心控制板管脚、外围模块管脚与fpga管脚的连接关系,以及外围模块的功能及其管脚特性),就可以确定fpga管脚的使用情况,包括输入输出类型、管脚之间的通联逻辑等。具体做法是:首先,根据外围模块的管脚号,确定相应的外围模块是什么模块,再根据已知外围模块的性质确定该管脚是单向传输的数字管脚(包括传输方向)、还是双向传输的数字管脚,

或者是模拟信号;然后,分别根据单向传输数字信号对应表、双向传输数字对应表、模拟信号对应表,确定fpga管脚。

41.例如,核心控制板与外围模块之间的连接对应表中核心控制板处理器管脚pn与外围模块的管脚sm相连,首先根据sm的编号确定其属于哪个外围模块,若该外围模块的这个管脚是单向数字信号,确定其是输入还是输出信号(皆是相对于处理器而言),然后从单向传输数字信号对应表中,确定sm与fpga的管脚gm相连,再确定与处理器管脚pn相连的fpga管脚是 fn。若是输入,在fpga配置中采用assign fn=gm,若是输出,在fpga配置中采用assign gm=fn,即可实现相应管脚的连接。

42.单向传输数字信号对应表

[0043][0044]

若外围模块的管脚是双向传输数字信号,则根据双向传输对应表确定与继电器使能端连接的fpga管脚号,如核心控制板与外围模块之间的连接对应表中核心控制板处理器管脚pn 与外围模块的管脚sn相连,且sn是双向信号,则根据双向传输数字信号对应表,只需在fpga 配置中使能信号en,即可实现pn和sn的连接。

[0045]

双向传输数字信号对应表

[0046][0047]

若外围模块的管脚是模拟信号,则根据双向传输对应表确定与多路模拟选择器使能端连接的fpga管脚号,如核心控制板与外围模块之间的连接对应表中核心控制板处理器管脚pn 与外围模块的管脚sn相连,且sn是模拟信号,则根据模拟信号对应表,只需在fpga配置中使能信号en,即可实现pn和sn的连接。

[0048]

模拟信号对应表

[0049][0050]

由于本案实施例中涉及的fpga逻辑主要有管脚连接和使能赋值两类,可以定制相应程序模板,对于不同的模块,只需要更改引脚或信号名称接口,很容易对硬件描述语言代

码进行复用。因此,在确定fpga连接或控制管脚后,根据verilog语言格式以及实际需要,即可利用python脚本自动生成符合语法规范及目标功能的.v文件;对于.xdc文件,其格式相对固定,只需要将硬件描述语言中使用到的引脚在.xdc文件中进行声明。可通过声明一个引脚的格式为:

[0051]

set_property package_pin+“fpga版上的引脚名称”+[get_ports+.v文件中使用的对应引脚名称]

[0052]

set_property iostandard lvcmos33[get_ports+.v文件中使用的对应引脚名称]

[0053]

根据所使用的fpga引脚以及管脚约束文件的特定格式,可利用python脚本自动生成管脚约束文件(.xdc)。

[0054]

在自动生成.v文件及.xdc文件的情况下,采用vivado提供的tcl(tool command language 工具命令语言)命令行自动对fpga进行配置,主要分为以下几步:

[0055]

(1)创建目标工程

[0056]

(2)添加目标.v及.xdc文件到目标工程

[0057]

(3)运行综合(synthesis)。

[0058]

(4)运行实现(implementation)。

[0059]

(5)生成比特流文件。

[0060]

(6)将比特流文件下载到目标开发板,对开发板进行编程配置。

[0061]

进一步地,基于上述的方法,本发明实施例还提供一种线上硬件实验透明化配置方法,用于核心控制板与外围模块之间的硬件配置,参见图3所示,包含:多个用户端上位机,及与每个用户端上位机通过互联网建立远程连接关系的实验室配置服务器;其中,

[0062]

用户端利用上位机生成核心控制板与外围模块之间连接关系,并将该连接关系上传至实验室中的配置服务器;

[0063]

配置服务器依据核心控制板与外围模块之间连接关系生成连接关系表,并依据连接关系表确定fpga开发板管脚使用情况来获取fpga开发板的电路逻辑配置文件及管脚约束文件;根据电路逻辑配置文件及管脚约束文件,通过调用fpga开发工具对fpga开发板进行自动化配置。

[0064]

除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对步骤、数字表达式和数值并不限制本发明的范围。

[0065]

最后应说明的是:以上所述实施例,仅为本发明的具体实施方式,用以说明本发明的技术方案,而非对其限制,本发明的保护范围并不局限于此,尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,其依然可以对前述实施例所记载的技术方案进行修改或可轻易想到变化,或者对其中部分技术特征进行等同替换,而这些修改、变化或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应所述以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1