一种高电源抑制比LDO电路及其应用的制作方法

本申请涉及电源管理芯片领域,特别涉及一种高电源抑制比ldo电路及其应用。

背景技术:

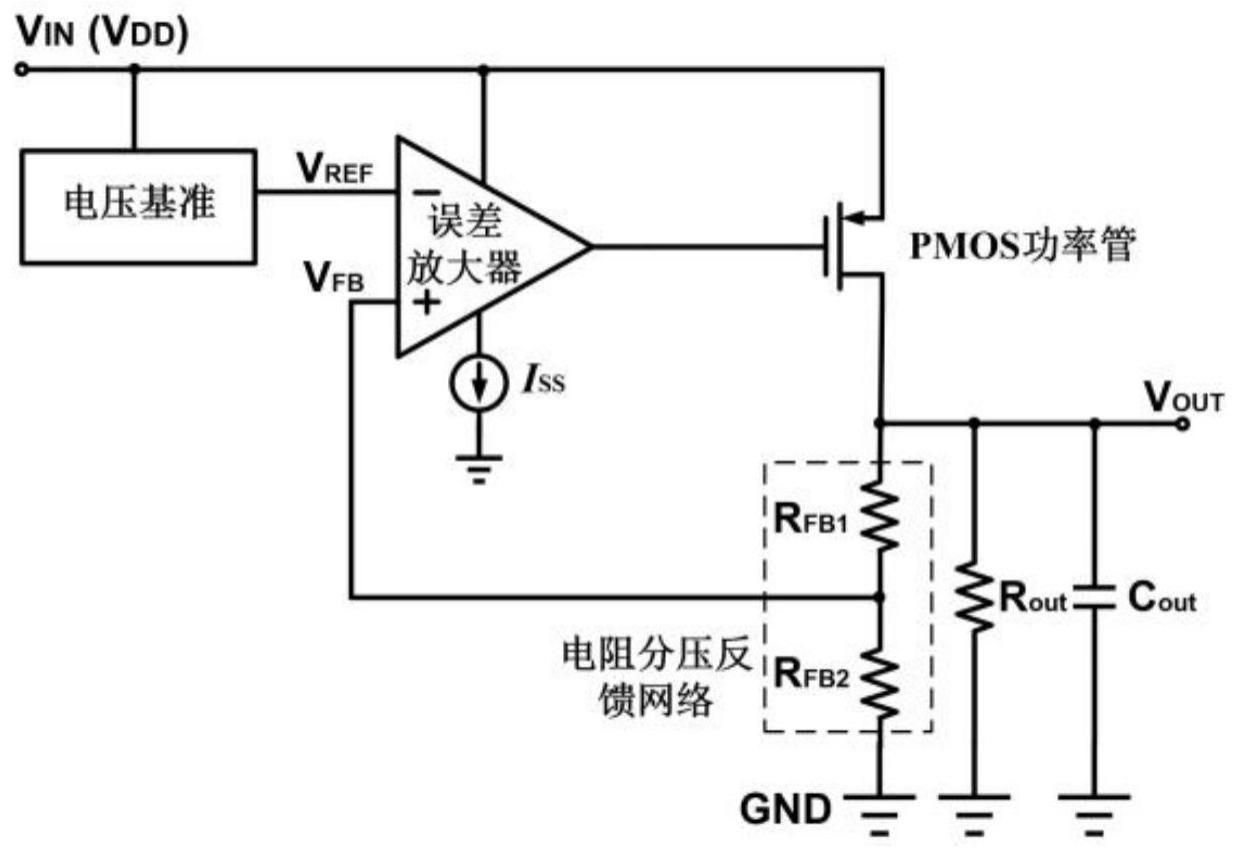

1、ldo是电源管理芯片中重要的一类,无片外电容型ldo凭借其易于集成、较好的线性调整率和负载调整率等优点,被广泛应用在模拟、射频和片上系统(system on chip,soc)等电路系统中。随着物联网电子设备的发展,高性能的soc对ldo的性能提出了更为苛刻的要求。物联网电子设备中的传感器模块要不断检测和收集物理环境中的数据,周围环境噪声和电源纹波会直接影响检测结果的准确性。然而,由于无片外电容型ldo在大负载时psrr(电源抑制比)较差的缺点,导致其越来越难满足物联网电子设备高性能的需求。

2、针对提高ldo的psrr,共源共栅阻性退化电路、基准噪声整形电路和自偏置低噪声隔离电路等电路技术被公开。如公告号为cn212569574u的中国专利公开了一种高压大驱动高电源抑制比ldo电路,包括噪声整形电路、共源共栅阻性退化电路和动态补偿电路。噪声整形电路和共源共栅阻性退化电路分别用于滤除基准噪声和减小误差放大器低频时热噪声,使到达pmos功率管栅极的噪声降低。然而,该发明未考虑电源噪声经pmos功率管的源漏等效电阻对ldo输出噪声的贡献,且该发明只针对于带片外电容型ldo,无法满足soc需要完全片内集成的需求。又如公开号为cn111399583a的中国专利公开了一种宽负载范围内高psrr的ldo电路,采用了在基准模块和误差放大器模块之间连接自偏置低噪声隔离电路的方法。自偏置低噪声隔离电路由nmos管和pmos管构成的源跟随结构组成,输入电压为基准电压vref,输出电压为低噪声电压va,再由va为误差放大器和pmos功率管提供电源电压,从而达到减小ldo输出噪声的目的。该发明有效地将电源噪声与ldo输出电压进行了隔离,但是自偏置低噪声隔离电路跨接在电源和pmos功率管源极之间,会因此增加ldo的漏失电压,从而导致ldo的效率降低、pmos功率管的功耗损耗增加。

3、以上技术虽然在一定程度上提高了ldo的psrr,但是具有不利于片上集成或以ldo漏失电压的损耗为代价的缺陷,亟待改进。

技术实现思路

1、本申请的目的是提供一种高电源抑制比ldo电路及其应用,旨在解决现有ldo电路大负载时低频psrr较差的问题。

2、为实现上述目的,本申请实施例采用以下技术方案:一种高电源抑制比ldo电路,包括:

3、预调压基准模块,所述预调压基准模块链接电源电压vdd,所述预调压基准模块包括预调压电路和基准核心电路,所述预调压电路产生一个对电源电压vdd的变化不敏感的电压vddx并输出给基准核心电路,所述基准核心电路产生并输出参考电压vref;

4、自适应误差放大器模块,所述自适应误差放大器模块包括误差放大器和自适应偏置电路,所述误差放大器的负输入端接入所述参考电压vref,所述误差放大器的尾电流由固定偏置电流源和自适应偏置电流源共同构成,所述自适应偏置电流源由所述自适应偏置电路产生;

5、pmos功率管,所述pmos功率管的栅极与所述误差放大器的输出端链接;

6、电阻反馈模块,所述电阻反馈模块产生反馈电压vfb并输出给所述误差放大器的正输入端。

7、在上述技术方案中,本申请实施例通过采用预调压电路产生vddx作为基准核心电路的电源电压,对基准核心电路的psrr进行了优化,使经误差放大器到达pmos功率管栅极的纹波降到最小。采用自适应偏置电路对误差放大器的尾电流进行调节,使其尾电流随ldo负载电流的增加而增加,使大负载时ldo的环路增益得到增强。通过以上两种技术的结合使用,可在不增加任何额外的无源器件和放大器的情况下,显著提高ldo环路低频时全负载范围内的psrr特性。

8、进一步地,根据本申请实施例,其中,所述预调压电路包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9,所述第一晶体管m1和第二晶体管m2栅极共连、源极接地,所述第三晶体管m3和第四晶体管m4栅极共连,所述第三晶体管m3和第四晶体管m4的源极分别与第一晶体管m1和第二晶体管m2的漏极相接组成电流镜,所述第五晶体管m5的漏极与所述第四晶体管m4的源极接相接,所述第五晶体管m5的栅极引入偏置电压vb;所述第六晶体管m6与第七晶体管m7栅极共连,电源电压vdd接入所述第六晶体管m6与第七晶体管m7的源极构成电流镜;所述第七晶体管m7的漏极和所述第五晶体管m5的源极连接,在连接处输出电压vddx;所述第九晶体管m9的源极连接电压vddx,所述第九晶体管m9的漏极与其栅极共连,并与第八晶体管m8的源极相接。

9、进一步地,根据本申请实施例,其中,所述自适应偏置电路包括:采样晶体管mps、第十晶体管m10和第十一晶体管m11;

10、所述采样晶体管mps的源极连接电源电压vdd,所述采样晶体管mps的栅极与所述误差放大器的输出端连接;

11、所述第十晶体管m10和第十一晶体管m11栅极共连,所述第十一晶体管m11的源极与其栅极共连,所述第十晶体管m10和第十一晶体管m11的源极接地构成电流镜;

12、采样晶体管mps的漏极与所述第十一晶体管m11漏级相接。

13、进一步地,根据本申请实施例,其中,所述自适应偏置电流随ldo负载电流成比例变化。

14、进一步地,根据本申请实施例,其中,所述预调压基准模块的psrr值为基准核心电路psrr值和预调压电路psrr值之和。

15、进一步地,根据本申请实施例,其中,在ldo空载时,由固定偏置电流源为所述误差放大器提供尾电流。

16、进一步地,根据本申请实施例,其中,在ldo带载时,由所述固定偏置电流源和所述自适应偏置电流源共同为所述误差放大器提供尾电流。

17、为了实现上述目的,本申请实施例还公开了一种高电源抑制比ldo电路在电源管理芯片上的应用。

18、与现有技术相比,本申请具有以下有益效果:本申请通过采用预调压电路产生vddx作为基准核心电路的电源电压,对基准核心电路的psrr进行了优化,使经误差放大器到达pmos功率管栅极的纹波降到最小。采用自适应偏置电路对误差放大器的尾电流进行调节,使其尾电流随ldo负载电流的增加而增加,进而使大负载时ldo的环路增益得到增强。通过以上两种技术的结合使用,可在不增加任何额外的无源器件和放大器的情况下,显著提高ldo环路低频时全负载范围内的psrr特性。

技术特征:

1.一种高电源抑制比ldo电路,其特征在于,包括:

2.根据权利要求1所述的一种高电源抑制比ldo电路,其特征在于,所述预调压电路包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9,所述第一晶体管m1和第二晶体管m2栅极共连、源极接地,所述第三晶体管m3和第四晶体管m4栅极共连,所述第三晶体管m3和第四晶体管m4的源极分别与第一晶体管m1和第二晶体管m2的漏极相接组成电流镜,所述第五晶体管m5的漏极与所述第四晶体管m4的源极接相接,所述第五晶体管m5的栅极引入偏置电压vb;所述第六晶体管m6与第七晶体管m7栅极共连,电源电压vdd接入所述第六晶体管m6与第七晶体管m7的源极构成电流镜;所述第七晶体管m7的漏极和所述第五晶体管m5的源极连接,并输出电压vddx;所述第九晶体管m9的源极连接电压vddx,所述第九晶体管m9的漏极与其栅极共连,并与第八晶体管m8的源极相接。

3.根据权利要求1所述的一种高电源抑制比ldo电路,其特征在于,所述自适应偏置电路包括:采样晶体管mps、第十晶体管m10和第十一晶体管m11;

4.根据权利要求1所述的一种高电源抑制比ldo电路,其特征在于,所述自适应偏置电流随ldo负载电流成比例变化。

5.根据权利要求1所述的一种高电源抑制比ldo电路,其特征在于,所述预调压基准模块的psrr值为基准核心电路psrr值和预调压电路psrr值之和。

6.根据权利要求1所述的一种高电源抑制比ldo电路,其特征在于,在ldo空载时,由所述固定偏置电流源为所述误差放大器提供尾电流。

7.根据权利要求1所述的一种一种高电源抑制比ldo电路,其特征在于,在ldo带载时,由所述固定偏置电流源和所述自适应偏置电流源共同为所述误差放大器提供尾电流。

8.一种如权利要求1-7中的任一项所述的高电源抑制比ldo电路在电源管理芯片上的应用。

技术总结

本申请公开了一种高电源抑制比LDO电路及其应用,涉及电源管理芯片领域。本申请采用预调压电路产生V<subgt;DDX</subgt;作为基准核心电路的电源电压,对基准核心电路的PSRR进行了优化,使经误差放大器到达PMOS功率管栅极的纹波降到最小。采用自适应偏置电路对误差放大器的尾电流进行调节,使其尾电流随LDO负载电流的增加而增加,使大负载时LDO的环路增益得到增强。通过以上两种技术的结合使用,可在不增加任何额外的无源器件和放大器的情况下,显著提高LDO环路低频时全负载范围内的PSRR特性。

技术研发人员:刘世军,余国义,汪涛,彭新

受保护的技术使用者:苏州喻芯半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!