一种具有宽分辨率SSI接口型绝对值编码器数据采集器

本发明涉及ssi接口型绝对值编码器采集,具体涉及一种具有宽分辨率ssi接口型绝对值编码器数据采集器。

背景技术:

1、在常见的伺服运动控制系统中,用于测量角度的传感器件应用广泛,ssi接口型绝对值编码器经常被用于运动器件角度的测量。ssi接口型绝对值编码器的数据通信只需两路差分信号“时钟和数据”的串行方式来传输,具有安装成本少,线路简单的优点。

2、本申请的发明人经过研究发现,不同厂家生产的ssi接口型绝对值编码器分辨率不一致,目前大多数ssi接口型绝对值编码器数据的读取需要采用专用集成芯片,或者采用cpld(complex programmable logic device,复杂可编程逻辑器件)或fpga(fieldprogrammable gate array,现场可编程门阵列)来实现,但这样较难灵活的匹配不同的ssi接口型绝对值编码器。因此亟需设计一种通用的ssi接口型绝对值编码器数据采集器,来实现宽分辨率的ssi接口型绝对值编码器数据的采集。

技术实现思路

1、针对现有不同厂家生产的ssi接口型绝对值编码器分辨率不一致,目前大多数ssi接口型绝对值编码器数据的读取需要采用专用集成芯片,或者采用cpld或fpga来实现,但这样较难灵活的匹配不同的ssi接口型绝对值编码器的技术问题,本发明提供一种具有宽分辨率ssi接口型绝对值编码器数据采集器。

2、为了解决上述技术问题,本发明采用了如下的技术方案:

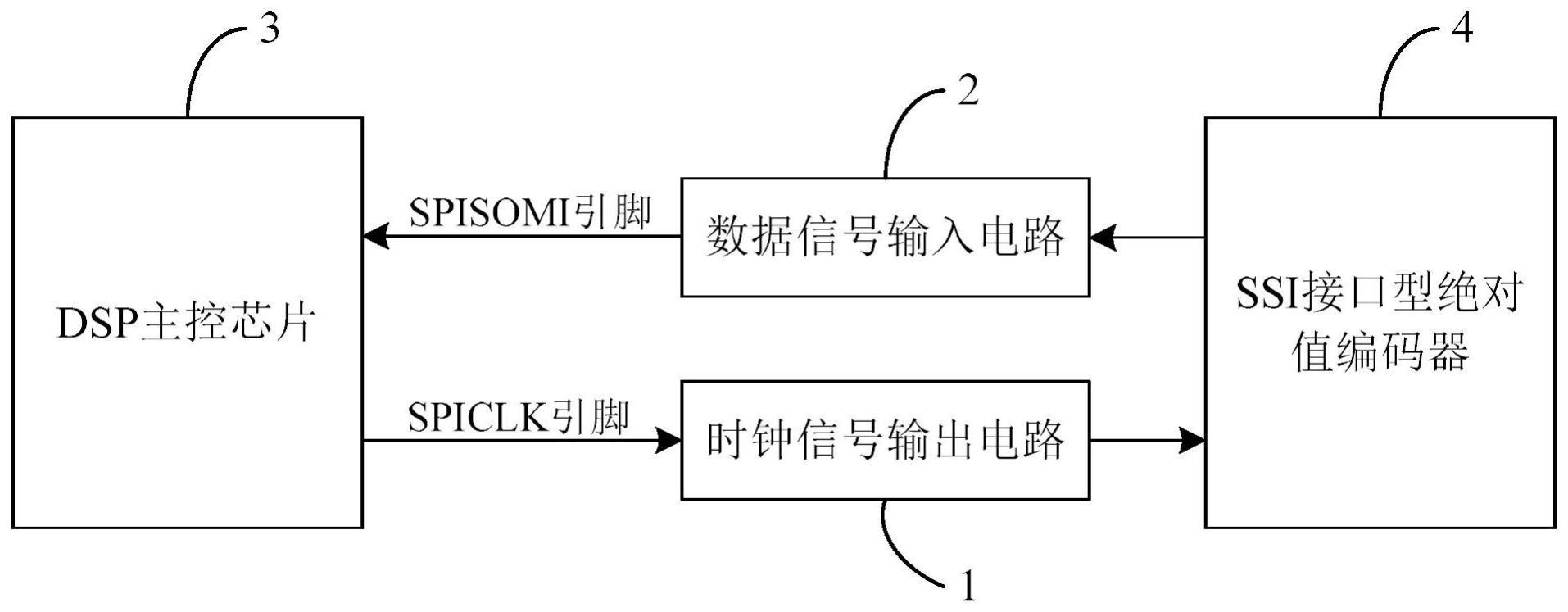

3、一种具有宽分辨率ssi接口型绝对值编码器数据采集器,包括时钟信号输出电路、数据信号输入电路和dsp主控芯片;其中,

4、所述时钟信号输出电路适于与所述dsp主控芯片和ssi接口型绝对值编码器连接,所述时钟信号输出电路用于将dsp主控芯片spiclk引脚发送的时钟信号转换为ssi接口型绝对值编码器所需要的差分电平信号,以驱动所述ssi接口型绝对值编码器进行角度数据的传输;

5、所述数据信号输入电路适于与所述dsp主控芯片和ssi接口型绝对值编码器连接,所述数据信号输入电路用于接收所述ssi接口型绝对值编码器表示角度物理量的数据差分信号并转换为适配dsp主控芯片的ttl电平信号;

6、所述dsp主控芯片控制spiclk引脚的高低电平生成时钟信号,以达到宽量程数据传递适配1~24位分辨率的ssi接口型绝对值编码器的数据采集,所述dsp主控芯片还通过spisomi引脚获取经过所述数据信号输入电路转换后的ttl电平信号。

7、进一步,所述时钟信号输出电路包括电平转换电路、输出端滤波电路和输出端阻抗匹配电阻,所述电平转换电路的输入端与dsp主控芯片的spiclk引脚连接,所述电平转换电路用于将dsp主控芯片spiclk引脚发送的时钟信号转换为ssi接口型绝对值编码器所需要的差分电平信号后,顺序经过所述输出端滤波电路和输出端阻抗匹配电阻输出至ssi接口型绝对值编码器。

8、进一步,所述电平转换电路包括电平转换芯片及电平转换外围电路,所述电平转换芯片选用型号为sn65hvd78dr的芯片,所述电平转换外围电路包括电阻r168、电阻r170和电容c267,所述电阻r168、电阻r170、电容c267的一端及电平转换芯片的第八引脚均与3.3v电源连接,所述电阻r168的另一端与电平转换芯片的第一、第二和第三引脚同时连接,所述电阻r170的另一端与电平转换芯片的第一引脚及dsp主控芯片的spiclk引脚连接,所述电容c267的另一端及电平转换芯片的第五引脚均接地,所述电平转换芯的第六和第七引脚分别与输出端滤波电路连接。

9、进一步,所述输出端滤波电路包括滤波电阻r169和r174、滤波电容c266和c269及限流电阻r172,所述滤波电阻r169的一端与电平转换芯片的第一输出端连接,所述滤波电阻r174的一端与电平转换芯片的第二输出端连接,所述滤波电容c266和c269的一端接地,所述滤波电阻r169和滤波电容c266的另一端与限流电阻r172的一端连接,所述滤波电阻r174和滤波电容c269的另一端与限流电阻r172的另一端连接,所述限流电阻r172的两端还分别与输出端阻抗匹配电阻的两端连接并作为与ssi接口型绝对值编码器相连接的clk+单元接口和clk-单元接口。

10、进一步,所述数据信号输入电路包括输入端阻抗匹配电阻r163和r165、高速光耦、输入端限流电阻r162和r167、双路反相器,所述输入端阻抗匹配电阻r163的一端与ssi接口型绝对值编码器数据差分信号的一路输入端和输入端限流电阻r162的一端连接,所述输入端限流电阻r162的另一端经电容c263接地,所述输入端阻抗匹配电阻r165的一端与ssi接口型绝对值编码器数据差分信号的另一路输入端和输入端限流电阻r167的一端连接,所述输入端限流电阻r167的另一端经电容c265接地,所述输入端阻抗匹配电阻r163和r165的另一端分别与高速光耦的两个输入端和电阻r164的两端连接,所述高速光耦的输出端与双路反相器的输入端连接,所述双路反相器的输出端与dsp主控芯片的spisomi引脚连接。

11、进一步,所述dsp主控芯片选用型号为tms320f28035的芯片,所述dsp主控芯片内部新增有时钟信号生成控制模块,所述时钟信号生成控制模块用于控制时钟信号生成的方法流程为:先让所述dsp主控芯片的spiclk引脚在空闲状态时内保持高电平,持续保持时间为第一时间;接着降低spiclk引脚电平,降低持续时间为第二时间;然后拉高spiclk引脚电平,拉高持续时间为第三时间;重复降低和拉高所述spiclk引脚的高低电平,即可生成时钟信号;其中,所述第二时间和第三时间相等且远小于所述第一时间。

12、与现有技术相比,本发明提供的具有宽分辨率ssi接口型绝对值编码器数据采集器中,时钟信号输出电路生成ssi接口型绝对值编码器所需要的时钟信号,并将其转换为ssi接口型绝对值编码器所需要的差分电平信号,ssi接口型绝对值编码器在识别到时钟信号的每个上升沿时对角度数据进行传输,数据信号输入电路接收ssi接口型绝对值编码器表示角度物理量的数据差分信号并转换为适配dsp主控芯片的正常逻辑的ttl电平信号。本发明中时钟信号输出电路生成的时钟信号可以达到宽量程数据传递适配1~24位分辨率的ssi接口型绝对值编码器的数据采集,具有宽分辨率、容错能力强、低成本等优点,因而可以灵活匹配不同的ssi接口型绝对值编码器。

技术特征:

1.一种具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,包括时钟信号输出电路、数据信号输入电路和dsp主控芯片;其中,

2.根据权利要求1所述的具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,所述时钟信号输出电路包括电平转换电路、输出端滤波电路和输出端阻抗匹配电阻,所述电平转换电路的输入端与dsp主控芯片的spiclk引脚连接,所述电平转换电路用于将dsp主控芯片spiclk引脚发送的时钟信号转换为ssi接口型绝对值编码器所需要的差分电平信号后,顺序经过所述输出端滤波电路和输出端阻抗匹配电阻输出至ssi接口型绝对值编码器。

3.根据权利要求2所述的具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,所述电平转换电路包括电平转换芯片及电平转换外围电路,所述电平转换芯片选用型号为sn65hvd78dr的芯片,所述电平转换外围电路包括电阻r168、电阻r170和电容c267,所述电阻r168、电阻r170、电容c267的一端及电平转换芯片的第八引脚均与3.3v电源连接,所述电阻r168的另一端与电平转换芯片的第一、第二和第三引脚同时连接,所述电阻r170的另一端与电平转换芯片的第一引脚及dsp主控芯片的spiclk引脚连接,所述电容c267的另一端及电平转换芯片的第五引脚均接地,所述电平转换芯的第六和第七引脚分别与输出端滤波电路连接。

4.根据权利要求3所述的具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,所述输出端滤波电路包括滤波电阻r169和r174、滤波电容c266和c269及限流电阻r172,所述滤波电阻r169的一端与电平转换芯片的第一输出端连接,所述滤波电阻r174的一端与电平转换芯片的第二输出端连接,所述滤波电容c266和c269的一端接地,所述滤波电阻r169和滤波电容c266的另一端与限流电阻r172的一端连接,所述滤波电阻r174和滤波电容c269的另一端与限流电阻r172的另一端连接,所述限流电阻r172的两端还分别与输出端阻抗匹配电阻的两端连接并作为与ssi接口型绝对值编码器相连接的clk+单元接口和clk-单元接口。

5.根据权利要求1所述的具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,所述数据信号输入电路包括输入端阻抗匹配电阻r163和r165、高速光耦、输入端限流电阻r162和r167、双路反相器,所述输入端阻抗匹配电阻r163的一端与ssi接口型绝对值编码器数据差分信号的一路输入端和输入端限流电阻r162的一端连接,所述输入端限流电阻r162的另一端经电容c263接地,所述输入端阻抗匹配电阻r165的一端与ssi接口型绝对值编码器数据差分信号的另一路输入端和输入端限流电阻r167的一端连接,所述输入端限流电阻r167的另一端经电容c265接地,所述输入端阻抗匹配电阻r163和r165的另一端分别与高速光耦的两个输入端和电阻r164的两端连接,所述高速光耦的输出端与双路反相器的输入端连接,所述双路反相器的输出端与dsp主控芯片的spisomi引脚连接。

6.根据权利要求1所述的具有宽分辨率ssi接口型绝对值编码器数据采集器,其特征在于,所述dsp主控芯片选用型号为tms320f28035的芯片,所述dsp主控芯片内部新增有时钟信号生成控制模块,所述时钟信号生成控制模块用于控制时钟信号生成的方法流程为:先让所述dsp主控芯片的spiclk引脚在空闲状态时内保持高电平,持续保持时间为第一时间;接着降低spiclk引脚电平,降低持续时间为第二时间;然后拉高spiclk引脚电平,拉高持续时间为第三时间;重复降低和拉高所述spiclk引脚的高低电平,即可生成时钟信号;其中,所述第二时间和第三时间相等且远小于所述第一时间。

技术总结

本发明提供一种具有宽分辨率SSI接口型绝对值编码器数据采集器,包括时钟信号输出电路、数据信号输入电路和DSP主控芯片,时钟信号输出电路适于与DSP主控芯片和SSI接口型绝对值编码器连接,用于将DSP主控芯片SPICLK引脚发送的时钟信号转换为SSI接口型绝对值编码器所需要的差分电平信号,数据信号输入电路适于与DSP主控芯片和SSI接口型绝对值编码器连接,用于接收SSI接口型绝对值编码器表示角度物理量的数据差分信号并转换为适配DSP主控芯片的TTL电平信号,DSP主控芯片控制SPICLK引脚的高低电平生成时钟信号及通过SPISOMI引脚获取经过数据信号输入电路转换后的TTL电平信号。本申请能适配1~24位分辨率的SSI接口型绝对值编码器数据采集,具有宽分辨率、容错能力强、低成本等优点。

技术研发人员:欧阳奇,余代宇

受保护的技术使用者:重庆大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!