一种限压电路、带隙基准电路和芯片的制作方法

本技术涉及集成电路技术,应用于电学领域,尤其涉及一种限压电路、带隙基准电路和芯片。

背景技术:

1、带隙基准电路可以为芯片提供不随温度变化(即零温度系数)和工艺偏差影响的参考电压,是集成电路设计中基础且不可或缺的电路结构。传统的带隙基准电路通常由电源vcc直接供电,电路中流经各支路的电流信号以及输出的基准电压信号易受到电源噪声的影响,因此,传统的带隙基准电路对电源噪声的抑制能力较差(即电路的电源抑制比较低),电路稳定性不高。

技术实现思路

1、本技术实施例公开了一种限压电路、带隙基准电路和芯片,用于增强对电源噪声的抑制能力,从而提高电路的稳定性。

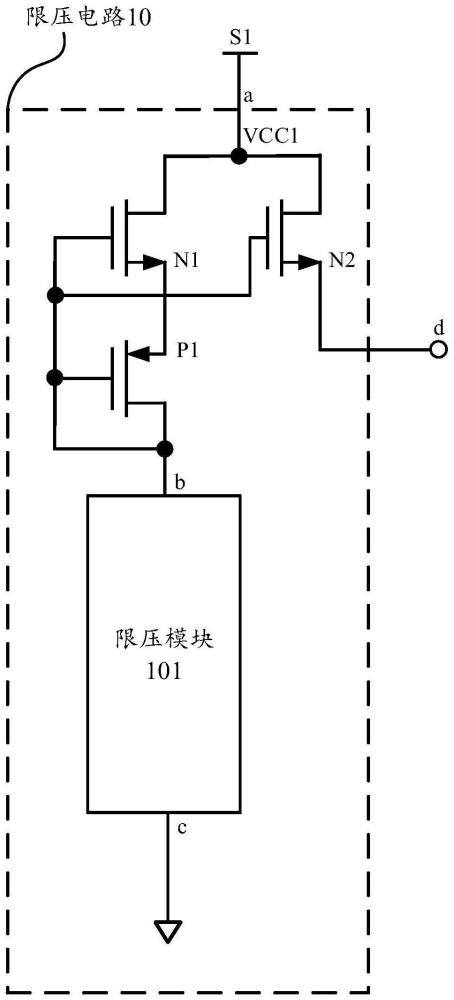

2、第一方面,本技术实施例提供了一种限压电路,限压电路包括第一nmos管n1、第二nmos管n2、第一pmos管p1和限压模块101,其中,限压电路的输入端连接第一nmos管n1的漏极和第二nmos管n2的漏极,第一nmos管n1的栅极连接第二nmos管n2的栅极、第一pmos管p1的栅极、第一pmos管p1的漏极和限压模块101的第一端,限压模块101的第二端连接参考地,第二nmos管n2的源极连接限压电路的输出端,限压模块101的第一端的电压值和第二端的电压值之间的电压差值由流经第一nmos管n1的电流信号的电流值决定。

3、上述限压电路中,第一nmos管n1和第一pmos管p1的物理尺寸确定时,流经第一nmos管n1的电流信号的电流值随之确定,限压电路的输出电压则也随之确定,不受到限压电路10的输入电压的噪声影响,对电源噪声的抑制能力较强,电路的稳定性较高。此外,上述限压电路还可以通过调整第一nmos管n1和第一pmos管p1的物理尺寸,将流经各支路的电流信号的电流值控制在na级别,以减小电路功耗。

4、结合第一方面,在一种可能的实现方式中,限压模块101包括n个pmos管,n个pmos管包括第二pmos管p2,其中,n个pmos管串联在限压模块101的第一端和限压模块101的第二端之间,限压模块101的第一端连接第一个pmos管的源极,第n个pmos管的漏极连接限压模块101的第二端,第二pmos管p2的栅极连接第二pmos管p2的漏极,n为大于零的正整数。

5、上述限压电路的限压模块101中,每个pmos管均可看作一个二极管。当流经第一nmos管n1的电流信号的电流值确定时,每个pmos管的源极电压值和栅极电压值间的电压差值(即每个pmos管的压降)随之确定。由于限压模块101两端的电压差等于n个pmos管的压降之和,限压模块101两端的电压差则也随之确定。此外,pmos管的个数可以根据实际应用中对限压电路的输出电压需求灵活调整,因此,上述限压电路的结构多样,灵活性高。

6、结合第一方面,或者第一方面的上述任一种可能的实现方式,在另一种可能的实现方式中,限压模块101包括n个二极管,n个二极管串联在限压模块101的第一端和限压模块101的第二端之间,限压模块101的第一端连接第一个二极管的正极,第n个二极管的负极连接限压模块101的第二端,n为大于零的正整数。

7、上述限压电路的限压模块101中,当流经第一nmos管n1的电流信号的电流值确定时,每个二极管的压降随之确定。由于限压模块101两端的电压差等于n个二极管的压降之和,限压模块101两端的电压差则也随之确定。此外,二极管的个数可以根据实际应用中对限压电路的输出电压需求灵活调整,因此,上述限压电路的结构多样,灵活性高。

8、第二方面,本技术实施例提供了一种带隙基准电路,带隙基准电路包括第一方面或第一方面任一种可能的实施方式所描述的限压电路、启动电路501、电流产生电路502和电压输出电路503,带隙基准电路的输入端连接限压电路的输入端,带隙基准电路的输出端连接电压输出电路503的输出端,其中,限压电路用于向启动电路501、电流产生电路502和电压输出电路503输出第一电压信号;启动电路501用于基于第一电压信号使电流产生电路502产生第一电流信号id_n,第一电流信号id_n为正温度系数电流信号;电压输出电路503用于基于第一电流信号id_n输出第一基准电压信号,第一基准电压信号为零温度系数电压信号。

9、上述带隙基准电路中的启动电路501、电流产生电路502和电压输出电路503不由第三电源s3直接供电,而是由限压电路输出的电压信号供电。限压电路中的第一nmos管n1和第一pmos管p1的物理尺寸确定时,流经第一nmos管n1的电流信号的电流值随之确定,限压电路的输出电压则也随之确定。因此,上述带隙基准电路对电源噪声的抑制能力强,电路稳定性高。

10、结合第二方面,在一种可能的实现方式中,限压电路的输入端连接启动电路501的输入端和电流产生电路502的输入端,其中,在电流产生电路502产生第一电流信号id_n的情况下,启动电路501中无电流信号流经。

11、上述带隙基准电路中,启动电路501在带隙基准电路建立工作点后,静态功耗为零,有利于降低带隙基准电路的功耗。

12、结合第二方面,或者第二方面的上述任一种可能的实现方式,在另一种可能的实现方式中,启动电路501包括第三nmos管n3、第四nmos管n4、第五nmos管n5和第一电容c1,电流产生电路502包括第六pmos管p6、第七pmos管p7、第八pmos管p8、第九pmos管p9、第十pmos管p10、第六nmos管n6、第七nmos管n7、第八nmos管n8、第九nmos管n9和第一电阻r1,其中,启动电路501的输入端通过第一电容c1连接第三nmos管n3的漏极、第四nmos管n4的栅极和第五nmos管n5的栅极,第三nmos管n3的源极,第四nmos管n4的源极和第五nmos管n5的源极均连接参考地,第三nmos管n3的栅极连接第六nmos管n6的栅极、第七nmos管n7的栅极和第九nmos管n9的栅极,第四nmos管n4的漏极连接第六pmos管p6的栅极和第七pmos管p7的栅极,第五nmos管n5的漏极连接第八pmos管p8的栅极、第九pmos管p9的栅极和第十pmos管p10的栅极。电流产生电路502的输入端连接第六pmos管p6的源极和第七pmos管p7的源极,第六pmos管p6、第八pmos管p8和第六nmos管n6串联在电流产生电路502的输入端和参考地之间,第七pmos管p7、第九pmos管p9、第八nmos管n8、第七nmos管n7和第一电阻r1串联在参考地之间,第七nmos管n7的栅极连接第九nmos管n9的漏极,第十pmos管p10的栅极连接第十pmos管p10的漏极,第七nmos管n7的漏极电压值等于第六nmos管n6的漏极电压值。

13、上述带隙基准电路中,启动电路501通过电容耦合的方式向电流产生电路502和电压输出电路503提供启动电流,避免电流产生电路502和电压输出电路503在第三电源s3上电过程中保持死锁状态(即无支路电流),从而避免带隙基准电路不能建立静态工作点。并且,带隙基准电路在建立静态工作点后,启动电路501的功耗为零,且限压电路10和电流产生电路502的支路电流均可控制在na级别,有利于降低带隙基准电路的功耗。

14、结合第二方面,或者第二方面的上述任一种可能的实现方式,在又一种可能的实现方式中,限压电路的输入端连接电压输出电路503的输入端,流经电压输出电路503的第二电流信号的电流值与第一电流信号id_n的电流值成正比。

15、上述带隙基准电路中,电压输出电路503可以复制第一电流信号id_n,电压输出电路503的支路电流则可控制在na级别,有利于进一步降低带隙基准电路的功耗。

16、结合第二方面,或者第二方面的上述任一种可能的实现方式,在又一种可能的实现方式中,电压输出电路503包括第十一pmos管p11、第十二pmos管p12、第二电阻r2和第一三极管q1,其中,电压输出电路503的输入端连接第十一pmos管p11的源极,电压输出电路503的输出端连接第十二pmos管p12的漏极和第二电阻r2的一端,第十一pmos管p11、第十二pmos管p12、第二电阻r2和第一三极管q1串联在电压输出电路503的输入端和参考地之间,第一三极管q1的基极连接第一三极管q1的集电极和参考地,第十一pmos管p11的栅极连接第七pmos管p7的栅极,第十二pmos管p12的栅极连接第十pmos管p10的栅极。

17、第三方面,本技术实施例提供了一种芯片,该芯片包括第一方面或第一方面任一种可能的实施方式所描述的限压电路,或者包括第二方面或第二方面任一种可能的实施方式所描述的带隙基准电路。

18、本技术第三方面所提供的芯片,其有益效果可以参考第一方面技术方案或者第二方面技术方案的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!