一种基于FPGA和V93000测试机的预测试平台的制作方法

一种基于fpga和v93000测试机的预测试平台

技术领域

[0001]

本发明涉及芯片测试技术领域,特别涉及一种基于fpga和v93000测试机的预测试平台。

背景技术:

[0002]

随着集成电路的飞速发展,片上集成系统soc得到了越来越广泛的应用。而在soc电路的整个设计过程中,测试环节难度大、耗时长、费用高。测试时间少则一个月,多则数月,费用可占到芯片制造成本的50%以上。芯片的开发周期中测试环节将会有越来越大的影响,是制约soc实际应用的一个关键因素。

[0003]

普通的芯片测试流程是在芯片开发的最后阶段对芯片进行ate测试程序开发及芯片验证,耗时长。特别是一些高速端口的ate测试程序开发,常常需要耗时几个月,增加了芯片的整体开发周期。

技术实现要素:

[0004]

本发明的目的在于提供一种基于fpga和v93000测试机的预测试平台,以实现在soc芯片设计阶段进行测试程序开发及芯片验证。

[0005]

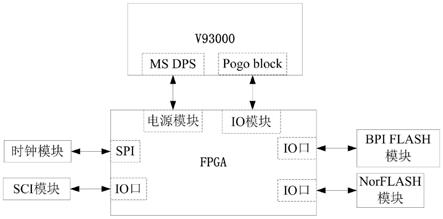

为解决上述技术问题,本发明提供了一种基于fpga和v93000测试机的预测试平台,包括fpga和v93000测试机,所述v93000测试机通过ms dps板卡与所述fpga的电源模块连接,为所述fpga及外围电路供电,所述v93000测试机通过pogo block模组与所述fpga的io模块进行通道直连;所述预测试平台还包括bpi flash模块、norflash模块、时钟模块和sci模块;其中,所述bpi flash模块与所述fpga直连,用于存储soc芯片的网表文件;所述norflash模块通过电压转换后与所述fpga进行连接,用于存储soc芯片程序运行文件;所述fpga通过spi端口对所述时钟模块进行配置;所述sci模块实现所述fpga对串口读写的控制,与其他外设互联进行数据传输。

[0006]

可选的,所述bpi flash模块所用芯片为mt28gu01gaaa1egc。

[0007]

可选的,所述norflash模块采用1gb容量的s29gl01gp芯片,通过两片电平转换芯片gtl2000dl进行电压转换,将所述s29gl01gp芯片与所述fpga进行连接。

[0008]

可选的,所述时钟模块所用的时钟管理芯片为ad9518-4abcpz,其参考时钟由晶振或外部sma接口提供。

[0009]

可选的,所述fpga的通道通过电压转换芯片txs0108e与芯片ad9518-4abcpz的spi端口连接,所述fpga通过spi接口完成对所述芯片ad9518-4abcpz的配置,所述芯片ad9518-4abcpz输出的时钟供所述fpga使用。

[0010]

可选的,所述sci模块所用芯片为max3232e。

[0011]

可选的,所示fpga的io接口通过电压转换芯片txs0108e与芯片max3232e的uart端口连接,实现fpga对串口读写的控制,与其他外设互联进行数据传输。

[0012]

可选的,所述电源模块中各电源vccint_fpga、mgtavcc_fpga、vcc1v8_fpga、mgtaux_fpga、mgtavtt_fpga、vcc3v3通过ms dps板卡的15路电源dps11、dps12、dps13、dps21、dps22、dps25、dps26、dps31、dps32、dps35、dps36、dps81、dps82、dps85、dps86进行供电,满足所需电压及电流。

[0013]

可选的,所述fpga的io模块通过pogo block模组的数字通道101-124和225-232连接所述v93000测试机。

[0014]

可选的,所述bpi flash模块、所述norflash模块、所述时钟模块、所述sci模块、所述电源模块和所述io模块均集中在同一块电路板上。

[0015]

可选的,所述fpga的型号为xcvu440-flga2892-1-c。

[0016]

在本发明提供的基于fpga和v93000测试机的预测试平台,具有很高的兼容性,不同芯片无需重复开发设计制板,均可用本平台进行预测试。在芯片设计阶段将soc芯片的asic代码转换为rtl代码,运行于fpga原型验证系统,然后将此fpga原型验证系统应用于v93000测试机,,即可进行测试程序开发及调试;取代了以往的在芯片开发的最后阶段其进行测试,而是在芯片设计阶段通过fpga原型验证系统来进行测试程序开发及调试,来保证芯片设计的可靠性和正确性,大大缩短了芯片整体开发周期,节省设计经费,在soc芯片设计阶段本平台具有较高的使用率。

附图说明

[0017]

图1为本发明提供的一种基于fpga和v93000测试机的预测试平台的构架图;图2为bpi flash模块的原理图;图3为norflash模块的原理图;图4为时钟模块的原理图;图5为sci模块的原理图;图6为电源模块的原理图;图7为io模块的原理图。

具体实施方式

[0018]

以下结合附图和具体实施例对本发明提出的一种基于fpga和v93000测试机的预测试平台作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0019]

实施例一本发明提供了一种基于fpga和v93000测试机的预测试平台,其架构如图1所示,包括fpga和v93000测试机,所述v93000测试机通过ms dps板卡与所述fpga的电源模块连接,为所述fpga及外围电路供电,所述v93000测试机通过pogo block模组与所述fpga的io模块进行通道直连。所述预测试平台还包括bpi flash模块、norflash模块、时钟模块和sci模块。

[0020]

如图2所示,所述bpi flash模块所用芯片为mt28gu01gaaa1egc,其1.8v电平信号与fpga直连,用于存储soc电路的网表文件。

[0021]

图3是所述norflash模块的原理图,采用1gb容量的s29gl01gp芯片。fpga的1.8v电

平信号经过两片电平转换芯片gtl2000dl转为3.3v后与所述s29gl01gp芯片进行连接,用于存储soc芯片程序运行文件。

[0022]

图4是时钟模块的原理图,所用的时钟管理芯片为ad9518-4abcpz,其参考时钟由晶振或外部sma接口提供。fpga的1.8v电平信号经过电平转换芯片txs0108e转为3.3v后与时钟管理芯片ad9518-4abcpz进行连接,所述fpga通过spi接口完成对时钟管理芯片ad9518-4abcpz的配置,时钟管理芯片ad9518-4abcpz输出的时钟供fpga使用。

[0023]

图5是sci模块的原理图,所用芯片为max3232e。fpga的1.8v电平信号经过电平转换芯片txs0108e转为3.3v后与芯片max3232e的uart端口相连,实现fpga对串口读写的控制,与其他外设互联进行数据传输。

[0024]

图6是电源模块的原理图,预测试平台所需的电源vccint_fpga、mgtavcc_fpga、vcc1v8_fpga、mgtaux_fpga、mgtavtt_fpga、vcc3v3通过ms dps板卡的15路电源dps11、dps12、dps13、dps21、dps22、dps25、dps26、dps31、dps32、dps35、dps36、dps81、dps82、dps85、dps86进行供电,满足所需电压及电流。

[0025]

图7是io接口模块的原理图,通过v93000测试机上101-124、225-232等pogo block的数字通道连接v93000测试机和fpga,进行数据传输。

[0026]

所述bpi flash模块、所述norflash模块、所述时钟模块、所述sci模块、所述电源模块和所述io模块均集中在同一块电路板上。所述fpga型号为xcvu440-flga2892-1-c。本发明将soc芯片模拟运行于fpga原型验证系统上,在芯片设计阶段通过测试机对fpga原型验证系统进行测试程序开发及调试,来保证芯片设计的可靠性和正确性,大大缩短了芯片整体开发周期,节省了设计经费。

[0027]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1